Chipscope教程:从RTL设计到逻辑分析仪生成

需积分: 10 146 浏览量

更新于2024-08-02

收藏 437KB PDF 举报

"Chipscope 简明教程 - stevechou@21cn.com - www.edaking.com"

Chipscope 是一款由Xilinx公司提供的内置逻辑分析工具,用于在FPGA(现场可编程门阵列)设计中进行硬件调试。本教程主要介绍了如何在特定的操作环境下使用Chipscope进行RTL设计的仿真与逻辑分析仪的产生。

首先,教程假设用户已经安装了必要的软件,包括仿真工具Modelsim5.8,综合工具Synplifypro7.5.1,布局布线工具ISE6.2,以及分析工具Chipscope6.2。这些工具是完成FPGA设计流程所必需的,它们分别负责不同的任务,如Modelsim用于行为仿真,Synplifypro进行逻辑优化,ISE管理整个设计流程,而Chipscope则提供硬件级别的调试功能。

在RTL(寄存器传输级)设计阶段,用户通常会编写Verilog或VHDL代码,并创建一个测试平台(testbench)来验证设计的功能。教程中提到的rtl/lfsr.v是RTL源代码,而rtl/lfsr_tb.v是对应的测试平台,它们的仿真波形可以用来检查设计是否按预期工作。

当设计完成后,需要生成逻辑分析仪来监控内部信号。Chipscope 提供了两种方法来实现这一点:CoreGenerator 和 CoreInserter。CoreInserter 直接在已综合的网表中插入逻辑分析仪,而CoreGenerator则是在设计阶段就将逻辑分析仪的逻辑整合到用户的RTL代码中。由于CoreInserter需要对网表进行操作,可能更复杂且每次修改RTL都需要重新插入,因此教程选择了使用CoreGenerator,因为它允许在修改设计后只需重新进行综合、布局和布线即可。

生成Chipscope逻辑分析仪的步骤如下:

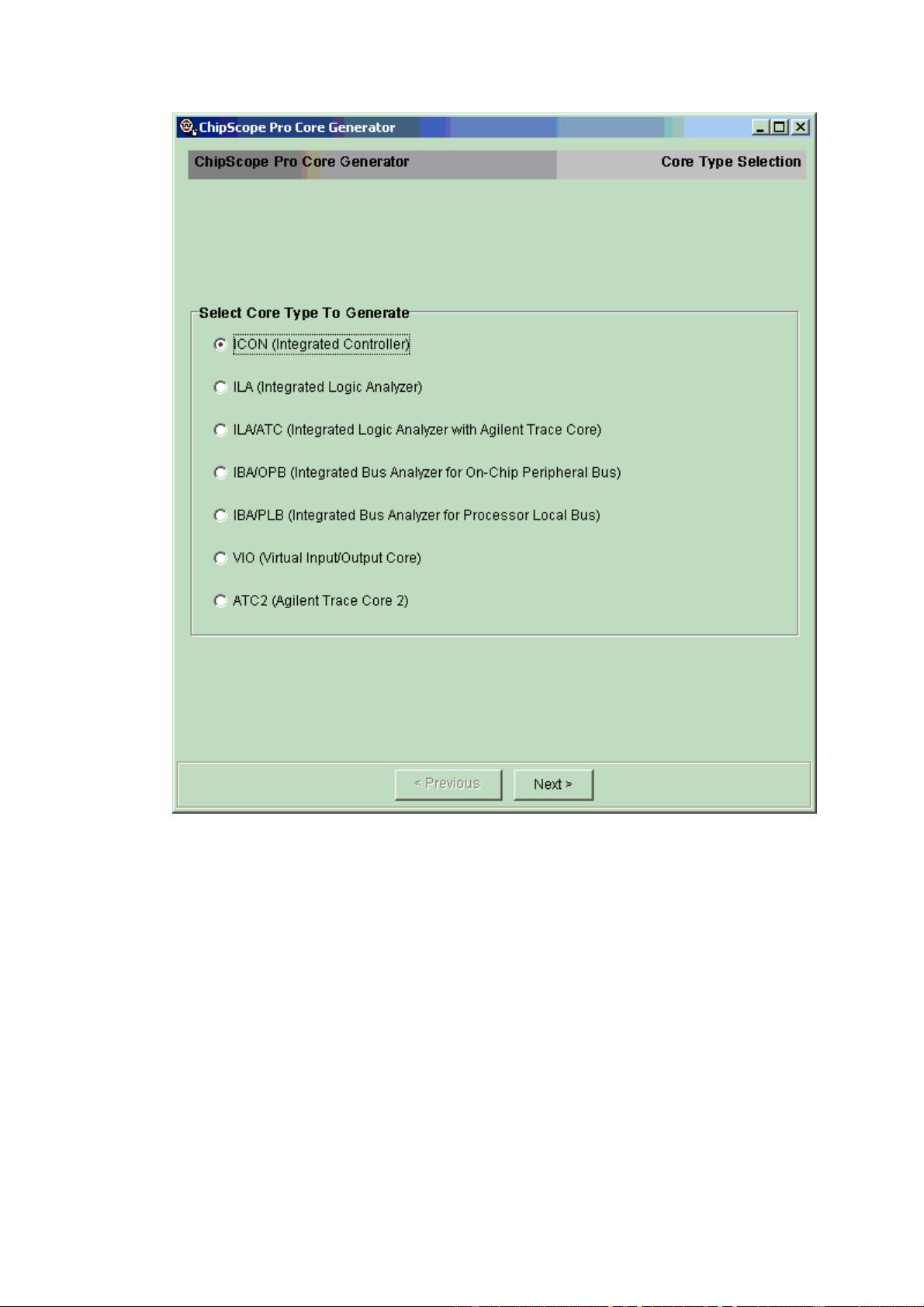

1. 通过启动菜单打开ChipScope Pro CoreGenerator。

2. 选择所需的图标(集成控制器)并设置输出目录和设备家族。

3. 指定设计的语言(Verilog或VHDL)和综合工具。

4. 生成集成控制器的Netlist。

5. 回到主菜单,选择ILA(集成逻辑分析仪)。

6. 设置输出目录、设备家族和触发时钟边缘。

7. 设置触发宽度(例如32位)和数据深度。

8. 选择“DataSameAsTrigger”,使得数据端口和触发端口相同,并根据需要选择采样深度,注意不要超过FPGA的BlockRAM资源限制。

9. 选择语言和综合工具,再次生成集成Core。

完成以上步骤后,用户可以得到一个包含逻辑分析仪的Bit文件,将其下载到FPGA中,然后通过Chipscope界面观察和分析设计中的内部信号,从而进行精确的硬件调试。这种方法对于理解和优化复杂的FPGA设计至关重要,因为它提供了对设计底层行为的深入洞察。

2009-08-19 上传

2009-09-01 上传

点击了解资源详情

点击了解资源详情

2009-11-11 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

swain168

- 粉丝: 1

- 资源: 7

最新资源

- ES管理利器:ES Head工具详解

- Layui前端UI框架压缩包:轻量级的Web界面构建利器

- WPF 字体布局问题解决方法与应用案例

- 响应式网页布局教程:CSS实现全平台适配

- Windows平台Elasticsearch 8.10.2版发布

- ICEY开源小程序:定时显示极限值提醒

- MATLAB条形图绘制指南:从入门到进阶技巧全解析

- WPF实现任务管理器进程分组逻辑教程解析

- C#编程实现显卡硬件信息的获取方法

- 前端世界核心-HTML+CSS+JS团队服务网页模板开发

- 精选SQL面试题大汇总

- Nacos Server 1.2.1在Linux系统的安装包介绍

- 易语言MySQL支持库3.0#0版全新升级与使用指南

- 快乐足球响应式网页模板:前端开发全技能秘籍

- OpenEuler4.19内核发布:国产操作系统的里程碑

- Boyue Zheng的LeetCode Python解答集