Cortex-M3内核深度解析:中断、存储器与异常处理

“Cortex-M3内核详解,包含中断控制、复位、时钟等内容的中文详细解析。”

Cortex-M3是ARM公司设计的一种高效能、低功耗的微控制器核心,广泛应用于嵌入式系统。它采用了RISC(精简指令集计算)架构,以实现更快的执行速度和更低的功耗。以下是对Cortex-M3内核各方面的详细解释:

1. **中断控制**:Cortex-M3内核包含了一个嵌套向量中断控制器(NVIC),能够处理多个同时发生的中断事件,并按照优先级进行管理。NVIC支持中断优先级分组,允许开发者灵活调整中断处理的顺序。

2. **复位**:在Cortex-M3中,复位是一个重要的异常处理过程。复位后,处理器会从预定义的向量表中获取第一条指令地址,执行初始化序列。复位机制确保了系统在遇到错误或启动时能正确恢复到已知状态。

3. **时钟**:Cortex-M3的时钟系统通常由外部晶振或内部RC振荡器提供,通过时钟分频器和倍频器调节CPU时钟频率。时钟管理是关键,因为它直接影响处理器性能和功耗。

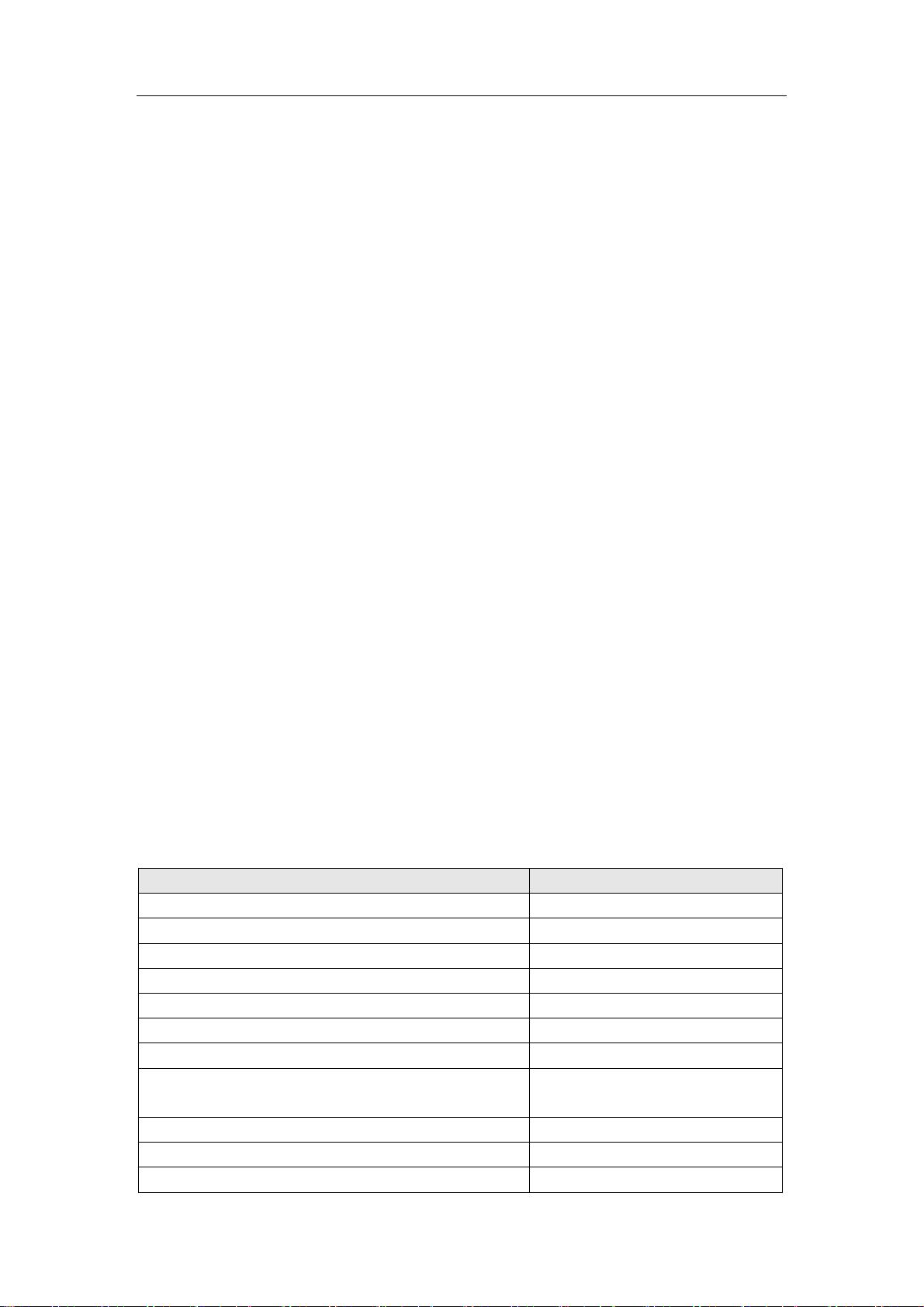

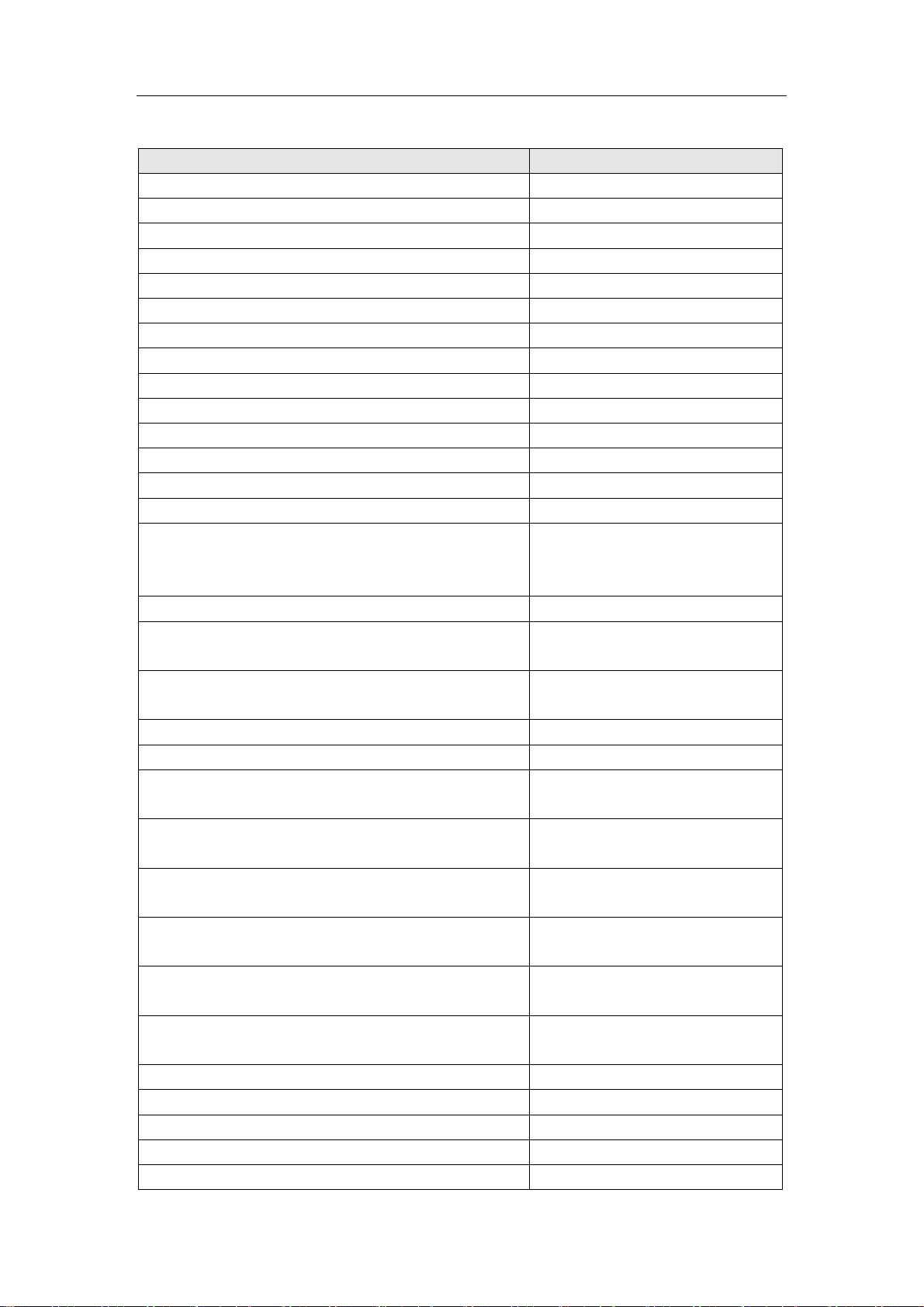

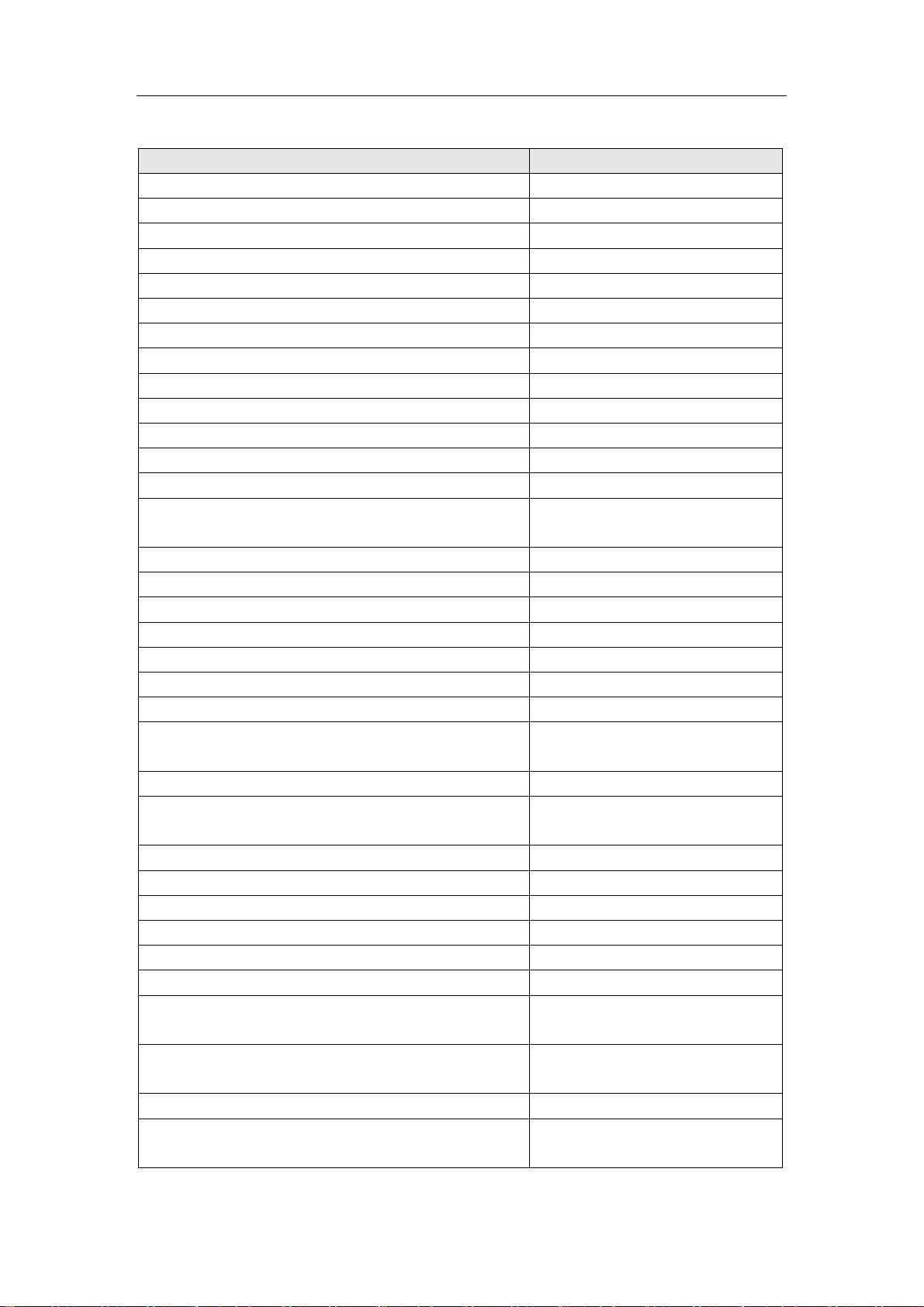

4. **处理器组件**:

- **处理器内核**:Cortex-M3的核心,执行指令和算术逻辑操作。

- **NVIC**:管理中断,包括中断向量管理和优先级管理。

- **总线矩阵**:负责片上外设与内存之间的数据传输。

- **FPB**:快速断点单元,用于设置硬件断点,方便调试。

- **DWT**:数据 watchpoint and trace unit,提供运行时性能监控功能。

- **ITM**:Instrumentation Trace Macrocell,用于调试输出。

- **MPU**:内存保护单元,确保对内存区域的访问权限控制。

- **ETM**:嵌入式跟踪宏单元,提供指令级追踪信息。

- **TPIU**:Trace Port Interface Unit,连接到调试接口,帮助收集追踪数据。

- **SW/JTAG-DP**:软件/联合测试访问端口,用于调试接口。

5. **编程模型**:包括工作模式(如线程模式和中断模式)、工作状态(如Thumb和Thumb-2状态)、特权访问和用户访问权限、寄存器布局(如通用寄存器和程序状态寄存器xPSR)、数据类型、存储器格式和指令集。

6. **系统控制**:涵盖处理器寄存器,如NVIC、调试接口寄存器、MPU寄存器等,这些寄存器用于配置和监控系统行为。

7. **存储器映射**:包括存储器的组织结构、位带操作(Bit-banding)以直接访问特定位,以及ROM存储器表,帮助理解内存分配和访问。

8. **异常模型**:涉及各种异常类型(如中断、系统调用等),异常优先级,特权和堆栈处理,以及异常的进入和退出流程,包括末尾连锁、迟来异常和复位处理。

以上内容构成了Cortex-M3内核的基础知识框架,深入理解这些概念对于开发基于Cortex-M3的嵌入式系统至关重要。开发者可以利用这些特性来优化中断响应、调试代码、管理存储资源以及实现高效能、低功耗的设计。

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

jc8507

- 粉丝: 0

- 资源: 10

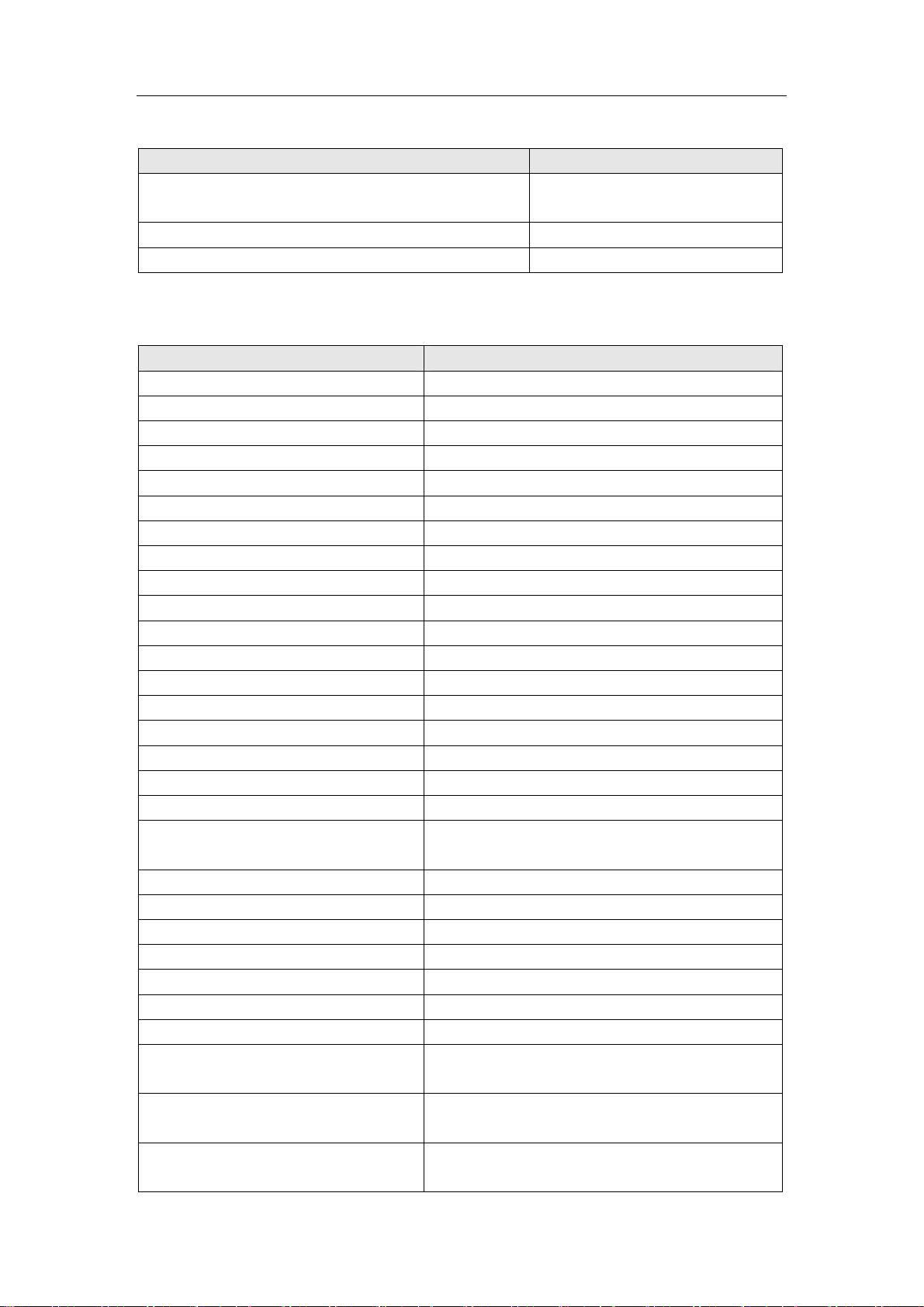

最新资源

- 计算机一级考试机试试题

- DDS芯片AD9850的工作原理及其与单片机的接口

- Beginning Web Development Silverlight and ASP.NET AJAX - From Novice to Professional

- 详细的jsp分页程序!(oracle+jsp+apache)

- 新一代人机交互中的二维图像AVR 重建

- Protel99教程.doc

- C# 命名空间编译单元命名空间声明

- The Unified Modeling Language Reference Manual

- C程序设计 学生成绩管理系统

- VC客户/服务通信编程(ServerSocket詳解).pdf

- 跟我一起写Makefile.txt

- linux vim 使用手册

- JavaScript语言精髓与编程实践

- java文件操作大全.txt

- 如何画状态图pdf格式

- [翻译版]FPGA设计经验谈.pdf