Quartus II中静态时序分析详解与模型

需积分: 18 45 浏览量

更新于2024-07-24

收藏 2.04MB PDF 举报

静态时序分析是数字电路设计过程中至关重要的一步,它确保电路能够在预定的时间约束下正确工作。本文将着重介绍在Quartus II软件中进行时序分析的基本原理和相关模型,Quartus II是Altera公司出品的一款广泛应用于FPGA和CPLD设计的工具。

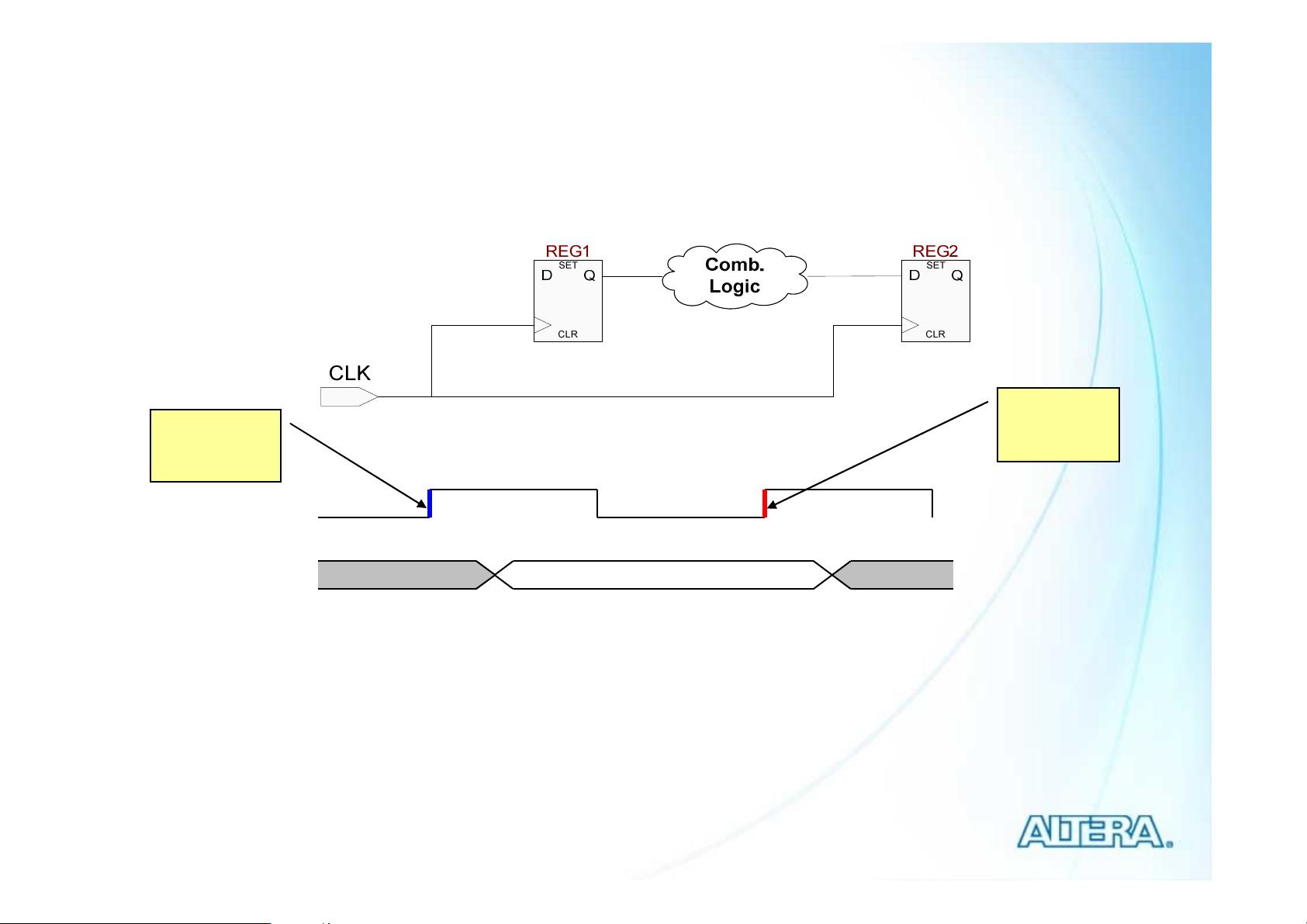

首先,时序分析的目标是全面理解设计中的定时特性,确保所有路径符合预设的时序规范和要求。这包括在早期阶段就检测出可能导致性能问题或不满足功能的延迟错误,相较于门级模拟和板级测试,静态时序分析能更快速、高效地发现这些问题。设计者需要明确输入(如CLK)到输出(如D、Q等)信号之间的预期延迟,以及如预置(PRE)、清除(CLR)等控制信号对组合逻辑延迟的影响。

在Quartus II中,时序分析涉及以下关键步骤:

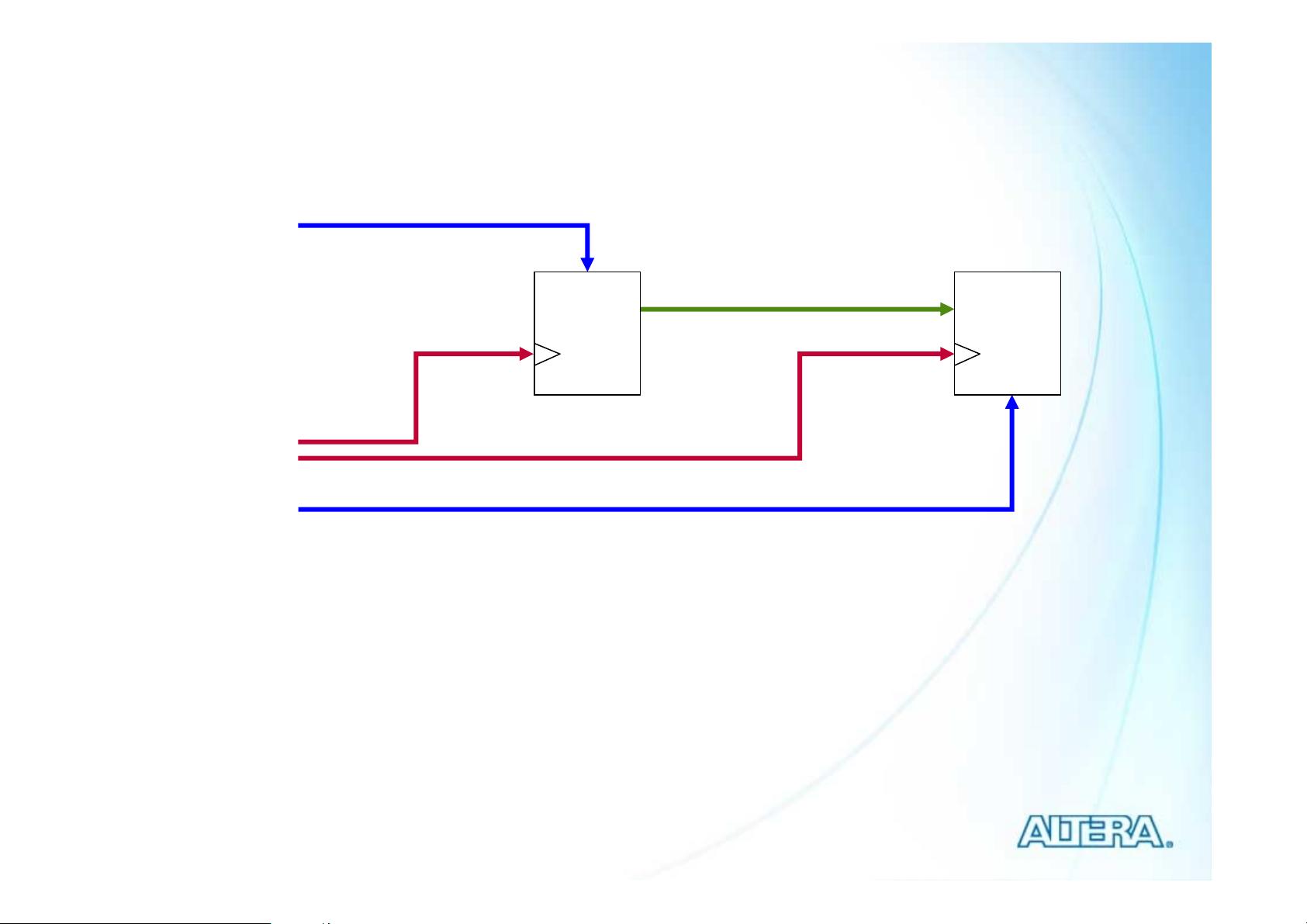

1. **设备路径分析**:设计中的每一个逻辑路径,无论是数据路径还是控制路径,都需要通过时序分析工具进行全面检查,以确定是否存在任何可能违反时序的行为。这包括计算每个逻辑门、触发器和其他组件的延迟,以及考虑它们之间的相互作用。

2. **设置时序要求**:设计者需要输入和管理时序约束,如最大延时、最小延时和容差等,这些约束会指导布局布线算法(placement and routing),以优化电路性能。

3. **指导布局和路由**:时序分析结果被用于指导FPGA的自动布局和布线过程,以确保电路结构能够在实际物理实现中满足时序要求。

4. **与实际结果对比**:静态时序分析不仅用于预测,还会与最终的布局和布线后的真实时序数据进行比较,验证设计是否达到预期。如果出现不符,可能需要调整设计或优化布线策略。

5. **识别关键路径**:在时序分析中,关键路径是指决定整个电路最短延时期限的那条路径。理解并优化关键路径对于减少电路的功耗和实现高速度至关重要。

6. **异常处理**:时序分析也会显示潜在的异常情况,如路径过长、缓冲需求不足或寄存器转移延迟等,设计师需要针对这些异常情况采取措施,比如添加适当数量的缓冲器或者重新配置设计结构。

静态时序分析在FPGA和CPLD设计中扮演着核心角色,它通过提供准确的路径延迟信息,帮助设计师确保电路的性能、可靠性和一致性,从而提高整体设计质量和生产效率。在Quartus II这样的高级设计工具中,这一过程自动化且精确,是现代集成电路设计不可或缺的一部分。

2010-06-05 上传

2021-10-15 上传

2021-09-29 上传

2011-04-11 上传

2015-09-08 上传

2019-02-27 上传

2022-09-24 上传

2018-03-15 上传

robkiller

- 粉丝: 0

- 资源: 1

最新资源

- C语言数组操作:高度检查器编程实践

- 基于Swift开发的嘉定单车LBS iOS应用项目解析

- 钗头凤声乐表演的二度创作分析报告

- 分布式数据库特训营全套教程资料

- JavaScript开发者Robert Bindar的博客平台

- MATLAB投影寻踪代码教程及文件解压缩指南

- HTML5拖放实现的RPSLS游戏教程

- HT://Dig引擎接口,Ampoliros开源模块应用

- 全面探测服务器性能与PHP环境的iprober PHP探针v0.024

- 新版提醒应用v2:基于MongoDB的数据存储

- 《我的世界》东方大陆1.12.2材质包深度体验

- Hypercore Promisifier: JavaScript中的回调转换为Promise包装器

- 探索开源项目Artifice:Slyme脚本与技巧游戏

- Matlab机器人学习代码解析与笔记分享

- 查尔默斯大学计算物理作业HP2解析

- GitHub问题管理新工具:GIRA-crx插件介绍