没有合适的资源?快使用搜索试试~ 我知道了~

首页IEEE Journal of Solid-State Circuits: 2020 February Issue Overview

IEEE Journal of Solid-State Circuits: 2020 February Issue Overvi...

需积分: 12 5 下载量 160 浏览量

更新于2024-07-15

收藏 125.04MB PDF 举报

"这篇文档是IEEE Journal of Solid-State Circuits (JSSC) 2020年2月刊的部分内容,涵盖了多个关于固态电路设计的研究论文,重点关注晶体管级的集成电路设计。"

在【标题】"JSSC_202002"中,我们可以理解这是IEEE固体状态电路期刊2020年2月的一期,这是一本专注于固态电路特别是集成电路晶体管级设计的专业学术出版物。

【描述】进一步强调了该期刊的范围,它每个月发布关于广义固态电路领域的论文,特别关注集成电路上的晶体管级别设计。这通常包括模拟、数字、混合信号电路,以及相关的技术,如电源管理、射频(RF)电路、传感器接口、微控制器单元等。

在【标签】"jssc"中,这代表了与IEEE Journal of Solid-State Circuits相关的主题或讨论。

在【部分内容】中,我们看到几篇论文的摘要,涵盖了不同领域的创新技术:

1. "A6.5–8.1-GHz Communication/Ranging VWB Transceiver for Secure Wireless Connectivity With Enhanced Bandwidth Efficiency and Energy Detection":这篇论文描述了一个6.5到8.1 GHz的超宽带(UWB)通信/测距收发器,旨在提高无线连接的安全性和带宽效率,并增强能量检测能力。这可能涉及新型的调制和检测技术,以及能效优化的电路设计。

2. "ACMOS 76–81-GHz 2-TX3-RX FMCW Radar Transceiver Based on Mixed-Mode PLL Chirp Generator":这篇论文介绍了一种基于混合模式锁相环(PLL)的76到81 GHz频段的双发射三接收FMCW雷达收发器。这种收发器利用了新颖的PLL技术来生成连续频率调制波,适用于高分辨率雷达应用。

3. "A Batteryless Padless Crystalless 116μm×116μm ‘Dielet’ Near-Field Radio With On-Chip Coil Antenna":这篇研究展示了一个无电池、无垫片、无晶体的116μm×116μm近场无线电,其包含片上线圈天线。这项技术可能涉及到能量收集和无线传输,用于物联网(IoT)设备等低功耗应用。

4. "A Reconfigurable Spectrum-Compressing Receiver for Non-Contiguous Carrier Aggregation in CMOS SOI":文章提到了一种可重构的频谱压缩接收器,用于非连续载波聚合(Carrier Aggregation)在CMOS绝缘体上硅(SOI)技术中的应用。这是5G通信系统中的关键技术,旨在提高频谱利用率和数据传输速率。

5. 其他论文涉及高线性度功率混频器、270-GHz基本频率发射机、事件驱动的准电平交叉ΔΣ调制器以及12位ADC的设计,这些都展示了在固态电路设计中的最新进展和创新。

这个文件提供了2020年2月JSSC中关于先进固态电路设计的最新研究成果,涵盖了无线通信、雷达技术、低功耗设计等多个关键领域,对于了解和研究当前集成电路技术的发展具有重要意义。

RHEE et al.: 0.3 lx–1.4 Mlx MONOLITHIC SILICON NANOWIRE LDC WITH TEMPERATURE-INDEPENDENT OFFSET CANCELLATION 391

[8] S. Sengupta, H. Ouh, and M. L. Johnston, “An all-digital CMOS ambient

light sensor using a single photon avalanche diode,” in Proc. IEEE

Sensors, Oct./Nov. 2017, pp. 1–3.

[9] H. Ouh and M. L. Johnston, “Dual-mode, in-pixel linear and single-

photon avalanche diode readout for low-light dynamic range extension

in photodetector arrays,” in Proc. IEEE Custom Integr. Circuits Conf.

(CICC), Apr. 2018, pp. 1–4.

[10] B. Shen, S. Bose, and M. L. Johnston, “A 1.2 V–20 V closed-loop charge

pump for high dynamic range photodetector array biasing,” IEEE Trans.

Circuits Syst., II, Exp. Briefs, vol. 66, no. 3, pp. 327–331, Mar. 2018.

[11] C. Soci, A. Zhang, X.-Y. Bao, H. Kim, Y. Lo, and D. Wang, “Nanowire

photodetectors,” J . Nanosci. Nanotechnol., vol. 10, no. 3, pp. 1430–1449,

Mar. 2010.

[12] J.-S. Yoon, K. Kim, M. Meyyappan, and C.-K. Baek, “Optical charac-

teristics of silicon-based asymmetric vertical nanowire photodetectors,”

IEEE Trans. Electron Devices, vol. 64, no. 5, pp. 2261–2266, May 2017.

[13] K.-N. Lee et al., “Fabrication of silicon nanowire for biosensor appli-

cations,” in Proc. IEEE Sensors, Oct. 2006, pp. 1269–1271.

[14] A. Zhang, Y. Liu, and Y. H. Lo, “Characterization and physics of

top-down silicon nanowire phototransistors,” Proc. SPIE, vol. 7608,

Art. no. 76018D1, Jan. 2010.

[15] K.-N. Lee, S.-W. Jung, K.-S. Shin, W.-H. Kim, M.-H. Lee, and

W.-K. Seong, “Fabrication of suspended silicon nanowire arrays,” Small,

vol. 4, no. 5, pp. 642–648, May 2008.

[16] J. Shin, K. Pi, S. Jung, and D.-I. D. Cho, “Silicon-nanowire field-effect

transistors on a flexible substrate using top-down MEMS processes,” in

Proc. MEMS, Jan. 2016, pp. 469–472.

[17] A. Zhang, H. Kim, J. Cheng, and Y. H. Lo, “Ultrahigh responsivity

visible and infrared detection using silicon nanowire phototransistors,”

Nano Lett., vol. 10, no. 6, pp. 2117–2120, Jun. 2010.

[18] M. N. Khiarak, S. Martel, Y. D. Koninck, and B. Gosselin, “A high-

sensitivity CMOS biophotometry sensor with embedded continuous-

time modulation,” in Pr oc. IEEE Int. Symp. Cir cuits Syst. (ISCAS),

May 2017, pp. 1–4.

[19] R. Yun and V. M. Joyner, “A monolithically integrated phase-sensitive

optical sensor for frequency-domain NIR spectroscopy,” IEEE Sensors

J., vol. 10, no. 7, pp. 1234–1242, Jul. 2010.

[20] W. Ahmad, M. Abdulaziz, M. Törmänen, and H. Sjöland, “CMOS

adaptive TIA with embedded single-ended to differential conversion for

analog optical links,” in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS),

May 2015, pp. 658–661.

[21] M. N. Khiarak et al., “A wireless fiber photometry system based

on a high-precision CMOS biosensor with embedded continuous-time

modulation,” IEEE Trans. Biomed. Circuits Syst., vol. 12, no. 3,

pp. 495–509, Jun. 2018.

[22] M. N. Khiarak et al., “An energy-efficient CMOS biophotometry sensor

with incremental DT- ADC conversion,” in Proc. IEEE Int. Symp.

Circuits Syst. (ISCAS), May 2018, pp. 1–4.

[23] M. Lemkin and B. Boser, “A three-axis micromachined accelerometer

with a CMOS position-sense interface and digital offset-trim electron-

ics,” IEEE J. Solid-State Circuits, vol. 34, no. 4, pp. 456–468, Apr. 1999.

[24] R. Hogervorst, J. P. Tero, R. G. H. Eschauzier, and J. H. Huijsing,

“A compact power-efficient 3 V CMOS rail-to-rail input/output opera-

tional amplifier for VLSI cell libraries,” IEEE J. Solid-State Circ uits,

vol. 29, no. 12, pp. 1505–1513, Dec. 1994.

[25] R. Wu, K. A. A. Makinwa, and J. H. Huisjing, “A chopper current-

feedback instrumentation amplifier with a 1 mHz 1/f noise corner and an

AC-coupled ripple reduction loop,” IEEE J. Solid-State Circuits, vol. 44,

no. 12, pp. 3232–3243, Dec. 2009.

[26] M. A. T. Sanduleanu, A. J. M. Van Tuijl, R. F. Wassenaar,

M. C. Lammers, and H. Wallinga, “A low noise, low residual offset,

chopped amplifier for mixed level applications,” in Proc. IEEE Int. Conf.

Electron., Circuits Syst. Surfing Waves Sci. Technol., vol. 2, Sep. 1998,

pp. 333–336.

[27] R. Wu, Y. Chae, J. H. Huijsing, and K. A. A. Makinwa, “A 20-b

± 40-mV range read-out IC with 50-nV offset and 0.04% gain error

for bridge transducers,” IEEE J. Solid-State Circuits, vol. 47, no. 9,

pp. 2152–2163, Sep. 2012.

[28] J. Markus, J. Silva, and G. C. Temes, “Theory and applications of

incremental converters,” IEEE Trans. Circuits Syst. I, Reg. Papers,

vol. 51, no. 4, pp. 678–690, Apr. 2004.

[29] J. Jun, C. Rhee, S. Kim, and S. Kim, “An SC interface with

programmable-gain embedded ADC for monolithic three-axis 3-D

stacked capacitive MEMS accelerometer,” IEEE Sensors J., vol. 17,

no. 17, pp. 5558–5568, Sep. 2017.

[30] J. Silva, U. Moon, J. Steensgaard, and G. C. Temes, “Wideband low-

distortion delta-sigma ADC topology,” Electron. Lett., vol. 37, no. 12,

pp. 737–738, Jun. 2001.

[31] C. C. Enz and G. C. Temes, “Circuit techniques for reducing the effects

of op-amp imperfections: Autozeroing, correlated double sampling, and

chopper stabilization,” Proc. IEEE, vol. 84, no. 11, pp. 1584–1614,

Nov. 1996.

[32] B. E. A. Saleh and M. C. Teich, Fundamentals of Photonics, 2nd ed.

Hoboken, NJ, USA: Wiley, 2007.

[33] C.-T. Chiang, “Design of CMOS monolithic digitized light transducer

with calibration technique for ambient light sensor applications,” IEEE

Sensors J., vol. 13, no. 5, pp. 1931–1940, May 2013.

[34] F. Tang et al., “A linear 126-dB dynamic range light-to-frequency

converter with dark current suppression upto 125

◦

C for blood oxygen

concentration detection,” IEEE Trans. Electron Devices, vol. 63, no. 10,

pp. 3983–3988, Oct. 2016.

[35] C.-T. Chiang and J.-Y. Liou, “Design of a CMOS intelligent light sensing

chip for automatic brightness tuning applications,” IEEE Sensors J.,

vol. 13, no. 12, pp. 4955–4961, Dec. 2013.

[36] C.-T. Chiang, “Design of a CMOS monolithic digitized light detector

with noise insensitivity for light monitoring applications,” IEEE Sensors

J., vol. 14, no. 8, pp. 2537–2545, Aug. 2014.

Cyuyeol Rhee received the B.S. degree in electrical

engineering from the University of Toronto, Toronto,

ON, Canada, in 2010, and the Ph.D. degree in elec-

trical engineering from Seoul National University,

Seoul, South Korea, in 2019.

He is currently a Post-Doctoral Researcher with

Seoul National University. His research interests

include sensor readout circuits for various sensors

and data converters.

Junyoung Park (S’18) received the B.S. degree in

electrical engineering and computer science from

Seoul National University, Seoul, South Korea,

in 2015, where he is currently pursuing the Ph.D.

degree.

His research interests include data convert-

ers and sensor interfaces, including low-power,

high-resolution systems.

Suhwan Kim (S’97–M’01–SM’07) received the

B.S. and M.S. degrees in electrical engineering

and computer science from Korea University, Seoul,

South Korea, in 1990 and 1992, respectively, and the

Ph.D. degree in electrical engineering and computer

science from the University of Michigan, Ann Arbor,

MI, USA, in 2001.

From 1993 to 1999, he was with LG Elec-

tronics, Seoul, South Korea. From 2001 to 2004,

he was a Research Staff Member with IBM Thomas

J. Watson Research Center, Yorktown Heights, NY,

USA. In 2004, he joined Seoul National University, Seoul, where he is

currently a Professor of electrical and computer engineering. His research

interests include analog and mixed-signal integrated circuits, high-speed I/O

circuits, and silicon-photonic integrated circuits.

Dr. Kim was a recipient of the 1991 Best Student Paper Award of the IEEE

Korea Section, the First Prize (Operational Category) in the VLSI Design Con-

test of the 2001 ACM/IEEE Design Automation Conference, the Best Paper

Award of the 2009 Korean conference on semiconductors, and the 2011 Best

Paper Award of the International Symposium on Low-Power Electronics and

Design. He has served as the Organizing Committee Chair of the IEEE Asian

Solid-State Circuits Conference and the General Co-Chair and the Technical

Program Chair of the IEEE International System-on-Chip (SoC) Conference.

He has participated multiple times on the Technical Program Committee

of the IEEE International SOC Conference, the International Symposium

on Low-Power Electronics and Design, the IEEE Asian Solid-State Circuits

Conference, and the IEEE International Solid-State Circuits Conference.

He has served as a Guest Editor for the IEEE J

OURNAL OF SOLID-STATE

CIRCUITS special issue on the IEEE Asian Solid-State Circuits Conference.

452 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 55, NO. 2, FEBRUARY 2020

A 1.9-mW SVM Processor With On-Chip Active

Learning for E pileptic Seizure Control

Shuo-An Huang, Student Member, IEEE, Kai-Chieh Chang, Horng-Huei Liou,

and Chia-Hsiang Yang

, Senior Member, IEEE

Abstract—This article presents a support vector machine

(SVM) processor that supports both seizure detection and on-

chip model adaptation for epileptic seizure control. Alternating

direction method of multipliers (ADMM) is utilized for highly

parallel computing for SVM training. From the algorithm aspect,

minimum redundancy maximum relevance (mRMR) and low-

rank approximation are exploited to reduce overall computa-

tional complexity by 99.4% while also reducing memory storage

by 90.4%. For hardware optimization, overall hardware complex-

ity is reduced by 87% through a hardware-shared configurable

coordinate rotation digital computer (CORDIC)-based processing

element array. Parallel rotations and folded structure for the

approximate Jacobi method reduce overall training latency by

98.6%. The chip achieves a detection performance with a 96.6%

accuracy and a 0.28/h false alarm rate within 0.71 s with the

power dissipation of 1.9 mW. The proposed SVM processor

achieves the shortest detection latency compared with the state-

of-the-art seizure detectors. It also supports real-time model

adaptation with a latency of 0.78 s. Compared with previous

designs, this work achieves a 22× higher throughput and a

162× higher energy efficiency for SVM training.

Index Terms— CMOS digital-integrated circuits, electroen-

cephalogram (EEG), model adaptation, on-chip training, seizure

detection, support vector machine (SVM).

I. INTRODUCTION

E

PILEPSY is a neurological disease caused by abnor-

mal discharges in the brain and affects over 50 million

people worldwide [1]. 70% of epilepsy patients can be

controlled using medication, while the others need to be

treated through brain surgery [2], [3]. However, this surgery

entails potential risks for memory impairm ent, movement

malfunction, or visual field loss. Moreover, surgery may not

be possible for patients who experience untraceable seizures.

Manuscript received July 25, 2019; revised October 17, 2019; accepted

November 12, 2019. Date of publication December 3, 2019; date of current

version January 28, 2020. This article w a s approve d by Associate Editor

Dennis Sylvester. This work was supported in part by the Ministry of Science

and Technology, Taiwan, under Grant MOST 106-2314-B-002-184, in part by

the Intelligent and Sustainable Medical Electronics Research Fund in National

Taiwan Uni versity, and in part by the NOVATEK Fellowship. (Corresponding

author: Chia-Hsiang Yang.)

S.-A. Huang is with the Graduate Institute of Electronics Engineering,

National Taiwan University, Taipei 10617, Taiwan.

K.-C. Chang and H.-H. Liou are with the Department of Neurology, National

Taiwan University Hospital, Taipei 10002, Taiwan.

C.-H. Yang is with the Department of Electrical Engineering, National

Taiwan Uni versity, Taipei 10617, Taiwan, and also with the Graduate Institute

of Electronics Engineering, National Taiwan University, T aipei 10617, Taiwan

(e-mail: chyee@ntu.edu.tw).

Color versions of one or more of the figures in this article are available

online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2019.2954775

Fig. 1. Closed-loop neuromodulation system.

A promising solution is neuromodulation that suppresses the

abnormal brain dynamics through electrical stimulation [3].

Neuromodulation systems can be classified into open-loop

and closed-loop systems. The open-loop system periodically

stimulates a specific region in the brain, while the closed-

loop system only stimulates the brain whenever seizures are

detected.

Fig. 1 shows a closed-loop neuromodulation system. A very

large-scale integration (VLSI) device is placed to sense neural

signals and to detect seizures. The VLSI device includes

analog front-end circuits to record neural signals from elec-

trodes, a digital signal processor for seizure detection, and an

electrical stimulator. Once a seizure is detected, the seizure

detector sends a command to trigger the stimulator. The stim-

ulator generates electrical impulses that can suppress seizures.

In the closed-loop neuromodulation system, the seizure detec-

tor plays a crucial role since effective seizure control relies on

real-time, low-power, and accurate seizure detection.

For seizure detection, several features have been identified

that allow seizures to be distinguished from normal brain

activities. These features include accumulated energy, corre-

lation, synchronization, and so on [4]–[7]. With the aid of

machine-learning techniques, such as a support vector machine

(SVM) [8], [9] and a neural network [10], [11], parameters

for seizure detection can be properly selected through training

samples. An SVM has a lower computational complexity for

inference and achieves a better performance given a few train-

ing samples, which is usually the case for seizure detection.

Shoeb [12] demonstrated an SVM-based seizure detection

0018-9200 © 2019 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission.

See http://www.ieee.org/publications_standards/publications/rights/index.html for more information.

HUANG et al.: 1.9-mW SVM PROCESSOR WITH ON-CHIP ACTIVE LEARNING FOR EPILEPTIC SEIZURE CONTROL 453

algorithm using spectral-energy features. For hardware real-

ization, an analog approach has been proposed for classifi-

cation [13]. Analog SVM classifiers [14], [15] achieve short

classification latencies, but only support simple classification

models with small feature dimensions. In contrast, digital

approaches [16]–[20] accommodate complex SVM models and

achieve higher classification accuracies.

However, seizure patterns differ from patient to patient and

may vary over time [22]. In addition, several non-seizure

patterns, such as eye blinking, cannot be easily classified.

A cu stom model is preferred in order to improve the detection

accuracy, but a low incidence of seizures makes pre-training

for personal SVM models difficult, even with 24-h electroen-

cephalography (EEG) recordings. Thus, a machine-learning

kernel that includes active learning, also regarded as model

adaptation, is essential for mitigating temporal variations by

tracking the latest recorded data and dynamically adjusting the

model.

An off-line model adaptation is proposed in [18], which

wirelessly transmits EEG signals to an external device. The

model is then re-trained based on the new incoming data,

and the updated weights are sent back to the VLSI device

to aid in subsequent detection. However, this approach entails

risks in security and privacy. Wireless transmission also intro-

duces additional power consumption. On-chip adaptation is

preferable and necessary, but it poses challenges for hardware

design due to the high computational complexity. An on-chip

trainable analog SVM classifier is proposed in [23], but it

only supports 12 2-D training samples, which is not sufficient

for practical applications. A sequential minimal optimization

(SMO)-based SVM training algorithm has been realized on a

field-programmable gate array (FPGA) [24], [25]. However,

the slow convergence characteristics of the SMO algorithm

require a high clock frequency and introduce high p ower given

the real-time constraints. An algorithm that provides a fast

convergent rate is, therefore, critical for low-power and real-

time model adaptation.

This ar ticle presents an SVM processor for seizure d etection

with active learning to achieve on-chip adaptation with low

power consumption in real time. The proposed seizure detector

supports both SVM inference and training based on the

selected features proposed in [12]. An SVM training algorithm

is developed by employing the alternating direction method

of multipliers (ADMM), which can be computed in a highly

parallel way and achieves rapid convergence [26]. To achieve

a high d etection accuracy, a non-linear SVM is applied. The

complexity of ADMM-based non-linear SVM training is con-

strained by the matrix dimensions, which is associated with the

number of training samples [27]. To enhance the flexibility of

hardware design, a minimum-redundancy maximum-relevance

(mRMR) feature selection determines the most representative

features to reduce the overall computational complexity [28].

Furthermore, a low-rank approximation is used for the kernel

matrix to further reduce matrix computation complexity [29].

For hardware design, a configurable coordinate rotation digital

computer (CORDIC)-based processing element (PE) array

is proposed that computes the required linear and non-

linear functions. Real-valued fast Fourier transform (RFFT)

is efficiently realized b y using complex-valued FFT (CFFT).

To tackle the large dynamic data range during the training

process, a custom floating-point (FLP) arithmetic unit is pro-

posed. The contributions of this work include the following.

1) The computational complexity for SVM inference and

training is greatly reduced by 99.4% through low-

rank approximation, making real-time seizure detection

feasible.

2) A customized FLP arithmetic unit and an FLP

CORDIC-based PE support precise computation to

tackle a high dynamic range in the training process.

3) A hardware-shared and folded SVM processor architec-

ture reduces the silicon area by 87%.

4) A PE array architecture that implements an approximate

Jacobi method with parallel rotations reduces the latency

for eigenvalue decomposition (EVD) by 98.6%.

5) An on-chip SVM model adaptation scheme used for

seizure d etection reduces the false alarm rate (FAR) by

nearly 40%.

This article is organized as follows. Section II describes

the seizure detection algorithm and the ADMM-based SVM

training algorithm. Techniques for complexity reduction at

the algorithm level are also presented. Section III describes

the system architectu re and the design features for efficient

hardware mapping. Section IV shows the chip validation

and the performance comparison. Finally, Section V draws

conclusions.

II. SVM-B

ASED SEIZURE DETECTION AND TRAINING

SVM is a supervised machine-learning model for solving

binary classification problems. It features sparse weights and

low computational complexity in inference. SVMs can be

categorized into linear and non-linear types. A non-linear SVM

provides higher classification accuracy than the linear SVM

when the data are non-linearly distributed. Thus, the non-

linear SVM is adopted in this work to achieve accurate

seizure detection. Although the non-linear SVM performs

better in classification, its computational complexity in both

inference and training is much higher than its linear counter-

part. Techniques for reducing the complexity of the non-linear

SVM are, therefore, applied.

A. Feature Extraction for Seizure Detection

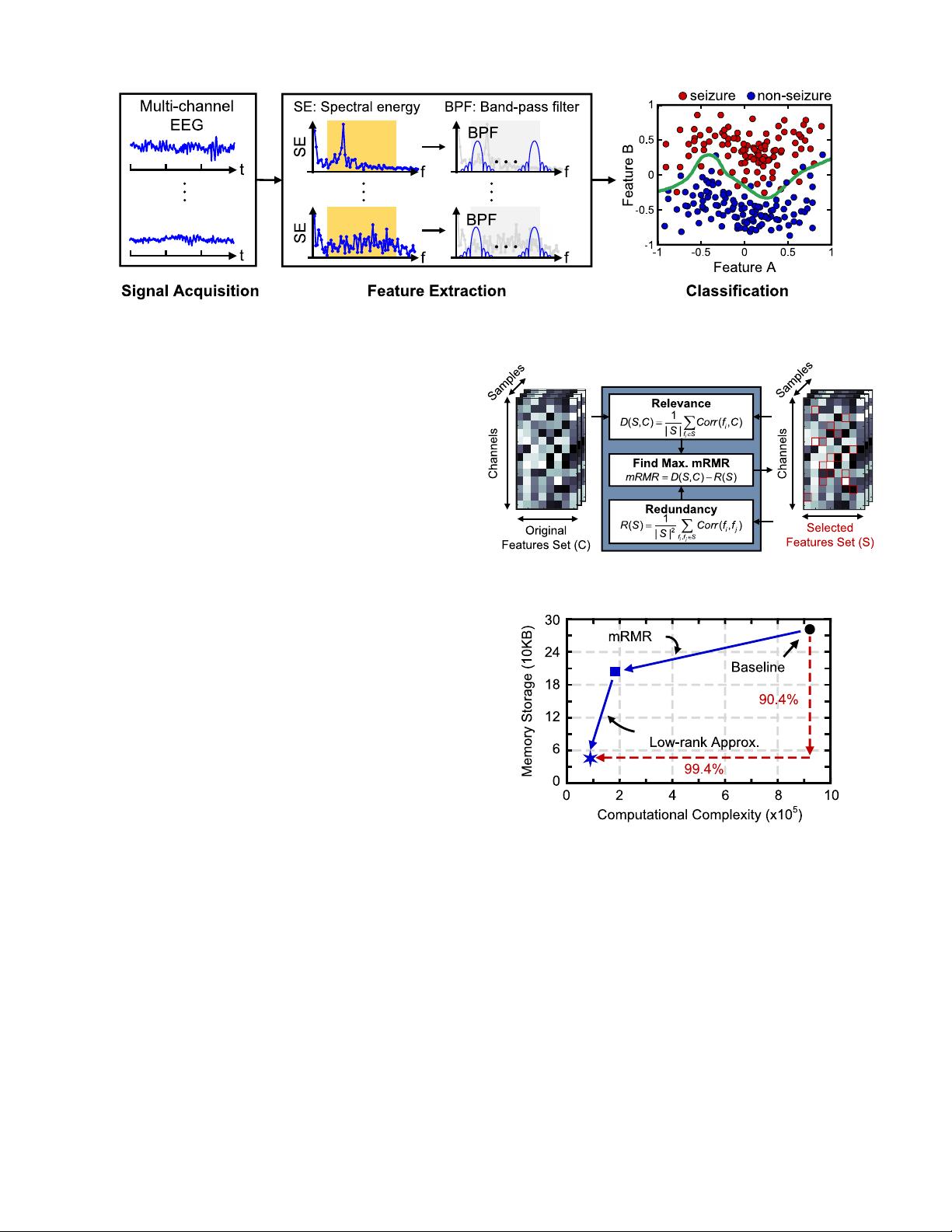

Fig. 2 shows the flow for SVM-based seizure detection.

The spectral features fro m multi-channel EEG signals are

extracted and classified. For each channel, the EEG signals

are transformed into the spectral domain in a window size

of 512 samples. The spectral energy features are extracted

from the 0.5–24-Hz frequency band, as in [12]. Since the

spectra of both seizures and normal events (such as eye

blinks) contain large energy components [12], which suppress

the components in other frequency bands, the low-frequency

band of 0.5–3 Hz is discarded here. In this work, eight

spectral energy features from each channel are extracted

from the 3–26-Hz frequency band, yielding 112 features for

14 channels.

454 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 55, NO. 2, FEBRUARY 2020

Fig. 2. Seizure detection using a non-linear SVM classifier.

B. ADMM-Based SVM Training

Many SVM training algorithms have been developed for

SVMs by employing decomposition techniques, such as

SMO [31], LIBSVM [32], and the cutting-plane method [33].

However, most are highly sequential and unsuitable for parallel

processing on the hardware. ADMM is a technique that

partitions a variable-jointed convex optimization problem into

several smaller and easier problems to manage sub-problems

so that the targeting variables or weight coefficients can be

alternatively updated in a parallel manner [34]. In this work,

a highly parallel ADMM-based algorithm is adopted to solve

the non-linear SVM training problem and to achieve real-

time training [35]. Comp ared with SMO, the ADMM-based

algorithm achieves a 9.8 × 10

7

shorter latency in convergence.

The details of the mathematical formulation for the

ADMM-based SVM training algorithm can be found in [35].

This type of ADMM-based algorithm for SVM training

involves large-scale matrix inversion, in which the matrix

dimensions are associated with the number of training samples.

Generally, the matrix dimensions range from hundreds to

thousands for seizure detection applications, m aking hardware

realization infeasible. To address this issue, feature selec-

tion [28] and rank approximation [29] are utilized in order

to reduce the memory storage and computational complexity

required.

C. Feature Selection

In this work, the mRMR feature selection alg orithm [28] is

applied to reduce the feature vector dimensions. The mRMR

algorithm selects the features that have the maximum relevance

D with the original feature set C,aswellastheminimum

redundancy R with the selected feature set S,asshown

in Fig. 3. The redundancy and relevance are measured by

the correlation. The mRMR algorithm reduces the computa-

tional complexity in both training and inference for an SVM

classifier. After applying feature selection, only 16 features

are needed rather than 112 spectral-energy features. Without

sacrificing the detection accuracy, the memory storage and

computational computation are reduced by 26% and 81%,

respectively.

D. Rank Approximation

Applying the ADMM algorithm to the non-linear SVM

training problem is still challenging since it involves

Fig. 3. mRMR feature selection flow.

Fig. 4. Computational complexity and memory storage reductions due to

feature selection and low-rank approximation.

high-dimensional matrix manipulations. The Nyström

method [29] is used to approximate the kernel matrix by

determining a rank-r matrix

˜

as given by

≈

˜

= V · V

T

. (1)

The rank r can be much smaller than the original matrix

dimensions, which greatly reduces the computational complex-

ity for the associated matrix manipulations.

Table I shows the hardware complexity for the linear

SVM, the non-linear SVM, and the model adopted in this

work. The minimum N is 256 and r is set to 16. The

dimensions for the matrix inversion for non-linear SVM

training are reduced from N × N to r × r. It is noted that

the non-linear decision boundary property is preserved even

HUANG et al.: 1.9-mW SVM PROCESSOR WITH ON-CHIP ACTIVE LEARNING FOR EPILEPTIC SEIZURE CONTROL 455

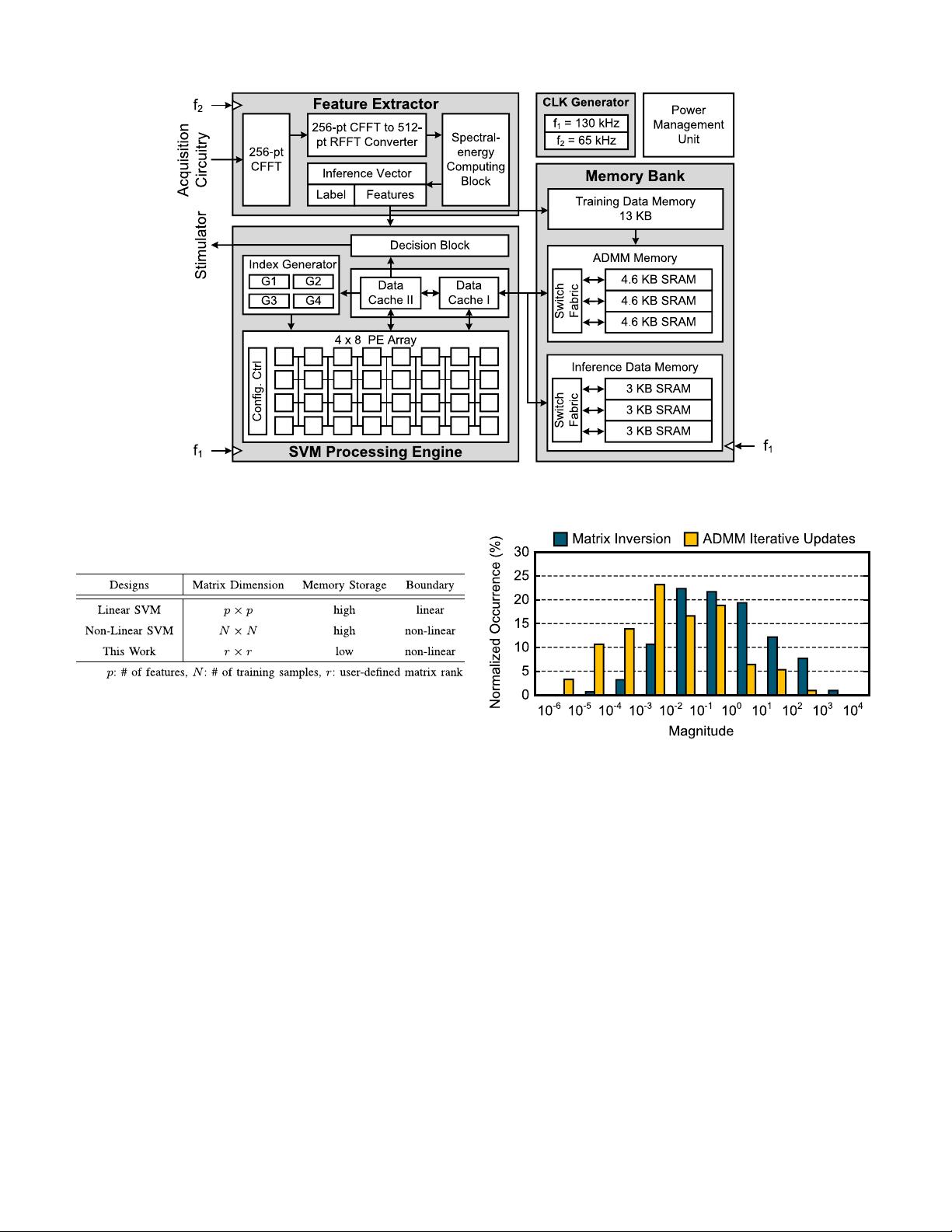

Fig. 5. System architecture for the proposed SVM processor .

TABLE I

H

ARDWARE COMP LEXITY F OR TRAINING

if the rank of the kernel matrix is approximated. A high

classification accuracy is still achieved with a much lower

computational complexity. By applying rank approximation,

the computational complexity and the memory storage are

reduced by 97% and 87%, respectively. Additionally, low-rank

approximation also reduces the computational complexity for

SVM inference, which is proportional to the number of support

vectors. By employing low-rank approximation, the number

of support vectors is reduced from N to r, enabling real-time

inference for seizure d etection.

Fig. 4 summaries the reductions in computational com-

plexity and memory storage after applying both the feature

selection and the low-rank approximation techniques. The

overall computational complexity is reduced by 99.4% and

the memory storage is reduced by 90.4%. This allows feasible

hardware mapping for on-chip SVM training.

III. S

YSTEM ARCHITECTURE

Fig. 5 shows the proposed SVM processor for seizure

detection. The processor includes a feature extractor, an SVM

processing engine, and a memory bank. The spectral-energy

features are extracted through RFFT, which can be effi-

ciently realized by CFFT, requiring half the number of points.

Fig. 6. Dynamic range analysis for both the matrix inversion and ADMM

variable update phases.

The extracted features are either sent to the SVM processing

engine for SVM inference or stored in the training data

memory for model adaptation. All the computations required

in both the SVM inference and the training are performed

in parallel through a configurable CORDIC-based PE array.

The PE array can be configured to support various matrix

manipulations with different dimensions. Two caches are

designed to store the recently used and the intermediate data.

Four parallel index generators generate the rotation indices

for matrix inversion. Two clock domains are allocated and

clock gating is extensively applied so as to reduce power

consumption.

A. Cu stomized FLP Arithmetic Unit

Fig. 6 shows the dynamic range analysis for both the matrix

inversion and the ADMM iterative update phases. As a refer-

ence design, 34-bit datapaths in fixed-point (FP) arithmetic

are able to accommodate the dynamic range of [10

−6

,10

4

].

剩余302页未读,继续阅读

2019-10-29 上传

2012-03-08 上传

2023-07-08 上传

2024-02-22 上传

2023-07-08 上传

2023-04-05 上传

2023-03-26 上传

2023-06-03 上传

netshell

- 粉丝: 11

- 资源: 185

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- Angular程序高效加载与展示海量Excel数据技巧

- Argos客户端开发流程及Vue配置指南

- 基于源码的PHP Webshell审查工具介绍

- Mina任务部署Rpush教程与实践指南

- 密歇根大学主题新标签页壁纸与多功能扩展

- Golang编程入门:基础代码学习教程

- Aplysia吸引子分析MATLAB代码套件解读

- 程序性竞争问题解决实践指南

- lyra: Rust语言实现的特征提取POC功能

- Chrome扩展:NBA全明星新标签壁纸

- 探索通用Lisp用户空间文件系统clufs_0.7

- dheap: Haxe实现的高效D-ary堆算法

- 利用BladeRF实现简易VNA频率响应分析工具

- 深度解析Amazon SQS在C#中的应用实践

- 正义联盟计划管理系统:udemy-heroes-demo-09

- JavaScript语法jsonpointer替代实现介绍

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功