纳米级低功耗容错数字IC设计挑战与解决方案

需积分: 10 121 浏览量

更新于2024-07-19

收藏 13.23MB PDF 举报

随着科技的飞速发展,半导体行业一直遵循着摩尔定律(Moore's Law)这一准则,该定律由戈登·摩尔(Gordon Moore)在1965年提出,描述了集成电路(IC)上集成元件数量每两年翻一番的趋势。然而,随着技术向纳米级(nanoscale)不断推进,低功耗和容错数字IC设计面临了一系列新的挑战。

首先,技术尺度的缩小(Technology Scaling)是推动摩尔定律的关键,但也带来了功率消耗问题(Challenges of Power Consumption)。随着器件尺寸减小,漏电流(leakage current)显著增加,这对电池寿命和整体系统效率构成威胁。因此,设计师必须采用先进的电源管理策略,如动态电压和频率调整(DVFS)、睡眠模式和待机模式,来降低静态功耗。

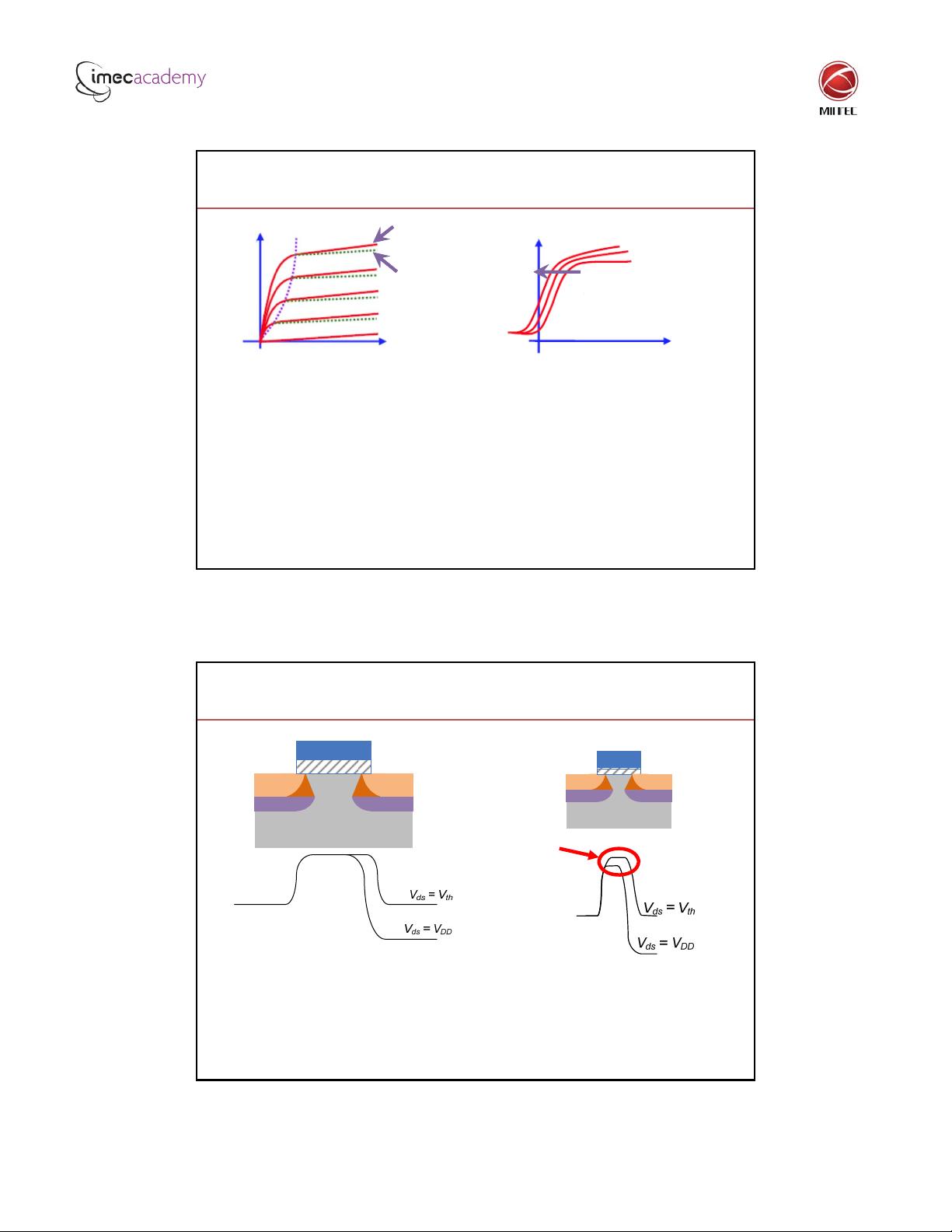

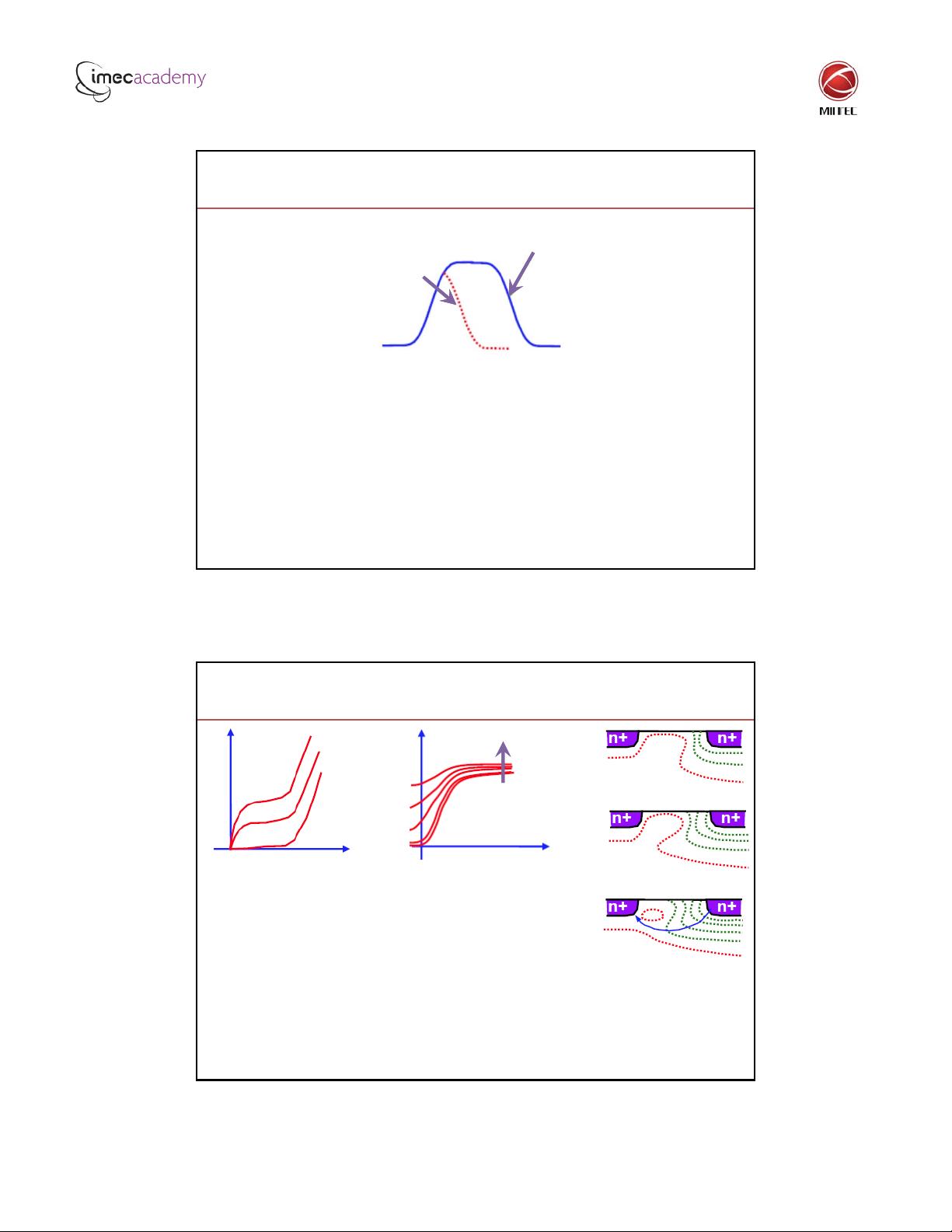

其次,短通道效应(Short Channel Effects, SCEs)是另一个关键挑战。在纳米级别,金属-氧化物-半导体场效应晶体管(MOSFETs)的栅极长度变短,导致阈值电压降低、电子迁移率下降,以及寄生效应加剧。这要求设计师进行精细的器件模型优化,同时开发新型材料和结构,如High-K gate dielectrics和FinFETs,来改善这些效应。

第三,变异性和可靠性问题(Challenges of Variability)成为不容忽视的难题。纳米尺度下,工艺过程中的随机性和一致性下降,使得同一工艺节点的芯片间性能差异增大。为了实现容错设计,需要引入误差校正码(ECC)、自修复逻辑或自适应算法,以提高电路对变异性的容忍度。

在解决这些挑战的过程中,IMEC等研究机构发挥着重要作用,他们不仅提供先进的工艺技术,如深亚微米技术(deep-submicron technology),还通过研究如离子注入MOSFET的设计方法,持续探索创新解决方案。IMEC的Page2展示了工程师们如何通过理论与实践相结合,确保在不断缩小的尺寸限制下,保持电路性能的同时满足低功耗和容错性需求。

总结来说,纳米级低功耗容错数字IC设计是一项复杂的任务,它要求设计师在技术发展和商业需求之间找到平衡。通过理解并应对技术尺度、功率消耗、短通道效应和变异性的挑战,才能在摩尔定律的驱动下,继续推动半导体行业的进步。

2018-11-20 上传

2021-07-26 上传

2020-12-01 上传

2020-11-30 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

qq_17616613

- 粉丝: 0

- 资源: 2

最新资源

- 探索数据转换实验平台在设备装置中的应用

- 使用git-log-to-tikz.py将Git日志转换为TIKZ图形

- 小栗子源码2.9.3版本发布

- 使用Tinder-Hack-Client实现Tinder API交互

- Android Studio新模板:个性化Material Design导航抽屉

- React API分页模块:数据获取与页面管理

- C语言实现顺序表的动态分配方法

- 光催化分解水产氢固溶体催化剂制备技术揭秘

- VS2013环境下tinyxml库的32位与64位编译指南

- 网易云歌词情感分析系统实现与架构

- React应用展示GitHub用户详细信息及项目分析

- LayUI2.1.6帮助文档API功能详解

- 全栈开发实现的chatgpt应用可打包小程序/H5/App

- C++实现顺序表的动态内存分配技术

- Java制作水果格斗游戏:策略与随机性的结合

- 基于若依框架的后台管理系统开发实例解析