WP505 (v1.0) 2018 年 10 月 2 日

china.xilinx.com 5

Versal:首款自适应计算加速平台 (ACAP)

标量引擎基于双核 Arm® Cortex-A72 构建,与赛灵思上一代 Arm Cortex-A53 核相比,每核单线程性

能提高了 2 倍。高级的架构和 7nm FinFET 工艺的功耗相结合,DMIPS/WAT 与先前的 16nm 实现方

案相比提高了 2 倍。立足赛灵思目前在汽车业大量部署的经验,经 ASIL-C 认证的 (1) UltraScale

+™Cortex-R5 标量引擎结合额外的系统级安全特性向 7nm 迁移。

自适应引擎由可编程逻辑和存储器单元组成,与新一代业界最快的可编程逻辑相连。除了支持原有设

计之外,还可以重新编程这些结构,以形成针对特定计算任务定制的存储器层级。与最新的 GPU 和

CPU 相比,赛灵思智能引擎可实现 更高的循环效率和更高的单位计算存储器带宽。这是优化边缘时

延与功耗,以及优化核心绝对性能的关键。

智能引擎由一组创新的超长指令字 (VLIW) 和单指令、多个数据 (SIMD) 处理引擎以及存储器构成,彼

此

间的互联速度和存储带宽均为 100Tb/s。这使机器学习和数字信号处理 (DSP) 应用的性能提升了

5-10 倍。

如表 1所示,这些计算函数以不同的比率和大小混合,构成了 Versal 器件产品组合。

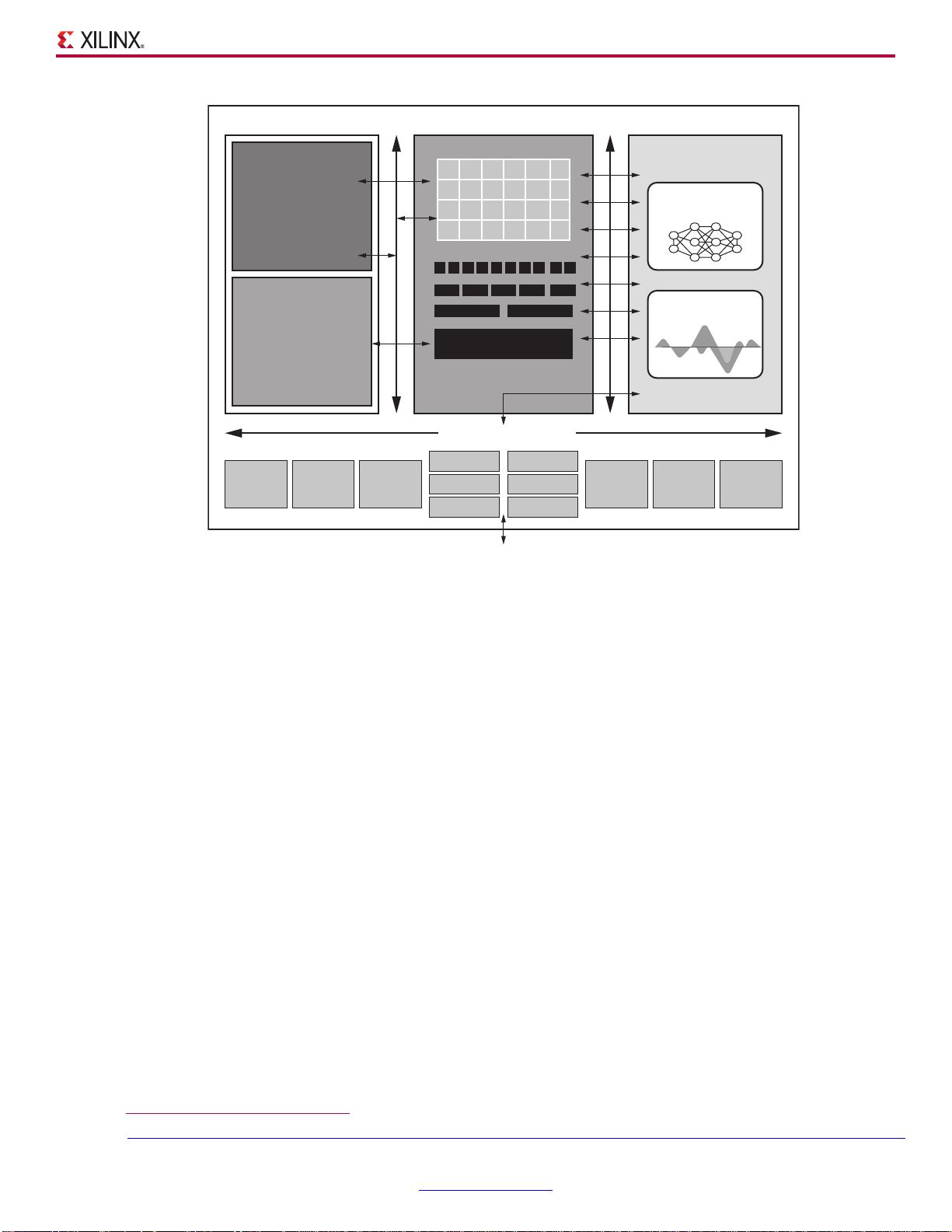

X-Ref Target - Figure 4

图 4:

赛灵思 Versal ACAP 功能图

1. https://china.xilinx.com/news/press/2018/xilinx-announces-availability-of-automotive-qualified-zynq-ultrascale-mpsoc-family.html

标量引擎

Arm

双核

Cortex-R5

自适应引擎 智能引擎

AI 引擎

片上网络

Arm

双核

Cortex-A72

Custom Memory

Hierarchy

PCIe

CCIX

DDR

LPDDR

HBM

MIPI

LVDS 3.3V

GPIO

112Gb/s

58Gb/s

32Gb/s

Nx 100G

以太网

600G

核

直接

RF

DSP 引擎

WP505_04_092718