电子科技大学周玉川:数值比较器与74LS161计数器实验详解

需积分: 0 90 浏览量

更新于2024-08-04

收藏 4.83MB DOCX 举报

在本次实验中,学生周玉川,学号2017221302006,在电子科技大学信息与软件工程学院进行了数字逻辑课程的相关实验。实验的主要内容围绕数值比较器和计数器的设计与实现展开。

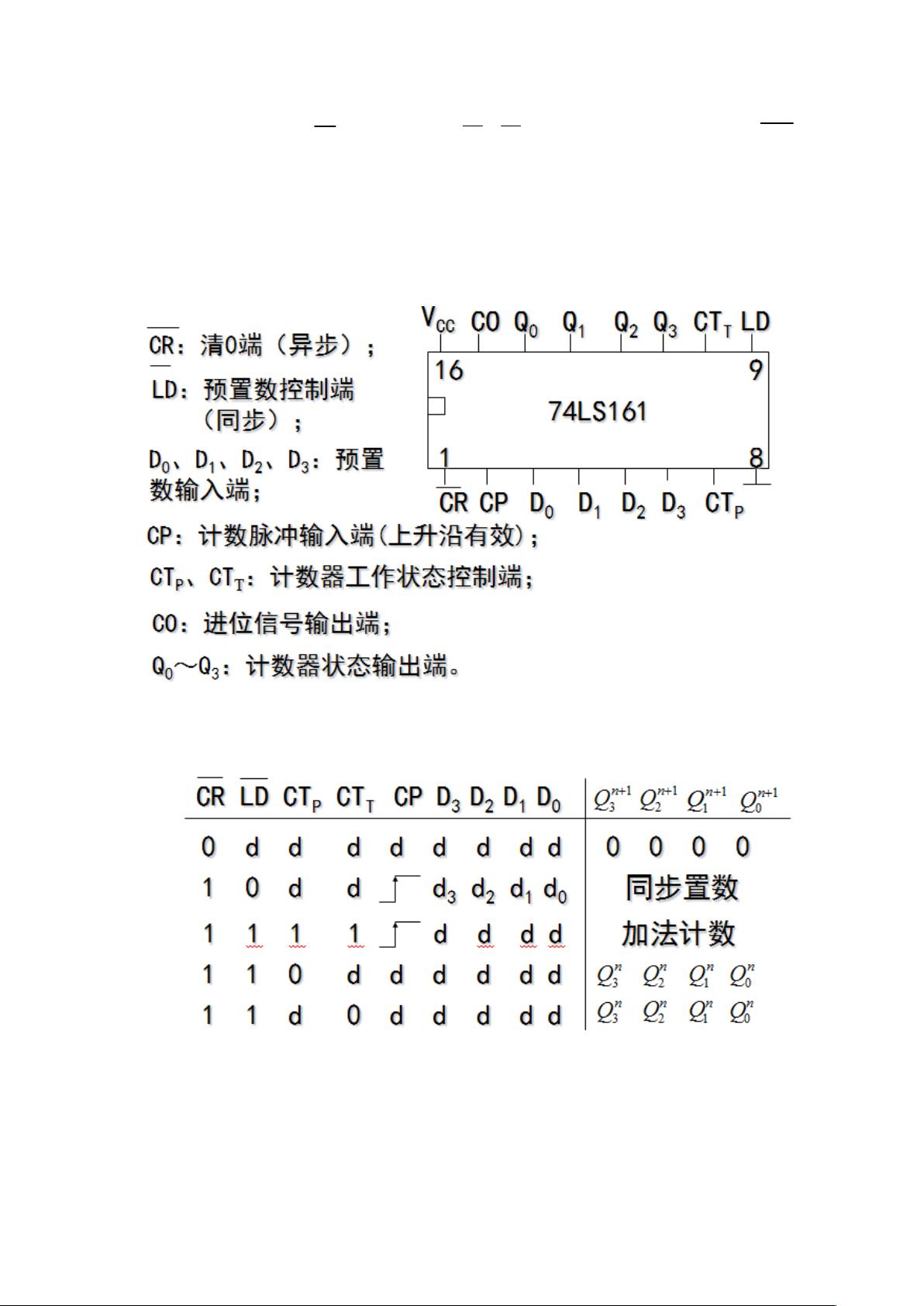

首先,实验涉及的器材包括数字逻辑试验箱、导线以及多种集成器件,如74LS00(与非门)、74LS04(非门)、74LS86(异或门)和74LS161(4位二进制同步计数器)。这些器件在实验中扮演了关键角色,它们被用于构建基本的逻辑单元和复杂的时序逻辑电路。

实验的第一部分是设计一位数值比较器,通过组合74LS86、74LS04和74LS00,实现了真值表中的逻辑功能。学生绘制了逻辑电路图,并进行了实际运算验证,确保电路按预期工作。一位数值比较器的构建展示了基本逻辑门如何进行组合来实现特定的功能。

第二部分是更为复杂的时序逻辑电路——60进制计数器。学生利用74LS161构建了这个计数器,并将其结果通过7段数码管显示出来。实验中采用了预置数法,通过LD控制端实现同步预置数,进而构造了模12和256进制的加法计数器。学生不仅设计了逻辑电路图,还通过实际操作验证了计数器的工作效果。

在整个实验过程中,学生不仅锻炼了逻辑设计能力,也深化了对数字逻辑原理的理解。通过动手搭建和验证电路,他们能够更好地掌握集成器件的使用和不同进制计数器的实现方法。此外,实验记录包括电路设计图和实际操作步骤,这些都是学习和评估实验成果的重要依据。

实验结果以六个图表的形式呈现,即两位数值比较器的逻辑结构图和实际电路图,以及60进制计数器的逻辑设计图和实验记录。这些数据和图像对于理解实验原理和验证设计的正确性至关重要。

总结来说,这次实验让学生在实践中应用了所学的数字逻辑理论,提升了他们的实验技能和问题解决能力,同时也强调了理论与实践相结合的重要性。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

2022-08-08 上传

洪蛋蛋

- 粉丝: 31

- 资源: 334

最新资源

- 网上书店可行性分析与需求分析

- C语言编程规范.pdf

- SQL server服务器大内存配置

- 世界上最全的oracle笔记 oracle 资料

- Programming C#

- MIT Linear Programming Courseware- example

- 一份在线考试系统的详细开发文档C#

- 在线考试系统需求说明

- 企业网站推广经合与体会

- convex optimization

- 芯源电子单片机教程(推荐).pdf

- c语言学习300例(实例程序有源码)

- thinking in java

- How to create your library

- Microsoft Windows CE学习资料

- _CC2001教程_研究与思考.pdf