PCI Express® 4.0: 电气预览与技术解析

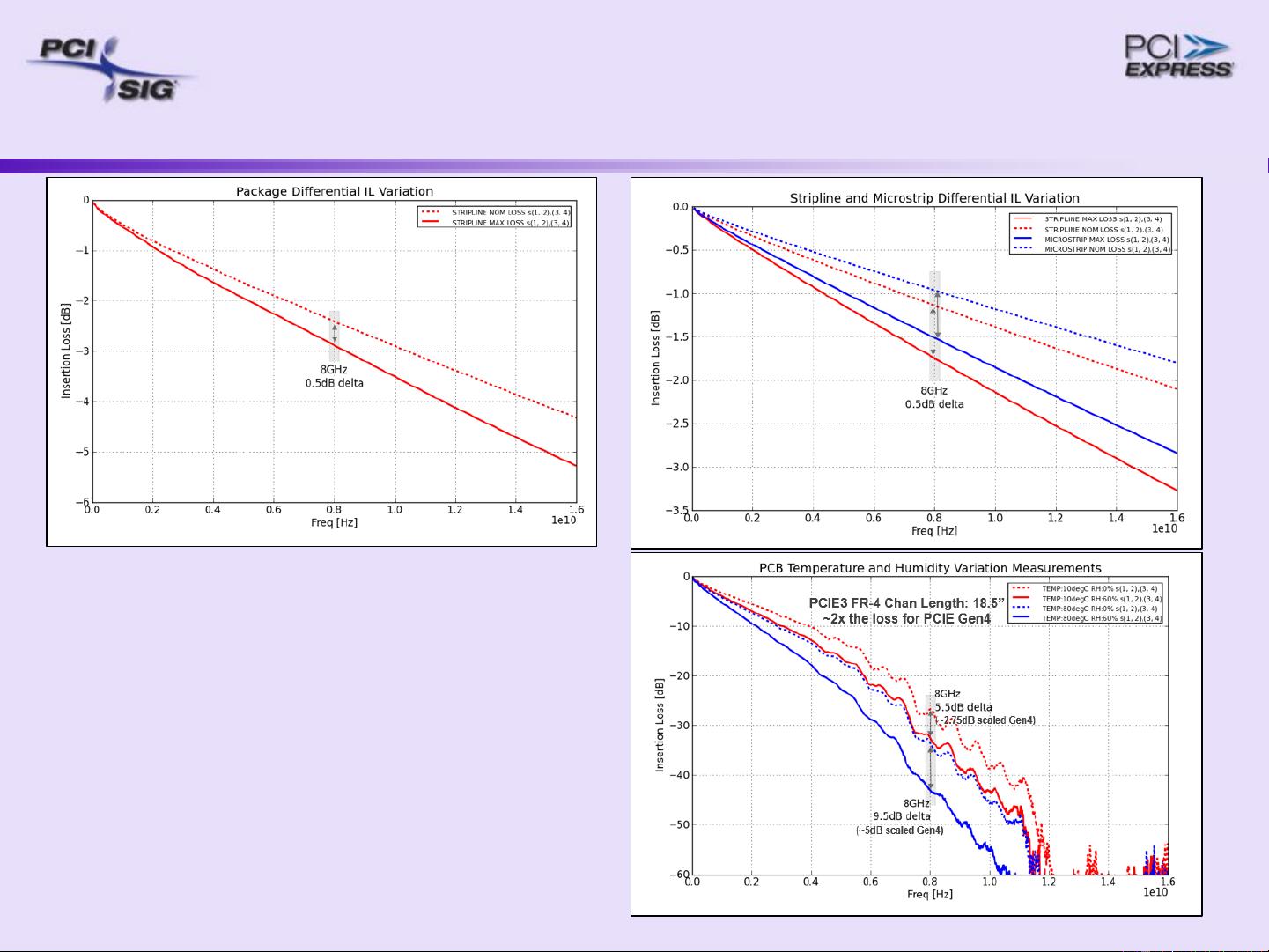

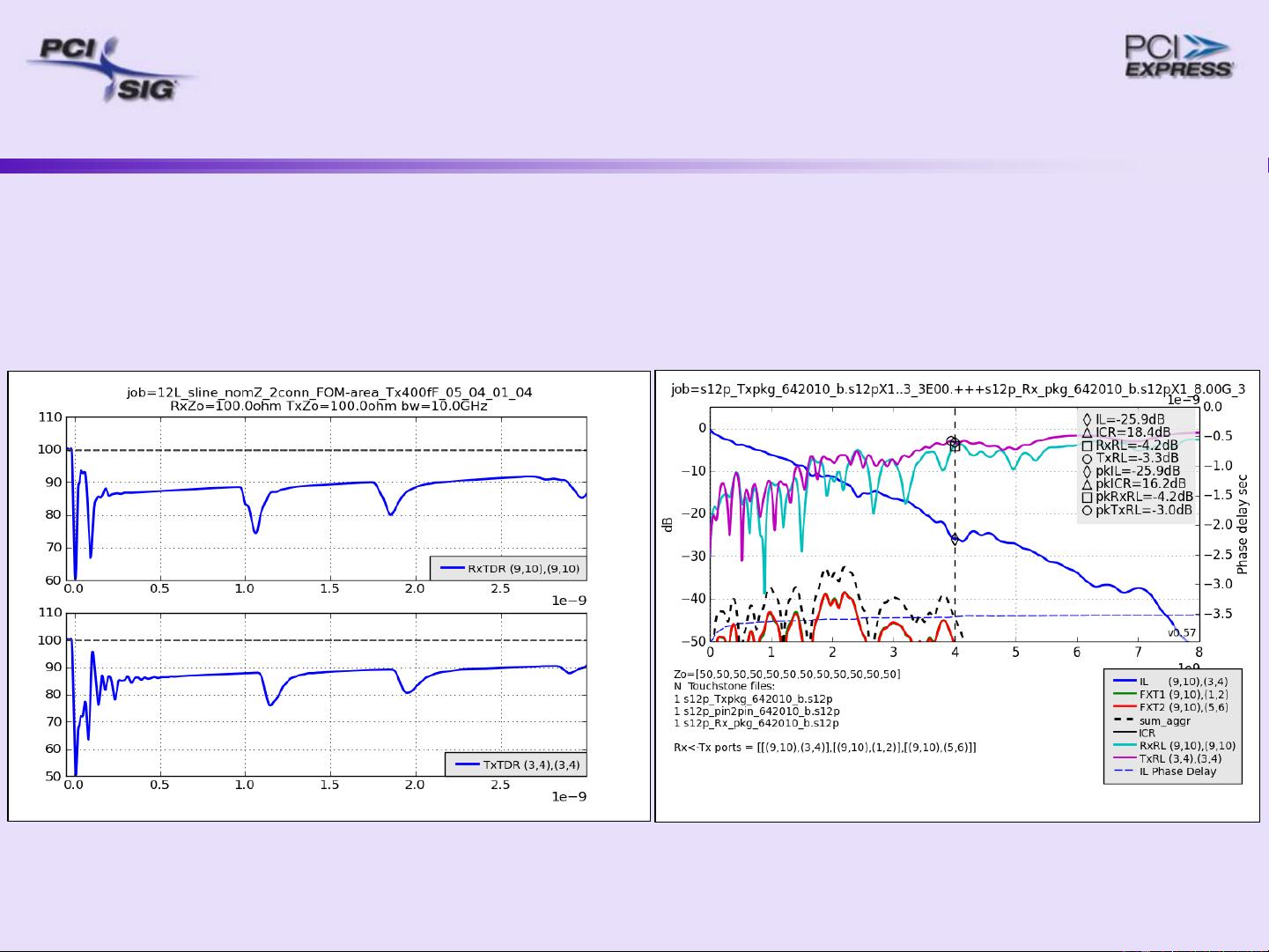

"PCI Express® 4.0 Electrical Previews (Frozen) 提供了关于PCI Express 4.0规范在电气设计方面的预览,由Advanced Micro Devices的Dean Gonzalez在PCI-SIG开发者大会上进行讲解。这份资料涵盖了PCIe 4.0的动机、概述,通道描述,发射器,接收器,参考时钟与SRIS(自适应接收器均衡),以及设计与仿真等方面的内容。" 正文: PCI Express(PCIe)是一种高速接口标准,用于连接计算机系统中的外部设备,如显卡、网卡和硬盘。PCIe 4.0是PCIe规范的第四代,它的主要目标是进一步提升数据传输带宽,以满足网络、存储和高性能计算等领域不断增长的需求。 **PCIe 4.0的动机与概述** PCIe 4.0的出现主要是由于对更高带宽的需求持续增长。从PCIe 2.x到3.0,带宽翻倍,提供了显著的性能提升。同样的动力推动了从PCIe 3.0到4.0的转变。新一代PCIe标准的目标是至少提供两倍于上一代的传输速率,同时尽可能地利用和扩展现有的PCIe 3.0基础设施,包括物理层(PHY)架构,以降低生态系统的升级成本。 **PCIe通道描述** 通道是PCIe连接的基础,它由一对差分信号线组成,用于传输数据。在PCIe 4.0中,通道的设计需要优化,以支持更高的信号频率,同时保持足够的信号完整性和抗干扰能力。 **发射器** 发射器是PCIe 4.0系统中的关键组件,负责将数字数据转换为模拟信号,通过通道发送。为了在更高的速度下保持信号质量,发射器可能需要更精细的调谐,例如增强预加重和均衡技术,以减少信号失真。 **接收器** 接收器在通道的另一端,负责接收并恢复信号。在PCIe 4.0中,接收器需要具有更高的灵敏度和噪声容忍度,以正确解析在高频率下可能出现的弱信号。 **参考时钟与SRIS** 参考时钟是所有数据传输的时间基准,对于保持信号同步至关重要。在PCIe 4.0中,可能会采用更精确的时钟源,并且SRIS(自适应接收器均衡)技术帮助接收器根据通道条件动态调整,以适应潜在的信号衰减。 **设计与仿真** 在开发PCIe 4.0规范时,设计者需要进行大量的模拟和测试,确保新标准在各种环境和条件下都能稳定工作。这包括模拟通道行为、发射器和接收器的性能,以及整个系统的电源完整性。 PCIe 4.0是为了解决日益增长的数据传输需求而推出的技术升级,通过优化通道、发射器和接收器设计,以及改进参考时钟和接收器均衡技术,实现了更高的带宽和更可靠的数据传输。尽管处于预览阶段,但这些技术的最终目的是在保持向后兼容性的同时,提供下一代高速接口的性能。

剩余45页未读,继续阅读

- 粉丝: 0

- 资源: 3

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 构建Cadence PSpice仿真模型库教程

- VMware 10.0安装指南:步骤详解与网络、文件共享解决方案

- 中国互联网20周年必读:影响行业的100本经典书籍

- SQL Server 2000 Analysis Services的经典MDX查询示例

- VC6.0 MFC操作Excel教程:亲测Win7下的应用与保存技巧

- 使用Python NetworkX处理网络图

- 科技驱动:计算机控制技术的革新与应用

- MF-1型机器人硬件与robobasic编程详解

- ADC性能指标解析:超越位数、SNR和谐波

- 通用示波器改造为逻辑分析仪:0-1字符显示与电路设计

- C++实现TCP控制台客户端

- SOA架构下ESB在卷烟厂的信息整合与决策支持

- 三维人脸识别:技术进展与应用解析

- 单张人脸图像的眼镜边框自动去除方法

- C语言绘制图形:余弦曲线与正弦函数示例

- Matlab 文件操作入门:fopen、fclose、fprintf、fscanf 等函数使用详解

信息提交成功

信息提交成功