FPGA实现的SPI接口设计与Verilog仿真

67 浏览量

更新于2024-08-31

1

收藏 242KB PDF 举报

“EDA/PLD中的基于FPGA的串行外围接口SPI设计与实现”

本文主要探讨了在EDA/PLD(电子设计自动化/可编程逻辑器件)领域中,如何基于FPGA(现场可编程门阵列)实现SPI(串行外围接口)总线的设计和功能验证。SPI总线是一种高效的同步串行数据传输接口,其特点包括全双工通信、信号线数量少、协议简洁以及高速传输能力。这些特性使得SPI在各种嵌入式系统和微控制器应用中被广泛采用。

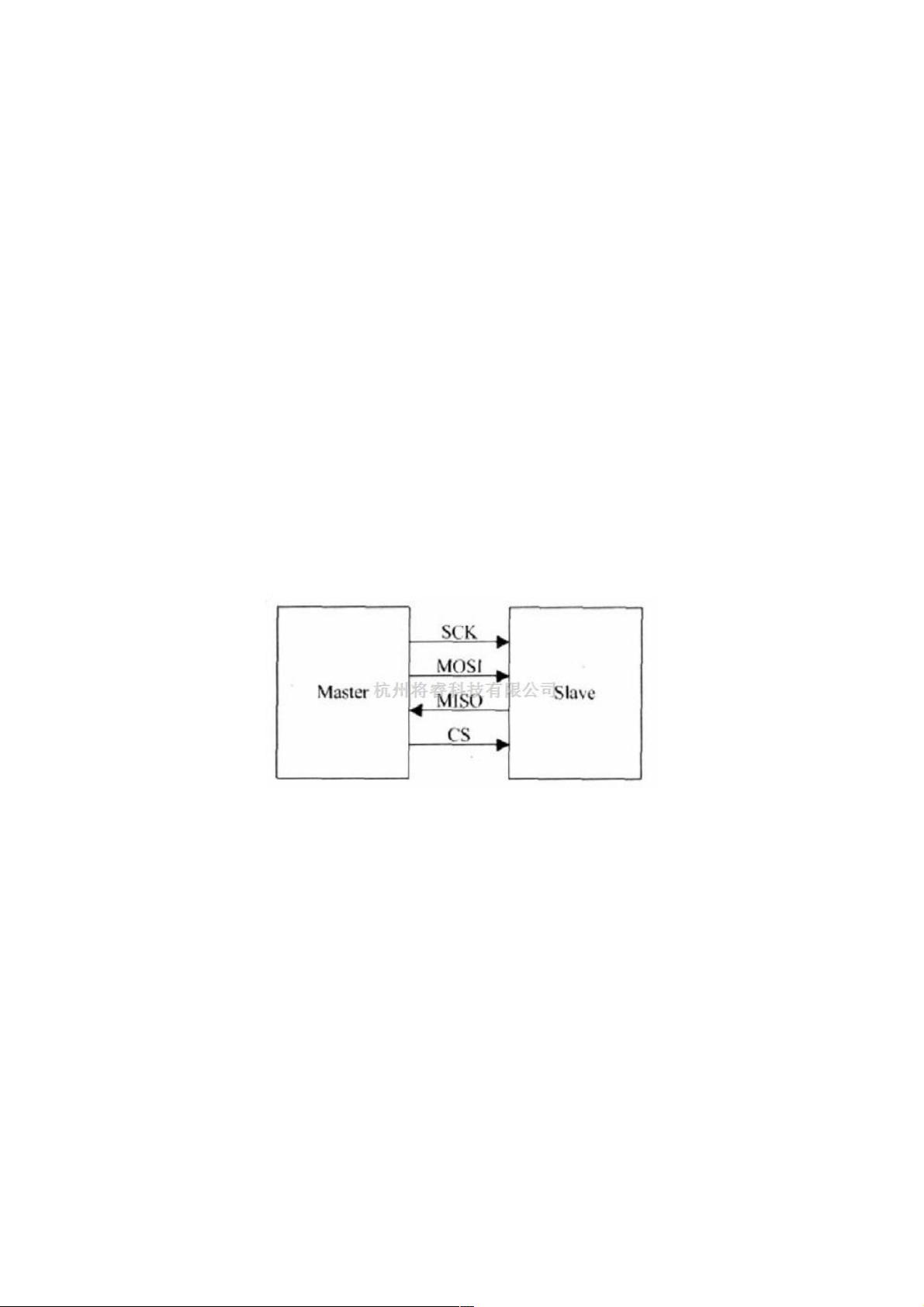

SPI总线通常由四条主要信号线组成:主设备(Master)输出/从设备(Slave)输入(MOSI)、主设备输入/从设备输出(MISO)、串行时钟(SCLK)和芯片选择(CS或SS)。SPI支持四种不同的工作模式,它们的主要区别在于数据在时钟上升沿还是下降沿被采样,以及数据的移位方向。理解这些模式的异同对于正确设计SPI接口至关重要。

在设计SPI主机模块时,作者使用了Verilog硬件描述语言,这是一种广泛用于数字电路设计的编程语言。通过ModelSim仿真工具,可以验证设计的正确性,确保SPI主机模块按照预期产生和接收数据。仿真波形的分析是验证设计功能的关键步骤,它能直观地显示SPI总线的时序行为。

在设计验证阶段,作者使用了Xilinx ISE工具套件,这是一款流行的FPGA设计和实现平台。SPI主机模块经过综合和布局布线后,可以被编程到FPGA中。最后,通过实际下载到FPGA并在目标系统上运行,确认了设计的正确性和功能完整性。

FPGA的使用为SPI总线设计提供了极大的灵活性。由于FPGA的可重复编程和可扩展性,设计者可以方便地调整SPI的数据位宽、工作模式,甚至添加额外的功能,以适应不断变化的系统需求。这种灵活性是传统固定功能的ASIC(应用专用集成电路)无法比拟的。

总结来说,该文详细介绍了SPI总线的基本概念、工作原理和设计方法,特别强调了其在FPGA实现中的应用。通过Verilog实现的SPI主机模块经仿真和实际硬件验证,证明了该设计的可行性,为读者提供了一种在EDA/PLD环境中实现SPI接口的参考方案。

104 浏览量

点击了解资源详情

154 浏览量

154 浏览量

174 浏览量

104 浏览量

156 浏览量

195 浏览量

144 浏览量

weixin_38721119

- 粉丝: 10

- 资源: 925

最新资源

- 搜索算法 网站推广研究的好东西

- TR一069协议在家庭网关上的实现

- 计算机网络第4版课后答案 谢希仁版

- oracle dataguard

- 网站策划方案标准实例

- 计算机网络答案(第四版)

- 计算机网络(第四版)国外经典教程+习题答案(中文版)

- Web网站统一口令认证系统的设计与实现

- c sharp 3.0 Design Patterns

- C#初学者必不可少的材料

- 进销存数据流-功能图.doc

- jstl-jsp的高级课程-减少页面脚本量,你最好的抉择!,pdf版,高清晰!

- java web,,常用软件术语,pdf 格式,非扫描,高清晰1

- 大地球进销存财务管理系统.doc

- 计算机专业编译原理答案

- c# socket网络编程