14

DRV2604L

ZHCSDF4F –MAY 2014–REVISED MARCH 2018

www.ti.com.cn

Copyright © 2014–2018, Texas Instruments Incorporated

Feature Description (continued)

8.3.3 Open-Loop Operation for LRA

In the event that open-loop operation is desired (such as for off-resonance driving) the DRV2604L device

includes an open-loop LRA drive mode that is available through the PWM input or through the digital interface.

When using the PWM input in open-loop mode, the DRV2604L device employs a fixed divider that observes the

PWM signal and commutates the output drive signal at the PWM frequency divided by 128. To accomplish LRA

drive, the host should drive the PWM frequency at 128 times the desired operating frequency.

When activated, the digital open-loop mode is available for pre-stored waveforms as well as for RTP mode. The

OL_LRA_PERIOD bit in register 0x20 programs the operating frequency, which is derived from the PWM output

frequency, ƒ

O(PWM)

. Use Equation 1 to calculate the driving frequency. The open-loop mode does not receive the

benefits of the smart-loop architecture.

8.3.4 Open-Loop Operation for ERM

The DRV2604L device offers ERM open-loop operation through the PWM input. The output voltage is based on

the duty cycle of the provided PWM signal, where the OD_CLAMP[7:0] bit in register 0x17 sets the full-scale

amplitude. For details see the Rated Voltage Programming section.

8.3.5 Flexible Front-End Interface

The DRV2604L device offers multiple ways to launch and control haptic effects. The MODE[2:0] bit in register

0x01 is used to select the interface mode.

8.3.5.1 PWM Interface

When the DRV2604L device is in PWM interface mode, the device accepts PWM data at the IN/TRIG pin. The

DRV2604L device drives the actuator continuously in PWM interface mode until the user sets the device to

standby mode or to enter another interface mode. In standby mode, the strength of vibration is determined by the

duty cycle.

For the LRA, the DRV2604L device automatically tracks the resonance frequency unless the LRA_OPEN_LOOP

bit in register 0x1D is set. If the LRA_OPEN_LOOP bit is set, the LRA is driven according to the frequency of the

PWM input signal. Specifically, the driving frequency is the PWM frequency divided by 128.

8.3.5.2 Internal Memory Interface

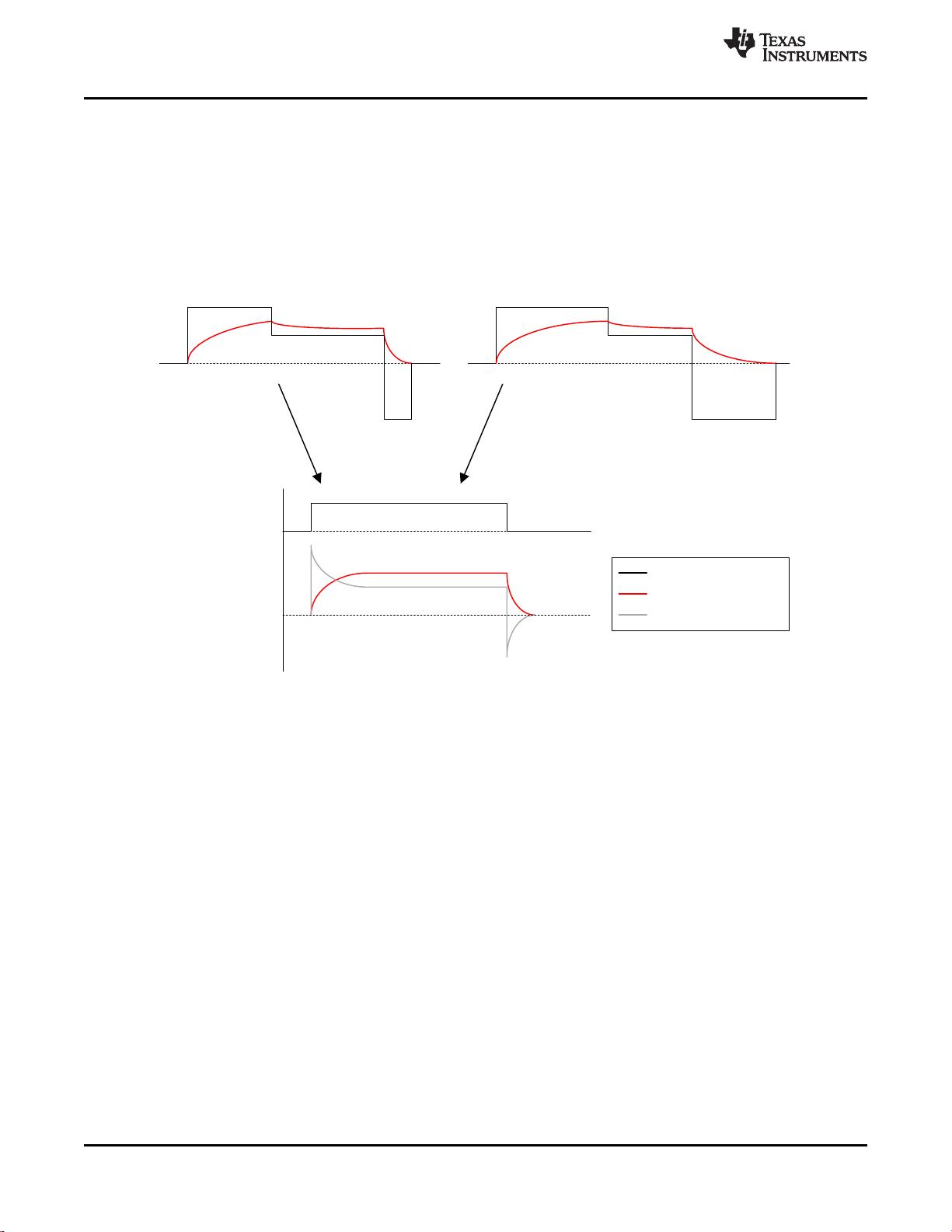

The DRV2604LL device is designed with 2 kB of integrated RAM for waveform storage used by the playback

engine. The data is stored in an efficient way (voltage-time pairs) to maximize the number of waveforms that can

be carried. The playback engine also has the ability to generate smooth ramps (up or down) by relying on the

start-waveform and end-waveform points and by using linear interpolation techniques.

Storing waveforms on the DRV2604LL device instead of the host processor has several advantages including:

• Offloading processing requirements, such as PWM generation, from the host processor or micro-controller

• Improving latency by storing the waveforms on the DRV2604LL device and only requiring a trigger signal

• Reducing I

2

C traffic by eliminating the requirement to transfer waveform data

8.3.5.2.1 Waveform Sequencer

The waveform sequencer queues waveform identifiers for playback. Eight sequence registers queue up to eight

waveforms for sequential playback. A waveform identifier is an integer value referring to the index position of a

waveform in the RAM library. Playback begins at register address 0x04 when the user asserts the GO bit

(register 0x0C). When playback of that waveform ends, the waveform sequencer plays the waveform identifier

held in register 0x05 if the next waveform is non-zero. The waveform sequencer continues in this way until it

reaches an identifier value of zero or until all eight identifiers are played (register addresses 0x04 through 0x0B),

whichever scenario is reached first.

The waveform identifier range is 1 to 127. The MSB of each sequence register can implement a delay between

sequence waveforms. When the MSB is high, bits [6:0] indicate the length of the wait time. The wait time for that

step then becomes WAV_FRM_SEQ[6:0] × 10 ms.