Intel FPGA时序约束深度解析与优化策略

需积分: 34 168 浏览量

更新于2024-08-06

收藏 557KB DOC 举报

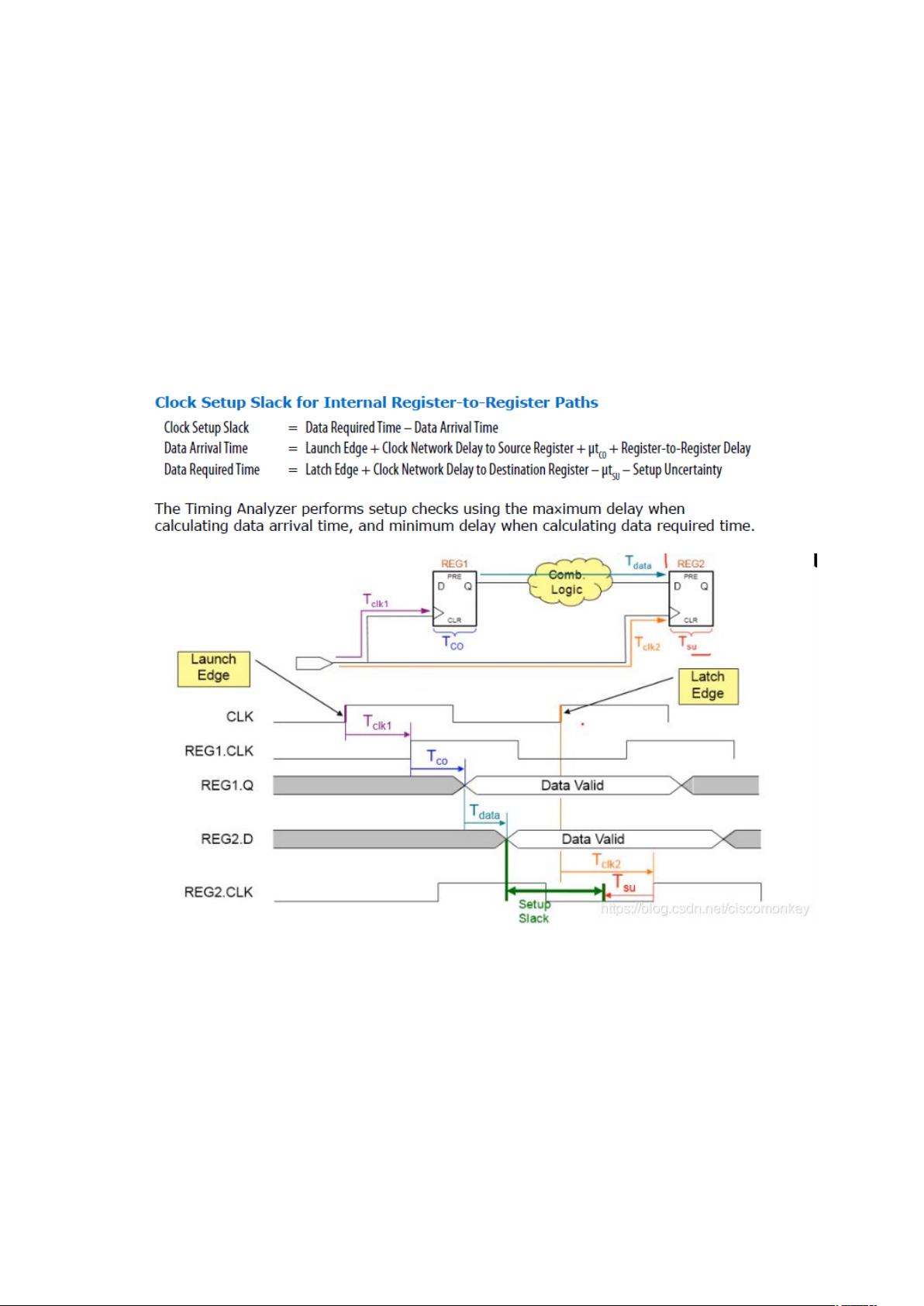

"本文是关于Intel FPGA时序约束解决方案的详细说明,主要涵盖TimeQuest工具的使用、时序分析的基本概念以及如何通过公式计算时序余量。文章旨在帮助读者理解并掌握时序约束,包括setup slack和hold slack的含义,以及它们在不同模型(如slow和fast)下的影响。此外,还介绍了Chip Planner中的布线布局和时钟路径的优化,强调使用专门的时钟管脚以减少clock skew。通过具体的计算题,作者展示了如何根据时钟周期、建立时间和保持时间计算时序余量。"

Intel FPGA时序约束是确保设计满足速度性能要求的关键步骤。设计者需要对时序分析有深入的理解,以优化设计性能。在TimeQuest这个时序分析工具中,选择不同的模型(如slow或fast)会对setup slack和hold slack产生影响。选择slow模型会更关注setup timing,而fast模型则对hold timing有较大影响。

时序分析主要包括两个关键指标:建立时间(setup time)和保持时间(hold time)。建立时间是指数据必须在时钟边沿到来之前稳定的时间,以确保正确捕获;保持时间是指数据在时钟边沿之后必须保持稳定的时间。这两个参数与时钟周期、时钟路径延迟和数据路径延迟密切相关。

Chip Planner是Intel FPGA设计中用于布线和逻辑分配的工具。它显示了FPGA内部的资源使用情况,如LAB(Logic Array Block)的分布和LE(Logic Element)的使用。通过合理布局,可以优化时钟路径,减少时钟 skew,从而提高时序性能。

计算时序余量是时序分析的重要部分。文章提供的计算题演示了如何根据给定的时钟延迟、数据路径延迟和时序要求(Tsetup和Thold)来计算setup slack和hold slack。这些计算可以帮助设计者了解设计是否满足时序约束,以及需要进行哪些优化。

理解并应用这些知识点对于成功地进行Intel FPGA设计至关重要。通过不断的实践和学习,设计师可以更好地掌握时序约束,从而提升FPGA设计的性能和可靠性。本文作为系列的总结,为读者提供了关于时序约束的实用知识和技巧,为进一步深入学习如IO约束等其他高级主题奠定了基础。

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

weixin_38604330

- 粉丝: 6

- 资源: 950

最新资源

- HPUX 11i V3系统管理员指南

- DIV+CSS布局大全

- J2EE 设计开发编程

- Serial ATA 2.6 Specification

- ITIL-white

- 《LINUX与UNIX SHELL编程指南》读书笔记

- 单源最短路径问题的Dijkstra算法

- Oracle 10g R2 Concepts双语版

- 02 第四章 使用SQL语句.pdf

- spring2.5 reference

- API函数大全(32 Bit Section PowerBuilder API)

- 51汇编指令表,一目了然,希望大家多多交流学习

- Serial ATA Specification Rev. 2.5

- 01 第一~三章.pdf

- asp.net速成教程

- Understanding JTA