直接晶体管级布局优化数字块

需积分: 14 19 浏览量

更新于2024-07-19

收藏 6.96MB PDF 举报

"Direct Transistor-Level Layout for Digital Blocks" 是一本由 Prakash Gopalakrishnan 和 Roba Rutenbar 合著的书籍,专注于探讨如何直接在晶体管层面进行数字块的布局设计。这本书主要讨论了传统标准单元库设计的高成本问题,以及尝试通过直接在晶体管级进行布局来优化小型设计的方法。

在传统的数字集成电路设计流程中,通常包括以下步骤:

a) RTL(寄存器传输级)网表,采用 Verilog 这样的硬件描述语言进行描述,并通过 Modelsim 进行仿真验证。

b) 合成阶段,使用工具如 DC Compiler 将 RTL 转换为门级逻辑。

c) 在 Cadence Virtuoso 等布局布线工具中导入门级网表,进一步优化布局。

d) 使用 Nanotime 和 SPICE 进行时序验证和电路模拟。

然而,直接在晶体管级进行布局面临着巨大的挑战,尤其是时序问题。由于缺乏专门处理这种布局的商业工具,因此需要设计者具备广泛的技能,包括RTL、物理设计(PD)和标准单元团队的专业知识。这种集成式方法在业界通常是分部门进行的,增加了实施难度。尽管如此,为了实现更优的设计,尤其是对于较小规模的设计,这种方法的探索是必要的。

提到的 nangate.com 公司尝试了类似的方法,但其生成的细粒度单元数量众多,导致对Synopsys库的时序特性进行表征变得极其耗时,这不是一个理想的选择。

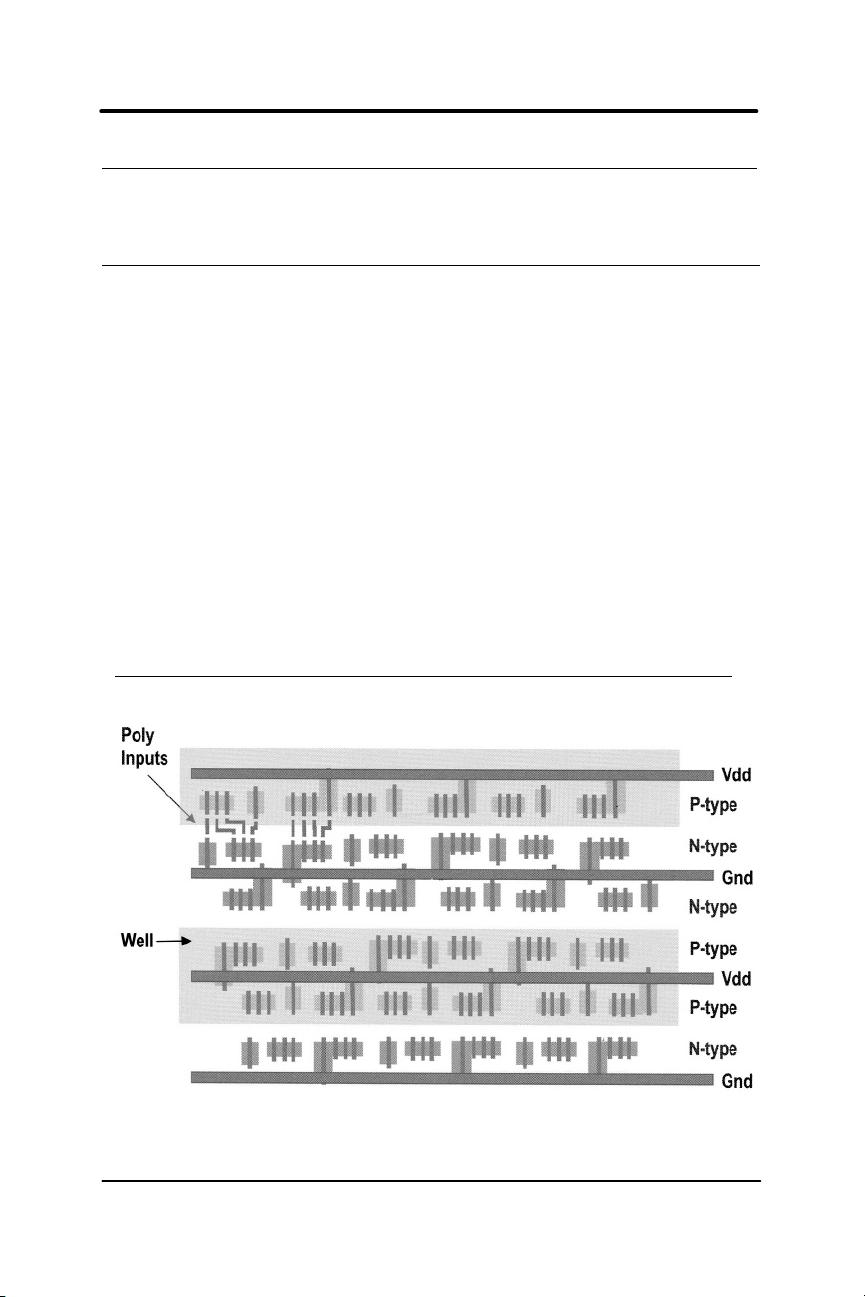

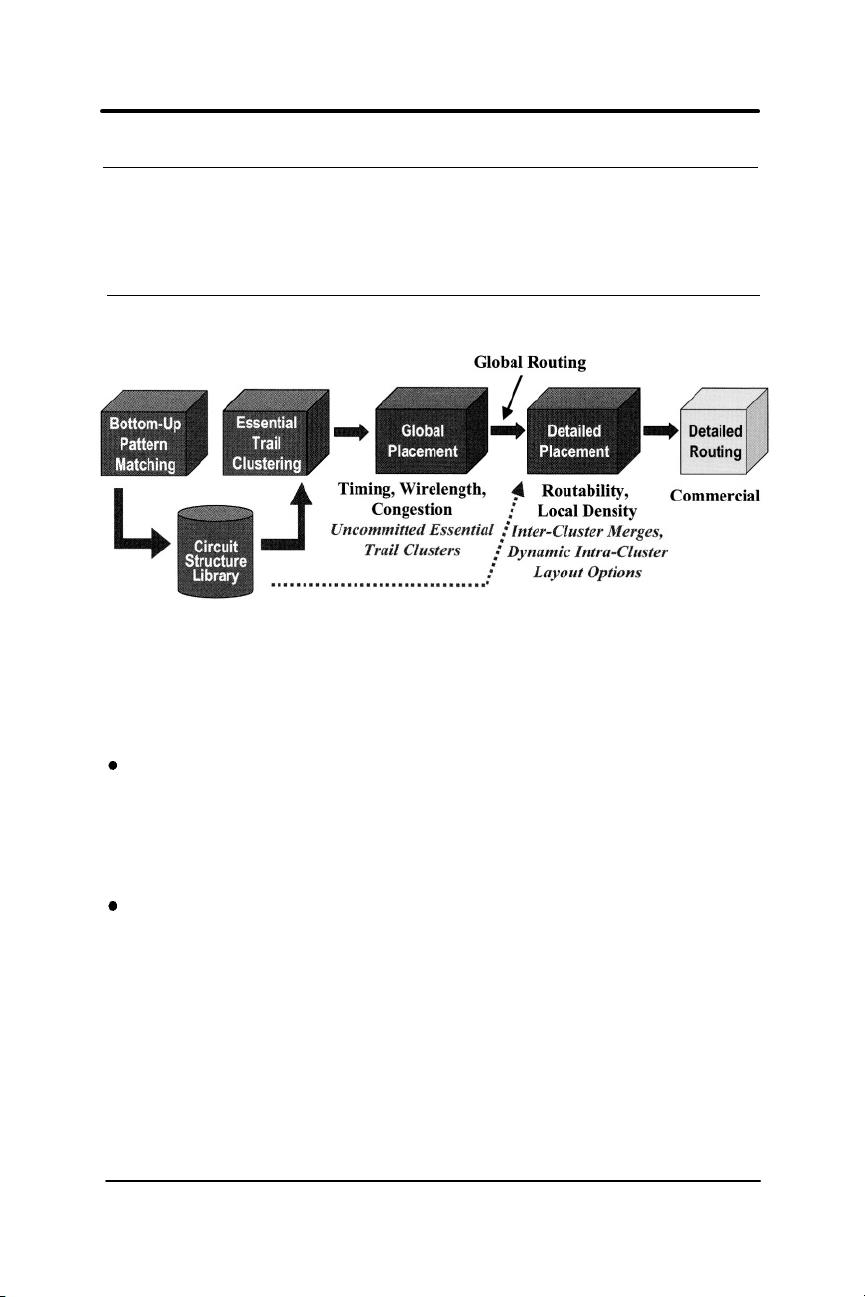

书中介绍了电路结构和聚类(Clustering)的概念,包括:

- 动机:对比标准单元和晶体管级设计的优势与局限

- 设计目标

- 前期晶体管级设计方法

- 整体策略

- 书籍大纲

作者还讨论了“Trails”和“Essential Cells”等概念,这些都是在晶体管级布局中关键的考虑因素。这些内容旨在提供一种更高效、更直接的方法来创建和优化数字电路的布局,以克服标准单元库设计的局限性。

"Direct Transistor-Level Layout for Digital Blocks" 提供了一种创新的视角,挑战了传统的IC设计流程,试图通过直接在晶体管级进行布局来提高效率和性能,尤其是在小型设计中。然而,这种方法需要高度的技术专长,并且目前缺乏相应的商业化工具支持,这使得实际应用面临挑战。

2019-05-23 上传

点击了解资源详情

点击了解资源详情

2021-02-08 上传

2022-07-15 上传

2021-02-09 上传

2021-02-23 上传

2021-05-24 上传

deepblue0755

- 粉丝: 7

- 资源: 97

最新资源

- Angular实现MarcHayek简历展示应用教程

- Crossbow Spot最新更新 - 获取Chrome扩展新闻

- 量子管道网络优化与Python实现

- Debian系统中APT缓存维护工具的使用方法与实践

- Python模块AccessControl的Windows64位安装文件介绍

- 掌握最新*** Fisher资讯,使用Google Chrome扩展

- Ember应用程序开发流程与环境配置指南

- EZPCOpenSDK_v5.1.2_build***版本更新详情

- Postcode-Finder:利用JavaScript和Google Geocode API实现

- AWS商业交易监控器:航线行为分析与营销策略制定

- AccessControl-4.0b6压缩包详细使用教程

- Python编程实践与技巧汇总

- 使用Sikuli和Python打造颜色求解器项目

- .Net基础视频教程:掌握GDI绘图技术

- 深入理解数据结构与JavaScript实践项目

- 双子座在线裁判系统:提高编程竞赛效率