没有合适的资源?快使用搜索试试~ 我知道了~

首页IEEE Journal of Solid-State Circuits: Transistor-Level IC Design and Peer Reviewed Papers

IEEE Journal of Solid-State Circuits: Transistor-Level IC Design...

需积分: 4 1 下载量 180 浏览量

更新于2024-07-16

收藏 124.08MB PDF 举报

"这篇文章来自于《IEEE固态电路期刊》(JSSC-2019-6),这是一本专注于固态电路领域的专业期刊,特别是针对晶体管级集成电路设计的探讨。期刊遵循IEEE PSPB操作手册中的同行评审要求,采用单盲评审方式,确保文章质量。2019年6月刊的部分内容包括了几篇研究论文,涉及数字三相调制发射器、宽带射频前端、植入式脑机接口系统的低功耗微波无线电收发器、多环控制交流耦合电源调制器以及低抖动多频率发生器等技术。"

在《IEEE固态电路期刊》2019年6月刊中,文章涉及了多个关键知识点:

1. 数字三相调制发射器:Lemberg等人介绍了一款工作在1.5到1.9 GHz的全数字三相调制发射器,其集成了一个多级类D功率放大器,实现了100 MHz的射频带宽。这项技术在无线通信系统中至关重要,因为它可以提高频率利用率和信号传输效率。

2. 宽带射频前端:Rasekhand和Bakhtiar提出了一种用于无SAW接收器的宽带射频前端,利用主动反馈和远超出带阻挡器抑制电路,显著提升了信号处理能力和干扰抑制能力,这对于现代无线通信设备的性能提升具有重要意义。

3. 植入式脑机接口系统的低功耗微波无线电收发器:Lee等人展示了一款采用供电调制节能技术的CMOS微型无线电收发器,专门应用于植入式脑机接口系统。这种设计考虑了生物兼容性和低功耗的需求,对于神经科学和医疗技术领域的发展有重大贡献。

4. 多环控制交流耦合电源调制器:Liu等人介绍的这种调制器结合了模式切换的CMOS功率放大器,用于能量回收系统,并具有包络成形功能。这种调制技术能提高能源效率,尤其适用于能量受限的无线通信系统。

5. 低抖动注入锁定多频率发生器:Yoon等人利用数字控制振荡器和时间交错校准方法开发出一款紧凑型双频注入锁定多频率发生器。这种发生器能减少抖动,提高时钟精度,对高精度数据传输和采样系统非常有用。

这些技术的介绍展示了当前固态电路和集成电路设计领域的最新进展,涵盖了从高频通信到低功耗生物医学应用等多个重要方向。通过这些技术,我们可以预见未来通信、医疗和物联网设备将更加高效、智能和可靠。

1810 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 54, NO. 6, JUNE 2019

[4] S. Lee et al., “A 128 Gb 2b/cell NAND flash memory in 14 nm

technology with tPROG=640 µs and 800 MB/s I/O rate,” in IEEE Int.

Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, San Francisco,

CA, USA, Jan./Feb. 2016, pp. 138–139.

[5] S. Lee, “Scaling challenges in NAND flash device toward 10nm technol-

ogy,” in Proc. 4th IEEE Int. Memory Workshop, Milan, Italy, May 2012,

pp. 1–4.

[6] K. Takeuchi, “Scaling challenges of NAND flash memory and hybrid

memory system with storage class memory & NAND flash memory,” in

Proc. IEEE Custom Int. Circuits Conf., San Jose, CA, USA, Sep. 2013,

pp. 1–6.

[7] Y. Fukuzumi et al., “Optimal integration and characteristics of ver-

tical array devices for ultra-high density, bit-cost scalable flash

memory,” in IEDM Tech. Dig., Washington, DC, USA, Dec. 2007,

pp. 449–452.

[8] K.-T. Park et al., “Three-dimensional 128 Gb MLC vertical nand

flash memory with 24-WL stacked layers and 50 MB/s high-

speed programming,” IEEE J. Solid-State Circuits, vol. 50, no. 1,

pp. 204–213, Jan. 2015.

[9] R. Micheloni, S. Aritome, and L. Crippa, “Array architectures for 3-D

NAND flash memories,” Proc. IEEE, vol. 105, no. 9, pp. 1634–1649,

Sep. 2017.

[10] T. Tanaka et al., “A 768Gb 3b/cell 3D-floating-gate NAND

flash memory,” in IEEE Int. Solid-State Circuits Conf. (ISSCC)

Dig. Tech. Papers, San Francisco, CA, USA, Jan./Feb. 2016,

pp. 142–143.

[11] R. Yamashita et al., “A 512Gb 3b/cell flash memory on 64-word-

line-layer BiCS technology,” in IEEE Int. Solid-State Circuits Conf.

(ISSCC) Dig. Tech. Papers, San Francisco, CA, USA, Feb. 2017,

pp. 196–197.

[12] C. Kim et al., “A 512Gb 3b/cell 64-stacked WL 3D V-NAND flash

memory,” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech.

Papers, San Francisco, CA, USA, Feb. 2017, pp. 202–203.

[13] H.-J. Kang et al., “Comprehensive analysis of retention characteristics

in 3-D NAND flash memory cells with tube-type poly-Si channel

structure,” in Proc. Symp. VLSI Technol., Kyoto, Japan, Jun. 2015,

pp. T182–T183.

[14] D. Oh et al., “TCAD simulation of data retention characteristics of

charge trap device for 3-D NAND flash memory,” in Proc. IEEE

Int. Memory Workshop (IMW), Monterey, CA, USA, May 2015,

pp. 1–4.

[15] B. Choi et al., “Comprehensive evaluation of early retention (fast charge

loss within a few seconds) characteristics in tube-type 3-D NAND flash

memory,” in Proc. IEEE Symp. VLSI Technol., Honolulu, HI, USA,

Jun. 2016, pp. 1–2.

[16] K. Mizoguchi, T. Takahashi, S. Aritome, and K. Takeuchi, “Data-

retention characteristics comparison of 2D and 3D TLC NAND flash

memories,” in Proc. IEEE Int. Memory Workshop, Monterey, CA, USA,

May 2017, pp. 1–4.

[17] K. Mizoguchi, S. Kotaki, Y. Deguchi, and K. Takeuchi, “Lateral charge

migration suppression of 3D-NAND flash by vth nearing for near data

computing,” in IEDM Tech. Dig., San Francisco, CA, USA, Dec. 2017,

pp. 19.2.1–19.2.4.

[18] T. Nakamura, Y. Deguchi, and K. Takeuchi, “AEP-LDPC ECC with error

dispersion coding for burst error reduction of 2D and 3D NAND flash

memories,” in Proc. IEEE Int. Memory Workshop (IMW), Monterey, CA,

USA, May 2017, pp. 1–4.

[19] C. Zambelli et al., “Characterization of TLC 3D-NAND flash endurance

through machine learning for LDPC code rate optimization,” in

Proc. IEEE Int. Memory Workshop, Monterey, CA, USA, May 2017,

pp. 1–4.

[20] Y. Lee, H. Yoo, J. Jung, J. Jo, and I.-C. Park, “A 2.74-pJ/bit, 17.7-Gb/s

iterative concatenated-BCH decoder in 65-nm CMOS for NAND flash

memory,” IEEE J. Solid-State Circuits, vol. 48, no. 10, pp. 2531–2540,

Oct. 2013.

[21] G. Dong, N. Xie, and T. Zhang, “On the use of soft-decision error-

correction codes in nand flash memory,” IEEE Trans. Circuits Syst. I,

Reg. Papers, vol. 58, no. 2, pp. 429–439, Feb. 2011.

[22] C.-L. Chen, K.-S. Lin, H.-C. Chang, W.-C. Fang, and C.-Y. Lee,

“A 11.5-Gbps LDPC decoder based on CP-PEG code con-

struction,” in Proc. ESSCIRC, Athens, Greece, Sep. 2009,

pp. 412–415.

[23] C. Matsui, R. Kinoshita, and K. Takeuchi, “Analysis on applicable error-

correcting code strength of storage class memory and NAND flash in

hybrid storage,” Jpn. J. Appl. Phys., vol. 57, no. 4S, Feb. 2018, Art.

no. 04FE01.

[24] S. Tanakamaru, Y. Yanagihara, and K. Takeuchi, “Error-prediction

LDPC and error-recovery schemes for highly reliable solid-state drives

(SSDs),” IEEE J. Solid-State Circuits, vol. 48, no. 11, pp. 2920–2933,

Nov. 2013.

[25] T. Tokutomi, M. Doi, S. Hachiya, A. Kobayashi, S. Tanakamaru, and

K. T. Vi, “Enterprise-grade 6x fast read and 5x highly reliable SSD with

TLC NAND-flash memory for big-data storage,” in IEEE Int. Solid-State

Circuits Conf. (ISSCC) Dig. Tech. Papers, San Francisco, CA, USA,

Feb. 2015, pp. 1–3.

[26] C. A. Aslam, Y. L. Guan, and K. Cai, “Retention-aware belief-

propagation decoding for NAND flash memory,” IEEE Trans.

Circuits Syst. II, Exp. Briefs, vol. 64, no. 6, pp. 725–729,

Jun. 2017.

[27] T. Takahashi, S. Yamazaki, and K. Takeuchi, “Data-retention time

prediction of long-term archive SSD with flexible-nLC NAND flash,”

in Proc. IEEE Int. Rel. Phys. Symp. (IRPS), Pasadena, CA, USA,

Apr. 2016, pp. 6C-5-1–6C-5-6.

[28] OpenFace. Accessed: Mar. 4, 2019. [Online]. Available:

https://cmusatyalab.github.io/openface/

[29] Y. Li et al., “128 Gb 3b/cell NAND Flash Memory in 19 nm technology

with 18 MB/s write rate and 400 Mb/s toggle mode,” in Proc. IEEE

Int. Solid-State Circuits Conf., San Francisco, CA, USA, Feb. 2012,

pp. 436–437.

[30] J.-W. Im et al., “A 128 Gb 3b/cell V-NAND flash memory with 1 Gb/s

I/O rate,” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech.

Papers, San Francisco, CA, USA, Feb. 2015, pp. 1–3.

[31] S. Tanakamaru, C. Hung, and K. Takeuchi, “Highly reliable and low

power SSD using asymmetric coding and stripe bitline-pattern elim-

ination programming,” IEEE J. Solid-State Circuits, vol. 47, no. 1,

pp. 85–96, Jan. 2012.

[32] Y. Deguchi, A. Kobayashi, H. Watanabe, and K. Takeuchi, “Flash

reliability boost Huffman coding (FRBH): Co-optimization of data

compression and V

th

distribution modulation to enhance data-retention

time by over 2900x,” in Proc. Symp. VLSI Technol., Kyoto, Japan,

Jun. 2017, pp. T206–T207.

[33] Y. Deguchi and K. Takeuchi, “Word-line batch V

th

modulation of TLC

NAND flash memories for both write-hot and cold data,” in Proc.

IEEE Asian Solid-State Circuits Conf. (A-SSCC), Seoul, South Korea,

Nov. 2017, pp. 161–164.

[34] N. P. Jouppi et al., “In-datacenter performance analysis of a tensor

processing unit,” in Proc. ACM/IEEE 44th Annu. Int. Symp. Comput.

Archit. (ISCA), Toronto, ON, Canada, Jun. 2017, pp. 1–12.

[35] Z. Cai, X. He, J. Sun, and N. Vasconcelos, “Deep learning with low

precision by half-wave Gaussian quantization,” in Proc. IEEE Conf.

Comput. Vis. Pattern Recognit. (CVPR), Honolulu, HI, USA, Jul. 2017,

pp. 5406–5414.

Yoshiaki D eguch i (M’17) received the B.E. and

M.E. degrees from the Department of Electrical,

Electric, and Communication Engineering, Chuo

University, Tokyo, Japan, in 2016 and 2018,

respectively.

He is currently a Visiting Researcher with Chuo

University. He is also currently with Hitachi

Ltd. Research and Development Group, Yokohama,

Japan. He has been engaged in research on reliabil-

ity enhancement techniques, error-correcting codes

(ECCs), data compression techniques, and approxi-

mate computing for

NAND flash memory-based SSD.

Toshiki Nakamura received the B.E. degree from

the Department of Electrical, Electric, and Com-

munication Engineering, Chuo University, Tokyo,

Japan, in 2017, where he is currently pursuing the

M.S. degree.

He has been engaged in a research on reliability

of

NAND flash memory.

DEGUCHI et al.: 3-D NAND FLASH VALUE-AWARE SSD 1811

Atsuna Hayakawa received the B.E. degree from

the Department of Electrical, Electric, and Com-

munication Engineering, Chuo University, Tokyo,

Japan, in 2017, where she is currently pursuing the

M.S. degree.

She has been engaged in the research on reliability

of resistive random access memory (ReRAM).

Ken Takeuchi (M’01) received the B.S. and M.S.

degrees in applied physics from the University of

Tokyo, Tokyo, Japan, in 1991 and 1993, respec-

tively, the M.B.A. degree from Stanford University,

Stanford, CA, USA, in 2003, and the Ph.D. degree

in electric engineering from the University of Tokyo

in 2006.

In 1993, he joined Toshiba, Yokohama, Japan,

where he led Toshiba’s

NAND flash memory circuit

design. From 2007 to 2012, he was an Associate

Professor with the Department of Electrical Engi-

neering and Information Systems, Graduate School of Engineering, University

of Tokyo. In 2012, he joined Chuo University, Tokyo, Japan, where he is

currently a Professor with the Department of Electrical, Electronic, and

Communication Engineering, Faculty of Science and Engineering. He is

currently involved in the database storage system for big-data application,

VLSI circuit design, signal processing, and device such as the emerging

non-volatile memories, 3-D integrated SSDs, low-power 3D-LSI circuits, and

ultralow-voltage SRAMs. He designed six world’s highest density

NAND flash

memory products such as 0.7um 16Mbit, 0.4um 64Mbit, 0.25um 256Mbit,

0.16um 1Gbit, 0.13um 2Gbit, and 56nm 8Gbit

NAND flash memories. He

has authored numerous technical papers. He holds 228 patents worldwide

including 124 U.S. patents. In particular, he invented the multipage cell

architecture, which was presented at the Symposium on VLSI Circuits in 1997.

He successfully commercialized the world’s first multi-level cell

NAND flash

memory in 2001.

Dr. Takeuchi was a recipient of the Takuo Sugano Award for Outstanding

Paper at International Solid-State Circuits Conference (ISSCC) 2007. He

served on the program committee member of ISSCC, Symposium on VLSI

Circuits, Custom Integrated Circuits Conference (CICC), Asian Solid-State

Circuits Conference (A-SSCC), International Reliability Physics Symposium

(IRPS), International Memory Workshop (IMW), International Conference

on Solid State Devices and Materials (SSDM), and Non-Volatile Memory

Technology Symposium (NVMTS). He served as a Tutorial Speaker at ISSCC

2008, a Forum Speaker at ISSCC 2015, an SSD Forum Organizer at ISSCC

2009, a 3D-LSI Forum Organizer at ISSCC 2010, an Ultralow Voltage LSI

Forum Organizer at ISSCC 2011, and a Robust VLSI System Forum Organizer

at ISSCC 2012. He serves as a Program Chair of Symposium on VLSI

Circuits.

1648 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 54, NO. 6, JUNE 2019

A 0.4-V 13-bit 270-kS/s SAR-ISDM ADC With

Opamp-Less Time-Domain Integrator

Sung-En Hsieh and Chih-Cheng Hsieh

Abstract—This paper presents a 13-bit high-resolution two-

step analog-to-digital converter (ADC). Successive approximation

register (SAR)-ADCs and an incremental sigma-delta modula-

tor (ISDM) act as the coarse and fine ADCs, respectively. By using

the proposed time-domain ISDM, the integrator is relaxed from

the finite gain error and static current consumption. For the

matching of the capacitive digital-to-analog converter(CDAC),

the integral non-linearity (INL) splitting (INLS) switching proce-

dure is developed to reduce the INL and switching energy to 25%

and 9% of the reference common-mode voltage (VCM)-based

scheme, respectively. With a reduced capacitance of the capacitor

array, the requirements of the input driver and reference buffer

are effectively relaxed. A prototype was fabricated in Taiwan

Semiconductor Manufacturing Company (TSMC) 90-nm CMOS

technology, which occupies an area of 0.059 mm

2

. The achieved

spurious-free dynamic range (SFDR) and signal-to-noise and

distortion ratio (SNDR) at Nyquist rate are 90.38 and 73.57 dB,

respectively. The maximum differential non-linearity (DNL) and

INL are 0.45 and 0.75 LSB, respectively. The prototype consumes

638 nW at 0.4-V supply and 270-kHz sampling rate. The resultant

Schreier figure of merit (FoM) is 186.8 dB, and the Walden FoM

is 0.61 fJ/conversion step.

Index Terms— High resolution, incremental sigma-delta mod-

ulator (ISDM), low power, successive approximation register

analog-to-digital converter (SAR-ADC).

I. INTRODUCTION

T

HE Internet-of-Things (IoT) refers to the ever-growing

network of physical devices which continuously monitor

environmental conditions, such as temperature, light, sound,

and so on. To guarantee its long-term operation, low-power

analog-to-digital converters (ADCs) are needed. Recently, suc-

cessive approximation register (SAR) ADCs show convincing

low-power performance with advanced technology since they

are mostly composed of digital circuits. However, as the noise

performance of a comparator scales with the square of the

energy consumption, the power efficiency of ADCs is limited.

Furthermore, an additional 1-bit improvement for an ADC’s

linearity requires fourfold capacitance on the SAR ADC’s

capacitor array. Thus, high resolution and low power [1] are

hard to achieve simultaneously.

Recent studies [2]–[6] show a convincing performance with

advanced switching procedures. However, with the improved

capacitive digital-to-analog converter’s (CDAC’s) switching

Manuscript received August 19, 2018; revised November 5, 2018 and

January 5, 2019; accepted January 12, 2019. Date of publication February 14,

2019; date of current version May 24, 2019. This paper was approved by

Associate Editor Jeffrey Gealow. (Corresponding author: Chih-Cheng Hsieh.)

The authors are with the Department of Electrical Engineering,

National Tsing-Hua University, Hsinchu 31003, Taiwan (e-mail: cchsieh@

ee.nthu.edu.tw).

Color versions of one or more of the figures in this paper are available

online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2019.2894998

energy, the achievable resolution may be still limited by

the CDAC matching. To increase the matching performance,

the digital fore-ground calibration [7], [8] is widely applied

with penalties of a complex adder and synthesized logic for

reconstructing the corresponding radix. The direct switching

procedure [9] and the input-range-adaptive switching pro-

cedure [10] use align switching at the fine conversion to

omit the unnecessary trial-and-error CDAC switching and

increase the matching performance. By splitting the CDAC,

the re-switching technique [11] further improves the matching

performance. However, both align-switching and re-switching

techniques still achieve a limited matching performance.

For thermal noise reduction, the bi-directional comparator

[12] and the cascade-input comparator [13] use low-power

and high-gain pre-amplifiers, respectively. This efficiently

reduces the noise with a tolerable power penalty for all bit

conversions. To further save power, the voltage-controlled

oscillator (VCO) of the adaptive time-domain comparator [14]

only oscillates and reduces noise at critical bit comparisons.

However, multiple low-noise and high-power comparisons are

still required, which limits the power efficiency. With static

current consumption (opamp) and a digital filter [a decima-

tion filter for incremental sigma-delta modulator (ISDM)],

the SDM [15] achieves ultralow thermal noise. An integrator

using the passive summing technique without an opamp was

reported [16]. However, the gain loss issue changes the noise

transfer function (NTF) and degrades the effective resolution.

To increase the power efficiency of the comparator and

improve the matching performance, [17] presents an SAR-

ISDM (incremental-SDM) hybrid ADC with an integral non-

linearity (INL) splitting (INLS) switching CDAC and an

opamp-less time-domain integrator. Moreover, for many sensor

systems, its front-end sensors and ADCs inherently require

a high supply voltage, to maintain the operation and signal

swing. A low supply voltage is used for back-end dig-

ital circuits for the power reduction. To avoid the high

supply voltage by adopting the two sub-ADCs technique

[13], the INLS switching procedure handles the same input

voltage swing (±V

ref

) with a shared and reduced supply

voltage (V

dd

= 0.5 V

ref

) from the back-end circuit for

the power reduction, compared to conventional approaches

(V

dd

= V

ref

). By adopting the shifted-monotonic switching

(SMS) [18] and semi-resting (SR) [13], the achieved INL

of INLS is only 25% and 45% of the VCM-based switch-

ing procedure [4], [5] and the re-switching technique [11],

respectively. Furthermore, an ISDM using an opamp-less time-

domain integrator is proposed as the fine ADC to achieve an

ideal NTF without static current consumption. This reduces

0018-9200 © 2019 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission.

See http://www.ieee.org/publications_standards/publications/rights/index.html for more information.

HSIEH AND HSIEH: 0.4-V 13-bit 270-kS/s SAR-ISDM ADC 1649

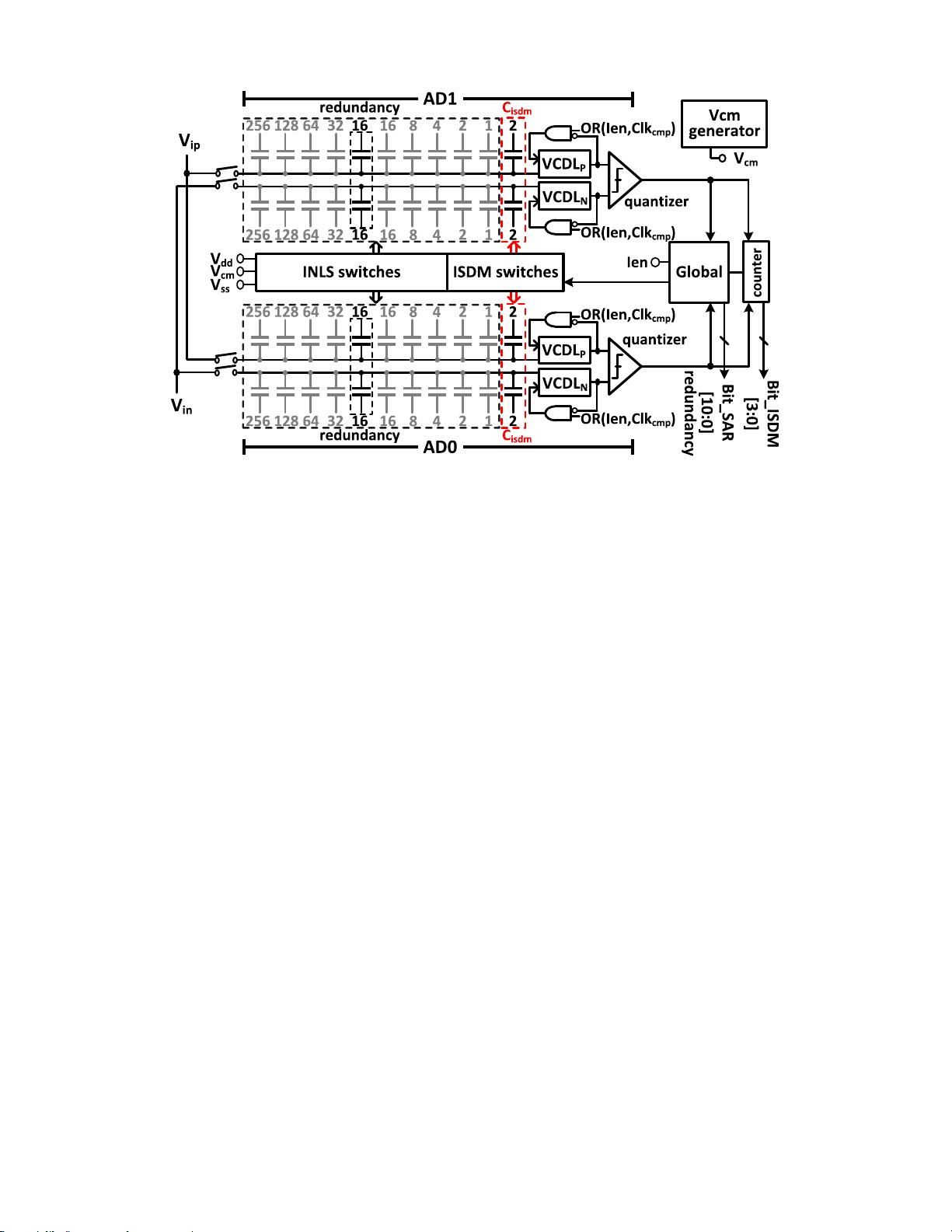

Fig. 1. Architecture of the proposed INLS switching procedure and time-domain ISDM.

the quantization noise and thermal noise by 4- and 2-bits,

respectively. Finally, the ISDM operation also avoids the

multiple high power and low noise bit conversions of an SAR

operation.

The rest of this paper is organized as follows. The arrange-

ments of V

LSB

between SAR and ISDM, requirements of the

reference buffer, and the matching performance of the capac-

itor array are discussed in Section II. Section III describes

calculations for the 4-bit ISDM operation and the VCM

inaccuracy. The voltage controlled delay line (VCDL’s) non-

ideal effects, the arrangement of the redundancy, and the

decision of the CDAC are also provided in Section III. Finally,

the measurement results and the conclusions are given in

Sections IV and V, respectively.

II. P

ROPOSED SAR ADC ARCHITECTURE

Fig. 1 shows the architecture of proposed SAR ADC with

the INLS switching procedure and time-domain ISDM. This

paper has two sub-ADCs (AD0 and AD1). Each sub-ADC

has two 9-bit capacitor arrays and two VCDLs to perform the

differential operation. By adopting the input range boosting

technique [13], AD1 and AD0 handle the input ranges of

0< V

ip

− V

in

< +2 V

dd

and −2V

dd

< V

ip

− V

in

< 0,

respectively, with an overall input range of −2 V

dd

< V

ip

−

V

in

< +2 V

dd

. Therefore, the single-ended voltage swing of

V

ip

and V

in

is 0 ∼ 2 V

dd

. One of the sub-ADC enters the

idle mode by detecting the polarity at the MSB conversion

to save power. The asynchronous logic [6] is shared by the

two sub-ADCs for power and area efficiency. For a sub-ADC,

the total capacitance (C

total

) of a single-ended capacitor array

(513 unit Cs) is 2.8 pF. With a careful layout, the gain loss

of the capacitor array is smaller than 3% without the need of

calibration on the gain mismatch between AD0 and AD1 [13].

This paper is composed of 11-bit SAR and 4-bit ISDM

ADCs for the coarse and fine conversions, respectively,

to achieve a 13-bit ADC with a 2-bit redundancy.

At the coarse SAR conversion, the control “Ien” is set to 0 to

disable the oscillation. For each bit conversion, the VCDLs are

enabled and then reset without the oscillation by a comparator

clock (Clk

cmp

),whereClk

cmp

is generated from a conventional

SAR logic [6]. Thus, the VCDL serves as an open-loop pre-

amplifier for the quantizer. VCDL and the quantizer operate

as a comparator that decides the polarity for the 11-bit SAR

ADC conversions with the INLS switching procedure.

After the coarse SAR conversion, Clk

cmp

is disabled

(Clk

cmp

= 0), and the residue voltage remains on the top

plates of the capacitor arrays for the following fine ISDM

conversion. At the fine ISDM conversion, the VCDL turns

into a VCO as a time-domain integrator by setting Ien = 1to

enable the oscillation. To perform the 1-bit CDAC feedback

of ISDM conversion, the 2-unit C (C

isdm

= 2C) is toggled,

corresponding to the quantizer’s output after each time of

oscillation. After 16 times of the time-domain integration

[over-sampling ratio (OSR) = 16], the first-order noise

shaping with a quantization noise improvement of 24 dB

(4-bit resolution) is achieved without using a power-hungry

operational amplifier (op-amp).

For this prototype, only the VCDL mismatch between

AD0 and AD1 requires a calibration. From simulations,

the mismatch between AD0 and AD1 is 21 LSB from the

input-referred offset mismatch of VCDLs. A redundant 16C in

the CDAC is implemented to achieve an additional ±64 LSB

searching range, which provides an over three-sigma tolerance

of mismatch between the sub-ADCs by adopting the digital

foreground calibration procedure of SR [13].

To avoid the gain mismatch between the coarse and fine

ADCs,thecoarseandfineADCssharethesameDACs.

Compared to the coarse ADC which switches 1C with bottom-

plate voltage swing = V

dd

/2, the fine ADC switches 2C

with a twofold bottom-plate voltage swing [6]. Therefore,

the searching range of the 4-bit fine ADC (=16 V

LSB

) is equal

to 4 ×V

LSB_coarse

without the gain calibration.

1650 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 54, NO. 6, JUNE 2019

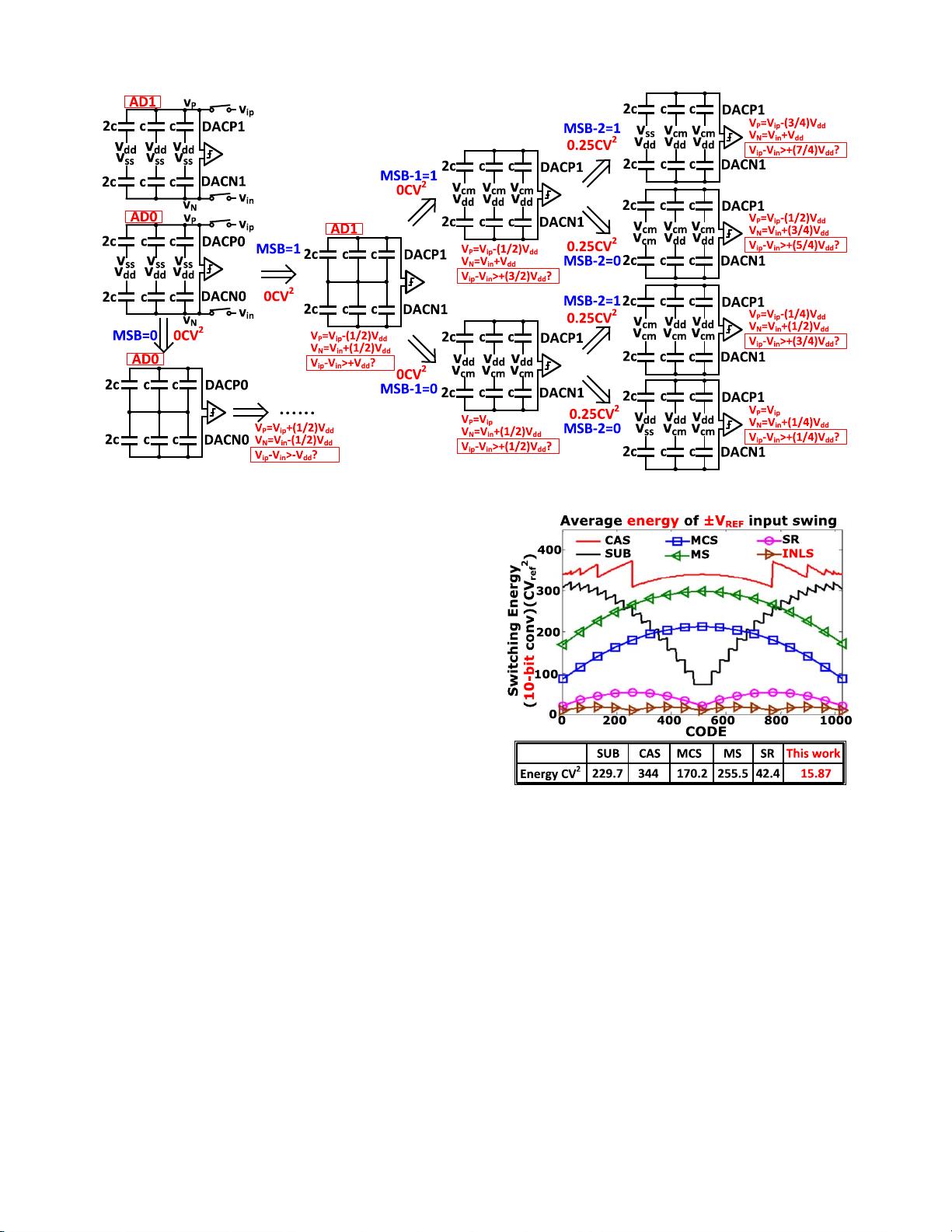

Fig. 2. 5-bit conversion example of the proposed INLS switching procedure.

Under the 0.4-V operation for low power consumption, the

double-boosted sample-and-hold (S/H) [13] and local-boosted

switches [3] are implemented for the linearity requirement and

leakage control. The sampling switches of AD0 and AD1 are

controlled by the same clock, which minimizes the timing

mismatch between the two sub-ADCs to a negligible level.

A. INL Splitting Switching Procedure

Fig. 2 shows a 5-bit pure SAR example of the proposed

INLS switching procedure with two sub-ADCs and 2-bit

CDACs. Note that 3-bit CDACs are required for a 5-bit

coarse SAR ADC if capacitor switching after the last-bit

conversion (residue voltage generation) for the coarse/fine ADs

operation is required. At the reset phase, the bottom plates of

DACP1/DACN1 and DACP0/DACN0 are reset to V

dd

/V

ss

and

V

ss

/V

dd

, respectively. If MSB = 1[(V

ip

− V

in

)>0], AD1

is chosen and the bottom plates of DACP1 and DACN1 are

merged together as V

cm

by the charge averaging operation. The

generated voltage shifts on DACP1 (V

P

) and DACN1 (V

N

) are

–V

dd

/2 and +V

dd

/2, respectively, with an overall differential

voltage shift (V

P

− V

N

) of –V

dd

for the MSB-1 conversion

[(V

ip−

V

in

)>+V

dd

or (V

ip−

V

in

)<+V

dd

]. In contrast, if

MSB = 0, AD1 is disabled for the power reduction, and AD0

handles the rest of the conversion. For the MSB-1 comparison,

if MSB-1 = 1, the differential voltage shift (V

P

− V

N

) of

–V

dd

/2 is accomplished by level shifting [18] the bottom

plate of DACN1 from V

cm

to V

dd

, to generate a voltage

shift of +V

dd

/2 on V

N

. In contrast, if MSB-1 = 0, the dif-

ferential voltage shift (V

P

− V

N

) of +V

dd

/2 is accomplished

by level shifting the bottom plate of DACP1 from V

cm

to

V

dd

, to generate a voltage shift of +V

dd

/2 on V

P

.Forthe

rest of the bit conversions, the monotonic switching (MS)

procedure [6] is adopted. If MSB-2 = 1, the bottom plate

of DACP1 is monotonically switched down from V

dd

to V

cm

(MSB-1 = 0) or from V

cm

to V

ss

(MSB-1 = 1), to generate

Fig. 3. Switching energy versus the output code.

the required differential voltage shift of –V

dd

/4. If MSB-2 = 0,

the bottom plate of DACN1 is monotonically switched down

from V

dd

to V

cm

(MSB-1 = 1) or from V

cm

to V

ss

(MSB-

1 = 0), to generate the required differential voltage shift of

+V

dd

/4. Note that inaccuracies of the merging operation and

V

cm

generation are covered by the ±70 LSB redundancy,

as described in Section III-D.

B. Switching Energy and Specification of Reference Buffer

For comparison, assume a 10-bit ADC has an identical

input range (±V

ref

) for the overall system and the same total

capacitance (2

10−1

C) for each sub-ADC. Fig. 3 shows the

switching energy of 10-bit ADCs versus the output codes

from a MATLAB simulation, including energy consumption

of the reset and conversion phases. By omitting the switching

energy of MSB and MSB-1 conversions and using a half

bottom plate’s voltage swing, the CDAC switching energy of

剩余313页未读,继续阅读

132 浏览量

119 浏览量

130 浏览量

132 浏览量

108 浏览量

2020-02-08 上传

117 浏览量

176 浏览量

129 浏览量

netshell

- 粉丝: 11

- 资源: 185

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功