DRV134/135: 高性能音频平衡线路驱动器详解

需积分: 9 149 浏览量

更新于2024-07-05

收藏 1.95MB PDF 举报

DRV134和DRV135是两款专门设计用于音频平衡线路驱动的集成电路,它们采用PDIP (双列直插封装)、SO-16以及SOL-16封装形式,旨在提供卓越的音频性能。这些设备的主要特点包括:

1. **平衡输出**:DRV134和DRV135作为差分输出放大器,能够将单端输入转换为一对平衡输出,确保信号在传输过程中减少噪声和失真。

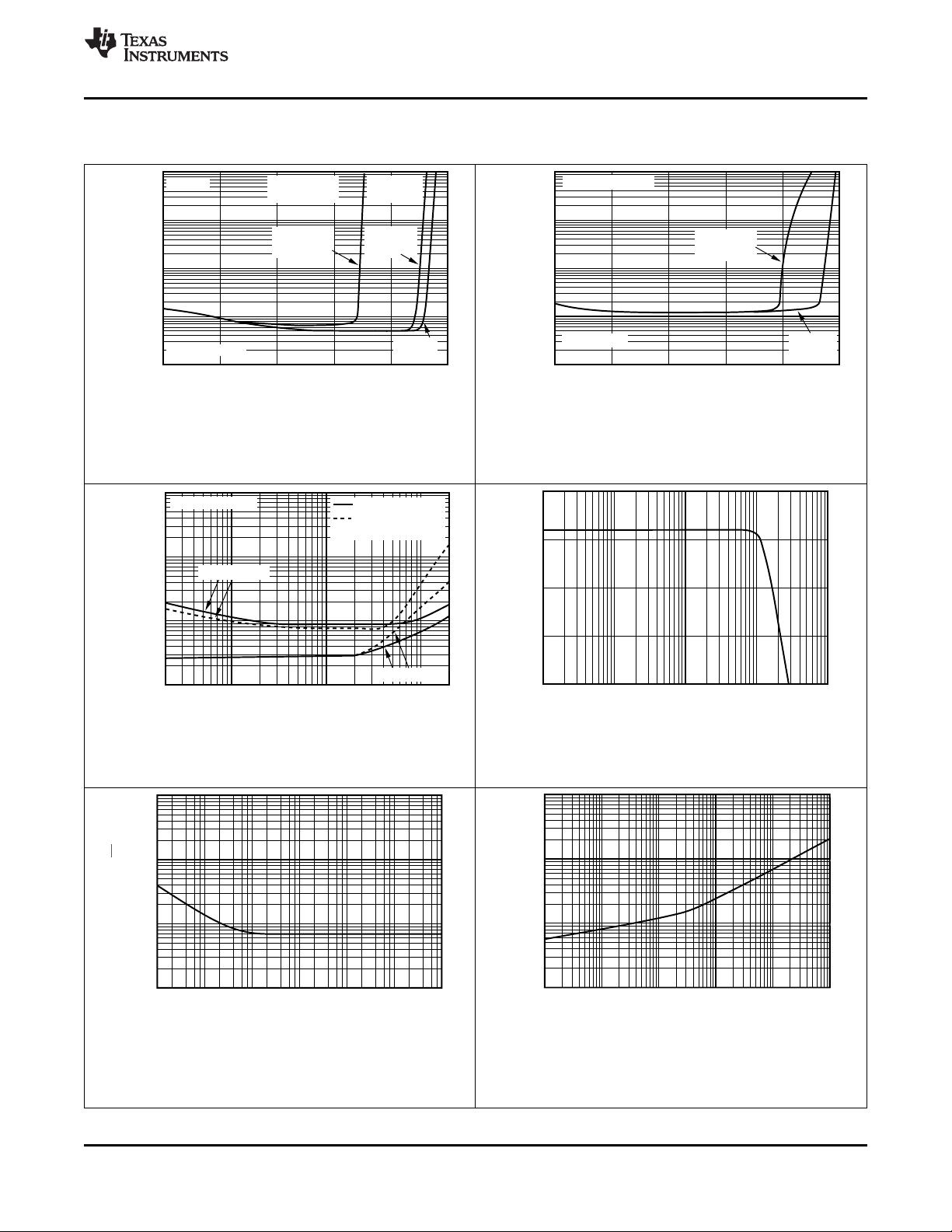

2. **低失真**:它们具有出色的线性特性,特别是在1kHz频率下,失真率低至0.0005%,这对于高保真音频应用至关重要。

3. **宽输出摆幅**:高达17Vrms的输出电压,能够在600Ω负载上实现,这意味着它们能够驱动各种阻抗的音频线路,提供了丰富的动态范围。

4. **高性能运算放大器**:内置高性能运算放大器,配备精密内部电阻,确保在音频应用中的稳定性和可靠性。

5. **高带宽**:由于高的 slew rate (15V/μs),这两个器件可以在音频频段内快速响应,保持良好的瞬态性能。

6. **低静态电流**:低的待机电流消耗,±5.2mA,有利于延长电池寿命,特别适合电池供电的设备。

7. **激光精确调谐**:芯片上的内部电阻通过激光精确校准,以确保准确的增益控制和最佳的输出共模抑制。

8. **多种封装选择**:提供的封装选项包括8针双列直插式(DIP)、SO-8和SOL-16,适应不同尺寸和电路布局的需求。

9. **广泛的电源范围**:工作电压非常宽广,可以从±4.5V到±18V,灵活性极高,可以适应各种电源环境。

10. **支持文档与工具**:产品提供样本、购买链接以及全面的技术文档、工具和软件,以及售后支持和社区资源,方便用户进行设计和调试。

这些特性使得DRV134和DRV135成为音频系统设计者在构建高质量音频设备时的理想选择,无论是对音质要求严格的音响设备,还是对于功耗敏感的便携式音频应用,都能发挥重要作用。

2022-05-03 上传

2018-11-07 上传

2023-05-23 上传

2023-07-14 上传

2023-03-14 上传

2024-05-23 上传

2023-07-16 上传

2023-07-16 上传

2023-07-13 上传

2023-06-08 上传

ltqshs

- 粉丝: 7w+

- 资源: 222

最新资源

- 解决本地连接丢失无法上网的问题

- BIOS报警声音解析:故障原因与解决方法

- 广义均值移动跟踪算法在视频目标跟踪中的应用研究

- C++Builder快捷键大全:高效编程的秘密武器

- 网页制作入门:常用代码详解

- TX2440A开发板网络远程监控系统移植教程:易搭建与通用解决方案

- WebLogic10虚拟内存配置详解与优化技巧

- C#网络编程深度解析:Socket基础与应用

- 掌握Struts1:Java MVC轻量级框架详解

- 20个必备CSS代码段提升Web开发效率

- CSS样式大全:字体、文本、列表样式详解

- Proteus元件库大全:从基础到高级组件

- 74HC08芯片:高速CMOS四输入与门详细资料

- C#获取当前路径的多种方法详解

- 修复MySQL乱码问题:设置字符集为GB2312

- C语言的诞生与演进:从汇编到系统编程的革命