没有合适的资源?快使用搜索试试~ 我知道了~

首页PHY Interface for the PCI Express Architecture Version 2.0

PHY Interface for the PCI Express Architecture Version 2.0

PHY Interface for the PCI Express Architecture Version 2.0

资源详情

资源评论

资源推荐

PHY Interface

for the

PCI Express

TM

Architecture

Version 2.00

©2007 Intel Corporation—All rights reserved.

PHY Interface for the PCI Express

TM

Architecture

©2007 Intel Corporation—All rights reserved. Page 2 of 38

Intellectual Property Disclaimer

THIS SPECIFICATION IS PROVIDED “AS IS” WITH NO WARRANTIES

WHATSOEVER INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS

FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING

OUT OF ANY PROPOSAL, SPECIFICATION, OR SAMPLE.

A COPYRIGHT LICENSE IS HEREBY GRANTED TO REPRODUCE AND

DISTRIBUTE THIS SPECIFICATION FOR INTERNAL USE ONLY. NO OTHER

LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY

OTHER INTELLECTUAL PROPERTY RIGHTS IS GRANTED OR INTENDED

HEREBY.

INTEL CORPORATION AND THE AUTHORS OF THIS SPECIFICATION DISCLAIM

ALL LIABILITY, INCLUDING LIABILITY FOR INFRINGEMENT OF

PROPRIETARY RIGHTS, RELATING TO IMPLEMENTATION OF INFORMATION

IN THIS DOCUMENT AND THE SPECIFICATION. INTEL CORPORATION AND

THE AUTHORS OF THIS SPECIFICATION ALSO DO NOT WARRANT OR

REPRESENT THAT SUCH IMPLEMENTATION(S) WILL NOT INFRINGE SUCH

RIGHTS.

ALL SUGGESTIONS OR FEEDBACK RELATED TO THIS SPECIFICATION

BECOME THE PROPERTY OF INTEL CORPORATION UPON SUBMISSION.

INTEL CORPORATION MAY MAKE CHANGES TO SPECIFICATIONS, PRODUCT

DESCRIPTIONS, AND PLANS AT ANY TIME, WITHOUT NOTICE.

Notice: Implementations developed using the information provided in this specification may

infringe the patent rights of various parties including the parties involved in the development of

this specification. No license, express or implied, by estoppel or otherwise, to any intellectual

property rights (including without limitation rights under any party’s patents) are granted herein.

This document is an intermediate draft for comment only and is subject to change without notice.

Readers should not design products based on this document.

All product names are trademarks, registered trademarks, or service marks of their respective

owners

Contributors

Jeff Morris Jim Choate

Andy Martwick Paul Mattos

Brad Hosler

Matthew Myers

PHY Interface for the PCI Express

TM

Architecture

©2007 Intel Corporation—All rights reserved. Page 3 of 38

Table of Contents

1 Preface...................................................................................................................................... 5

1.1 Scope of this Revision ...................................................................................................... 5

1.2 Revision History ............................................................................................................... 5

2 Introduction.............................................................................................................................. 6

2.1 PCI Express PHY Layer ................................................................................................... 7

3 PHY/MAC Interface ................................................................................................................ 7

4 PCI Express PHY Functionality............................................................................................... 9

4.1 Transmitter Block Diagram ............................................................................................ 10

4.2 Receiver Block Diagram................................................................................................. 11

4.3 Clocking.......................................................................................................................... 11

5 PIPE Interface Signal Descriptions........................................................................................ 12

5.1 PHY/MAC Interface Signals .......................................................................................... 12

5.2 External Signals .............................................................................................................. 15

6 PIPE Operational Behavior.................................................................................................... 17

6.1 Clocking.......................................................................................................................... 17

6.2 Reset................................................................................................................................ 17

6.3 Power Management ........................................................................................................ 17

6.4 Receiver Detection.......................................................................................................... 19

6.5 Transmitting a beacon..................................................................................................... 22

6.6 Detecting a beacon.......................................................................................................... 22

6.7 Clock Tolerance Compensation...................................................................................... 23

6.8 Error Detection................................................................................................................ 24

6.8.1 8B/10B Decode Errors............................................................................................. 24

6.8.2 Disparity Errors ....................................................................................................... 25

6.8.3 Elastic Buffer Errors................................................................................................ 25

6.9 Loopback ........................................................................................................................26

6.10 Polarity Inversion........................................................................................................ 28

6.11 Setting negative disparity............................................................................................ 28

6.12 Implementation specific timing................................................................................... 29

6.13 Control Signal Decode table........................................................................................ 31

6.14 Recommended synchronous signal timings ................................................................ 32

7 Sample Operational Sequences.............................................................................................. 32

7.1 Active PM L0 to L0s and back to L0.............................................................................. 32

7.2 Active PM to L1 and back to L0..................................................................................... 33

7.3 Receivers and Electrical Idle .......................................................................................... 34

8 Multi-lane PIPE...................................................................................................................... 37

PHY Interface for the PCI Express

TM

Architecture

©2007 Intel Corporation—All rights reserved. Page 4 of 38

Table of Figures

Figure 1: Partitioning PHY Layer ........................................................................................................ 6

Figure 2: PHY/MAC Interface............................................................................................................. 7

Figure 3: PHY Functional Block Diagram............................................................................................ 9

Figure 4: Transmitter Block Diagram ........................................................................................... 10

Figure 5: Receiver Block Diagram................................................................................................11

Figure 6: Clocking and Power Block Diagram ............................................................................. 11

Table of Tables

Table 5-1: Transmit Data Interface Signals................................................................................... 12

Table 5-2: Receive Data Interface Signals .................................................................................... 12

Table 5-3: Command Interface Signals......................................................................................... 13

Table 5-4: Status Interface Signals................................................................................................ 13

Table 5-5: External Signals ........................................................................................................... 15

PHY Interface for the PCI Express

TM

Architecture

©2007 Intel Corporation—All rights reserved. Page 5 of 38

1 Preface

1.1 Scope of this Revision

Version 2.00 of the PCI Express PHY Interface Specification has definitions of all functional

blocks and signals. This revision includes support for PCI Express

*

implementations conforming

to the PCI Express Base Specification, Revision 2.0.

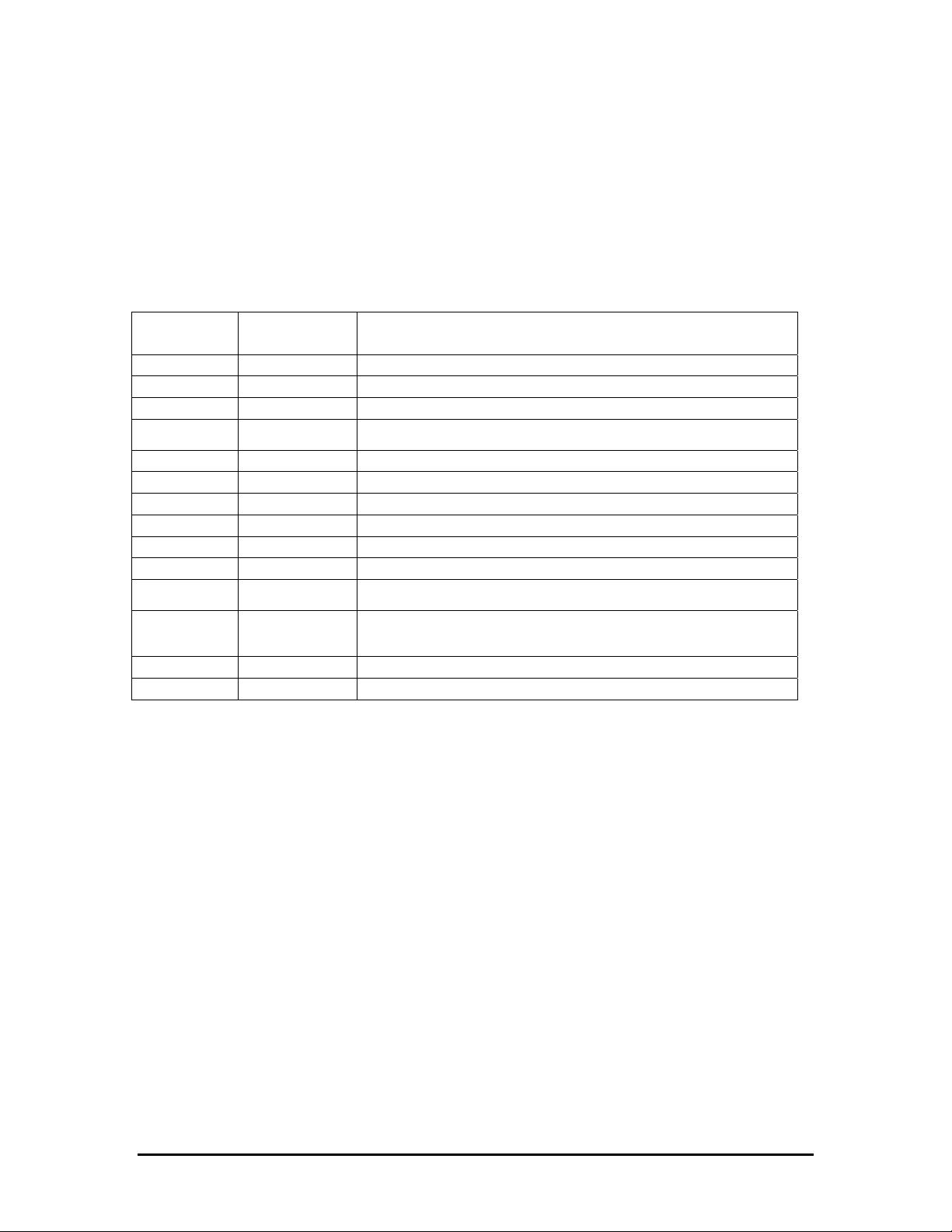

1.2 Revision History

Revision

Number

Date Description

0.1 7/31/02

Initial Draft

0.5 8/16/02

Draft for industry review

0.6 10/4/02

Provides operational detail

0.7 11/4/02

Includes timing diagrams

0.8 11/22/02

More operational detail. Receiver detection sequence changed.

0.9 12/16/02

Minor updates. Solid enough for implementations to be finalized.

0.95 4/25/03

Updates to reflect 1.0a Base Spec. Added multilane suggestions.

1.00 6/19/03

Stable revision for implementation.

1.70 11/6/05

First pass at Gen. 2 PIPE

1.81 12/4/2005

Fixed up areas based on feedback.

1.86 2/27/2006

Fixed up more areas based on feedback. Added a section on how

to handle CLKREQ#.

1.87 9/28/2006

Removed references to Compliance Rate determination. Added

sections for TX Margining and Selectable De-emphasis. Fixed up

areas (6.4) based on feedback.

1.90 3/24/2007

Minor updates, mostly editorial.

2.00 7/21/2007

Minor updates, stable revision for implementation.

剩余37页未读,继续阅读

da895

- 粉丝: 32

- 资源: 10

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论3