基于基于FPGA的带的带CRC校验的异步串口通信校验的异步串口通信

简单介绍了FPGA芯片、Verilog HDL、串口通信协议以及硬件电路设计,详细分析了软件部分各个模块的设计

方法,并下载程序到FPGA芯片,通过微机与系统之间的串口通信,验证了该设计的可行性与可靠性。在实现过

程中,着重分析了移位串/并,并/串转换过程,并加入CRC检验码生成过程和具体校验过程,用Verilog HDL

语言编程,实现了串口通信的采集、数据处理、数据发送的全过程。该方案的特点是实现容易,速度快,效率

高,实用性强,可以广泛应用于终端、打印机、逻辑分析仪、磁盘等与计算机相距不远的人-机交互设备和串行

存储的外部设备。

摘要:由于

关键词:Verilog HDL;串口通信;FPGA;

现场可编程门阵列(field programmable gate array,FPGA)在数字电路设计中已经被广泛使用。这种设计方式可以将以前需

要多块集成芯片的电路设计到一块大模块可编程逻辑器件中,大大减少了电路板的尺寸,增强了系统的可靠性和设计的灵活

性。本文详细介绍了已在实际项目中应用的基于FPGA的串口通信设计。硬件描述语言(hardware description

language,HDL)是一种用形式化方法来描述数字电路和设计数字逻辑系统的语言。数字逻辑电路设计者可以利用这种语言来

描述自己的设计思想,然后利用电子设计自化(EDA)工具进行仿真,再自动综合到门级电路,然后用ASIC或Soft-Core实现其

功能。Verilog HDL是硬件描述语言的一种,用于数字电子系统设计。串口通信是指在一个时间内传输1位数字数据。从19世

纪的二进位电报编码,发展到现在的RS 232(EIA 232),主要用于连接终端和大型主机。串口通信在过去的40年里,大大推动

了通信技术的发展。通信协议是指通信双方的一种约定。约定包括对数据格式、同步方式、传送速度、传送步骤、检纠错方式

以及控制字符定义等问题做出统一规定,通信双方必须共同遵守。因此,也叫通信控制规程,或称传输控制规程,它属于

ISO’sOSI七层

参考模型中的数据链路层,其主要完成的作用如下:

(1)实现数据格式化;

(2)进行串/并转换;

(3)控制数据传输速率;

(4)进行错误检测;

(5)进行TTL与EIA电平转换;

(6)提供EIA-RS 232C接口标准所要求的信号线;

(7)为了完成上述串行接口的任务,串行通信接口电路一般由可编程的串行接口芯片、波特率发生器、EIA与TTL电平转换器

以及地址译码电路组成。

1 方案设计与分析

1.1 硬件电路

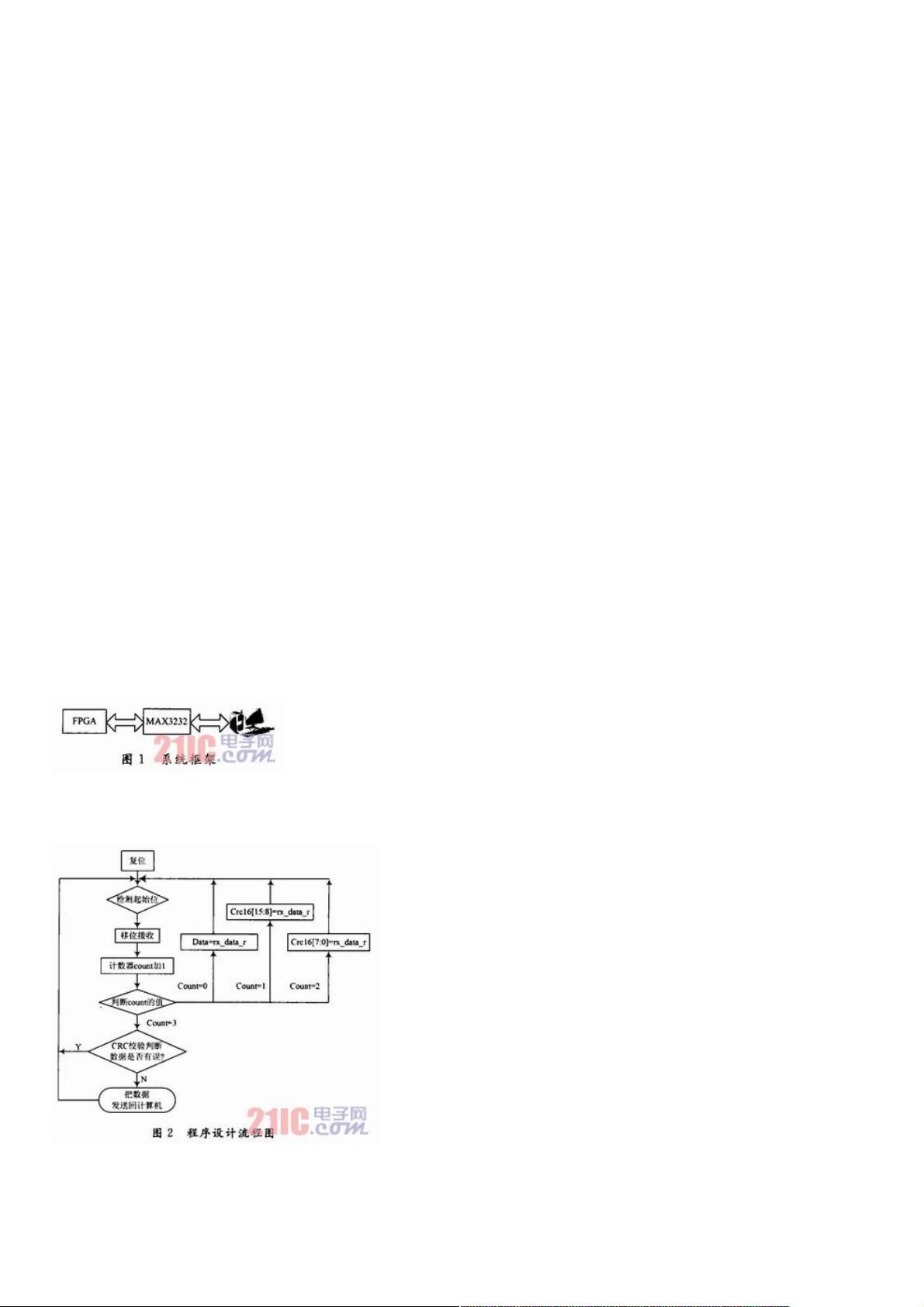

该方案的硬件电路设计包括:FPGA芯片、MAX3232,DB9。其硬件电路与微机通信的结构框图如图1所示。

1.2 软件设计思想

软件部分的设计流程如图2所示。

1.2.1 波特率设置

系统时钟是由PFGA的16引脚输入的24 MHz时钟,而异步串口通信的波特率设置为9 600 b/s,所以需要对主频进行分

频。分频过程定义了2个常量,分别用来存储波特率96 000 b/s的分频计数最大值bpspara和分频计数的一半bps_para_2。每

个系统时钟的上升沿来临时计数器cnt加1,每bps_para_2个系统时钟周期clk_bps改变1次状态,这样就产生了96 000 b/s的

波特率。部分分频代码如下:

评论0