没有合适的资源?快使用搜索试试~ 我知道了~

首页Xilinx FPGA原语的使用方法pdf\Xilinx原语的使用方法1.pdf

Xilinx FPGA原语的使用方法pdf\Xilinx原语的使用方法1.pdf

Xilinx FPGA原语的使用方法pdf\Xilinx原语的使用方法1.pdf

资源详情

资源评论

资源推荐

Xilinx 原语的使用方法 1

3.4 Xilinx 公司原语的使用方法

原语,其英文名字为 Primitive,是 Xilinx 针对其器件特征开发的一系列常用模

块的名字,用户可以将其看成 Xilinx 公司为用户提供的库函数,类似于 C++

中的“cout”等关键字,是芯片中的基本元件,代表 FPGA 中实际拥有的硬件逻

辑单元,如 LUT,D 触发器,RAM 等,相当于软件中的机器语言。在实现过

程中的翻译步骤时,要将所有的设计单元都转译为目标器件中的基本元件,否

则就是不可实现的。原语在设计中可以直接例化使用,是最直接的代码输入方

式,其和 HDL 语言的关系,类似于汇编语言和 C 语言的关系。

Xilinx 公司提供的原语,涵盖了 FPGA 开发的常用领域,但只有相应配置的硬

件才能执行相应的原语,并不是所有的原语都可以在任何一款芯片上运行。在

Verilog 中使用原语非常简单,将其作为模块名直接例化即可。本节以 Virtex-4

平台介绍各类原语,因为该系列的原语类型是最全面的。其它系列芯片原语的

使用方法是类似的。

Xilinx 公司的原语按照功能分为 10 类,包括:计算组件、I/O 端口组件、寄存

器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM

组件、Slice/CLB 组件以及 G 比特收发器组件。下面分别对其进行详细介绍。

3.4.1 计算组件

计算组件指的就是 DSP48 核,也有人将其称为硬件乘法器,功能描述如表 3-6

所示。

表 3-6 计算组件清单

DSP48 其结构为一个 18*18 比特的有符号乘法器,且在后面还级联了一个

带有可配置流水线的 3 输入加法器

DSP48 核由一个 18 比特的乘法后面级联一个 48 比特的加法器,乘法器和加

法器的应用位宽分别可以在 18、48 比特内任意调整。其在乘加模块中有广

泛应用,特别是各类滤波器系统中,不仅可以提高系统稳定性,还能够节省

逻辑资源且工作在高速模式下。其在 Verilog 中的例化模版为:

module fpga_v4_dsp48(

BCOUT, P, PCOUT, A, B, BCIN, C, CARRYIN,CARRYINSEL, CEA,

CEB,

CEC, CECARRYIN, CECINSUB, CECTRL, CEM, CEP, CLK, OPMODE,

PCIN, RSTA, RSTB, RSTC, RSTCARRYIN, RSTM, RSTP,

SUBTRACT);

output [17:0]BCOUT;

output [47:0] P, PCOUT; //

input [17:0] A, B; //

input [47:0] C, PCIN;

input [1:0] CARRYINSEL;

input [6:0] OPMODE;

input BCIN, CARRYIN,CEA,CEB,

CEC,CECARRYIN,CECINSUB,CECTRL,CEM,

CEP,CLK, RSTA,

RSTB,RSTC,RSTCARRYIN,RSTM,RSTP,SUBTRACT;

//对 DSP48 原语的功能进行配置。

DSP48 #(

.AREG(1), // Number of pipeline registers on the A input, 0, 1 or 2

.BREG(1), // Number of pipeline registers on the B input, 0, 1 or 2

.B_INPUT("DIRECT"),

// B input DIRECT from fabric or CASCADE from another

DSP48

.CARRYINREG(1),

// Number of pipeline registers for the CARRYIN input, 0 or 1

.CARRYINSELREG(1),

// Number of pipeline registers for the CARRYINSEL, 0 or 1

.CREG(1), // Number of pipeline registers on the C input, 0 or 1

.LEGACY_MODE("MULT18X18S"),

// Backward compatibility, NONE, MULT18X18 or

MULT18X18S

.MREG(1), // Number of multiplier pipeline registers, 0 or 1

.OPMODEREG(1), // Number of pipeline regsiters on OPMODE

input, 0 or 1

.PREG(1), // Number of pipeline registers on the P output, 0 or 1

.SUBTRACTREG(1)

// Number of pipeline registers on the SUBTRACT input, 0 or 1

) fpga_v4_dsp48 (

.BCOUT(BCOUT), // 18-bit B cascade output

.P(P), // 48-bit product output

.PCOUT(PCOUT), // 48-bit cascade output

.A(A), // 18-bit A data input

.B(B), // 18-bit B data input

.BCIN(BCIN), // 18-bit B cascade input

.C(C), // 48-bit cascade input

.CARRYIN(CARRYIN), // Carry input signal

.CARRYINSEL(CARRYINSEL), // 2-bit carry input select

.CEA(CEA), // A data clock enable input

.CEB(CEB), // B data clock enable input

.CEC(CEC), // C data clock enable input

.CECARRYIN(CECARRYIN), // CARRYIN clock enable input

.CECINSUB(CECINSUB), // CINSUB clock enable input

.CECTRL(CECTRL), // Clock Enable input for CTRL regsiters

.CEM(CEM), // Clock Enable input for multiplier regsiters

.CEP(CEP), // Clock Enable input for P regsiters

.CLK(CLK), // Clock input

.OPMODE(OPMODE), // 7-bit operation mode input

.PCIN(PCIN), // 48-bit PCIN input

.RSTA(RSTA), // Reset input for A pipeline registers

.RSTB(RSTB), // Reset input for B pipeline registers

.RSTC(RSTC), // Reset input for C pipeline registers

.RSTCARRYIN(RSTCARRYIN), // Reset input for CARRYIN

registers

.RSTCTRL(RSTCTRL), // Reset input for CTRL registers

.RSTM(RSTM), // Reset input for multiplier registers

.RSTP(RSTP), // Reset input for P pipeline registers

.SUBTRACT(SUBTRACT) // SUBTRACT input

);

endmodule

3.4.2 时钟组件

时钟组件包括各种全局时钟缓冲器、全局时钟复用器、普通 I/O 本地的时钟

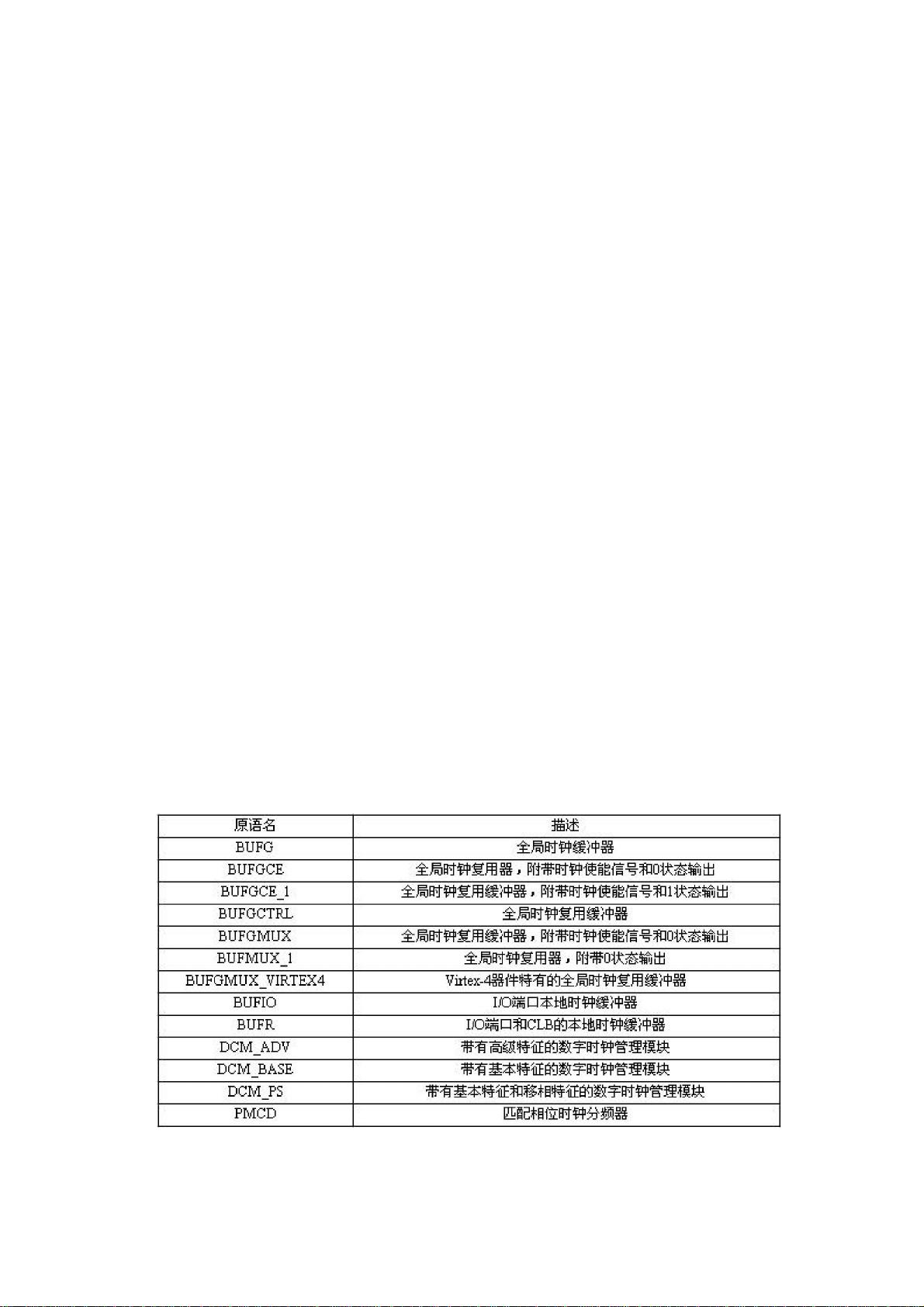

缓冲器以及高级数字时钟管理模块,如表 3-7 所示。

表 3-7 时钟组件的清单

下面对几个常用时钟组件进行简单介绍,其余组件的使用方法是类似的。

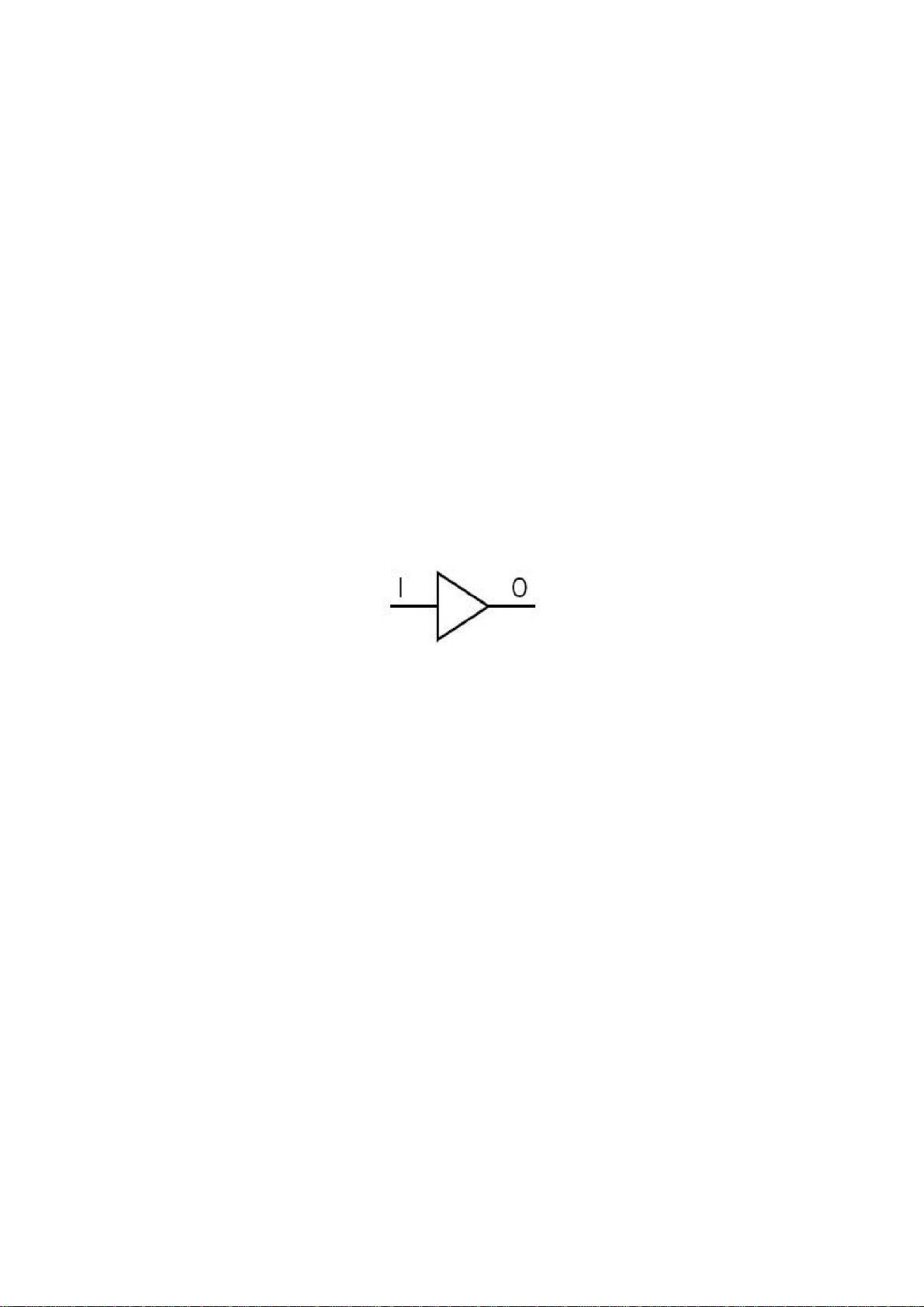

1.BUFG

BUFG 是具有高扇出的全局时钟缓冲器,一般由综合器自动推断并使用,其

和同类原语的 RTL 结构如图 3-28 所示。全局时钟是具有高扇出驱动能力的

缓冲器,可以将信号连到时钟抖动可以忽略不计的全局时钟网络,BUFG 组

件还可应用于典型的高扇出信号和网络,如复位信号和时钟使能信号。如果

要对全局时钟实现 PLL 或 DCM 等时钟管理,则需要手动例化该缓冲器。其

例化的代码模板如下所示:

// BUFG: 全局时钟缓存(Global Clock Buffer),只能以内部信号驱动

// Xilinx HDL 库向导版本,ISE 9.1

BUFG BUFG_inst (

.O(O), //时钟缓存输出信号

.I(I) // /时钟缓存输入信号

);

// 结束 BUFG_ins 模块的例化过程

在综合结果分析中,其和同类原语的 RTL 结构如图 3-32 所示。

图 3-32 全局时钟原语的 RTL 级结构示意图

2. BUFMUX

BUFMUX 是全局时钟复用器,选择两个输入时钟 I0 或 I1 中的一个作为全局

时钟,其和同类原语 BUFMUX1 的 RTL 级结构如图 M 所示。当选择信号 S

为低时,选择 I0;否则输出 I1,其真值表如表 M 所示。BUFMUX 原语和

BUFMUX1 原语的功能一样,只是选择逻辑不同,对于 BUFMUX1,当选择

信号 S 为低时,选择 I1;否则输出 I0。

BUFMUX 原语的例化代码模板如下所示:

// BUFGMUX: 全局时钟的 2 到 1 复用器(Global Clock Buffer 2-to-1 MUX)

// 适用芯片:Virtex-II/II-Pro/4/5, Spartan-3/3E/3A

// Xilinx HDL 库向导版本,ISE 9.1

BUFGMUX BUFGMUX_inst (

.O(O), //时钟复用器的输出信号

.I0(I0), // 0 时钟输入信号

.I1(I1), //1 时钟输入信号

.S(S) // 时钟选择信号

);

// 结束 BUFGMUX_inst 模块的例化过程

剩余16页未读,继续阅读

hglikun

- 粉丝: 3

- 资源: 47

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论3