指

导

教

师

评

语

建议:从学生的工作态度、工作量、设计(论文)的创造性、学术性、实用性及书面表达能力等方面给出评价。

签名: 20 年 月 日

目录

一·课程设计任务....................................................................................................4

1、设计目的..............................................................................................................4

2、设计要求..............................................................................................................4

二·课程设计原理及设计方案................................................................................4

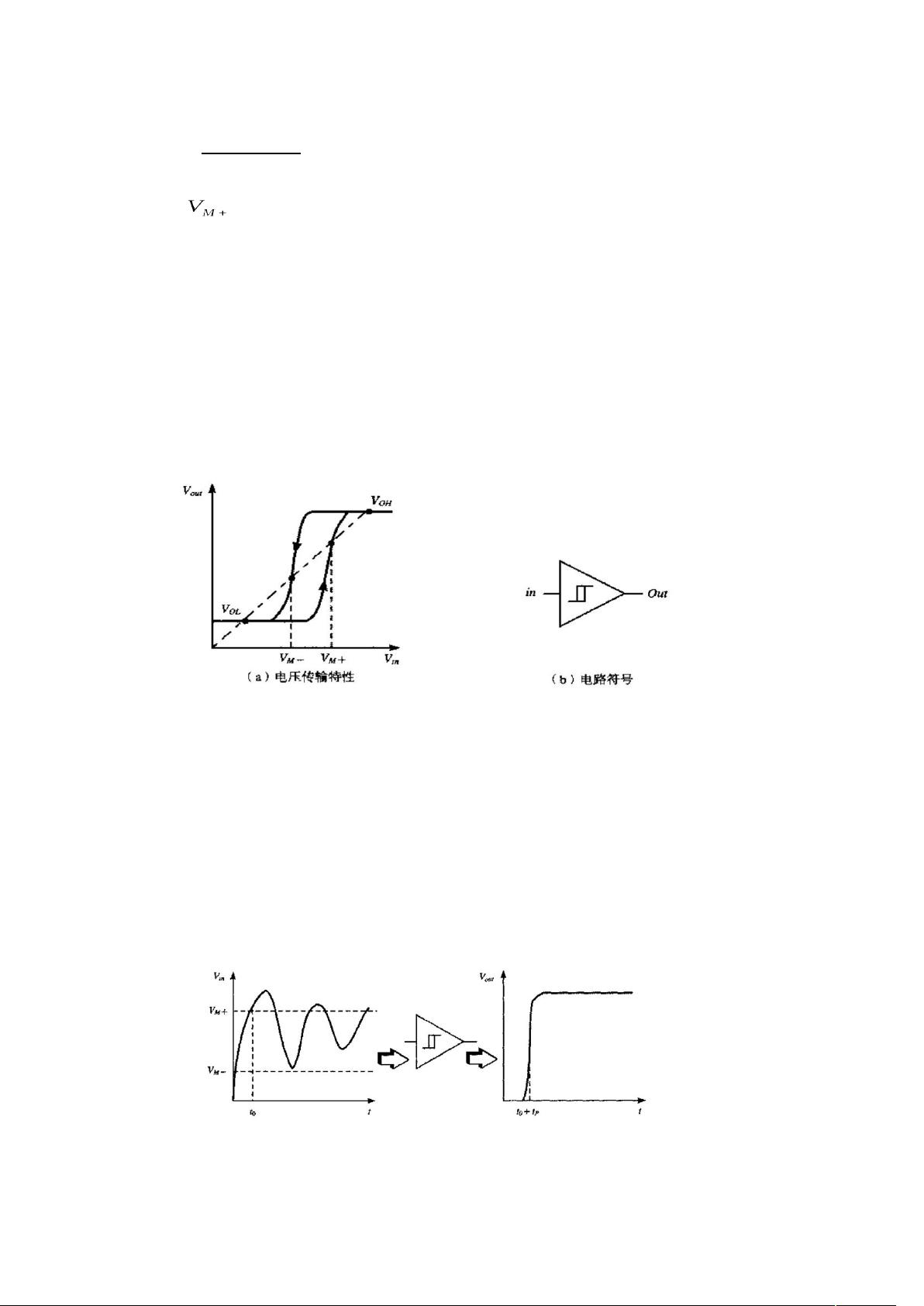

1、设计原理..............................................................................................................4

2、设计方案..............................................................................................................6

3、工具软件和测试环境介绍..................................................................................7

三·课程设计的步骤和结果....................................................................................7

1、电路设计..............................................................................................................8

2、符号设计..............................................................................................................9

3、版图设计..............................................................................................................9

四·实验结果与分析..............................................................................................13

1、总设计过程与分析............................................................................................13

2、电路设计过程与分析........................................................................................14

3、版图设计过程与分析........................................................................................15