Vivado UG1037:AXI协议详解与Xilinx设计迁移指南

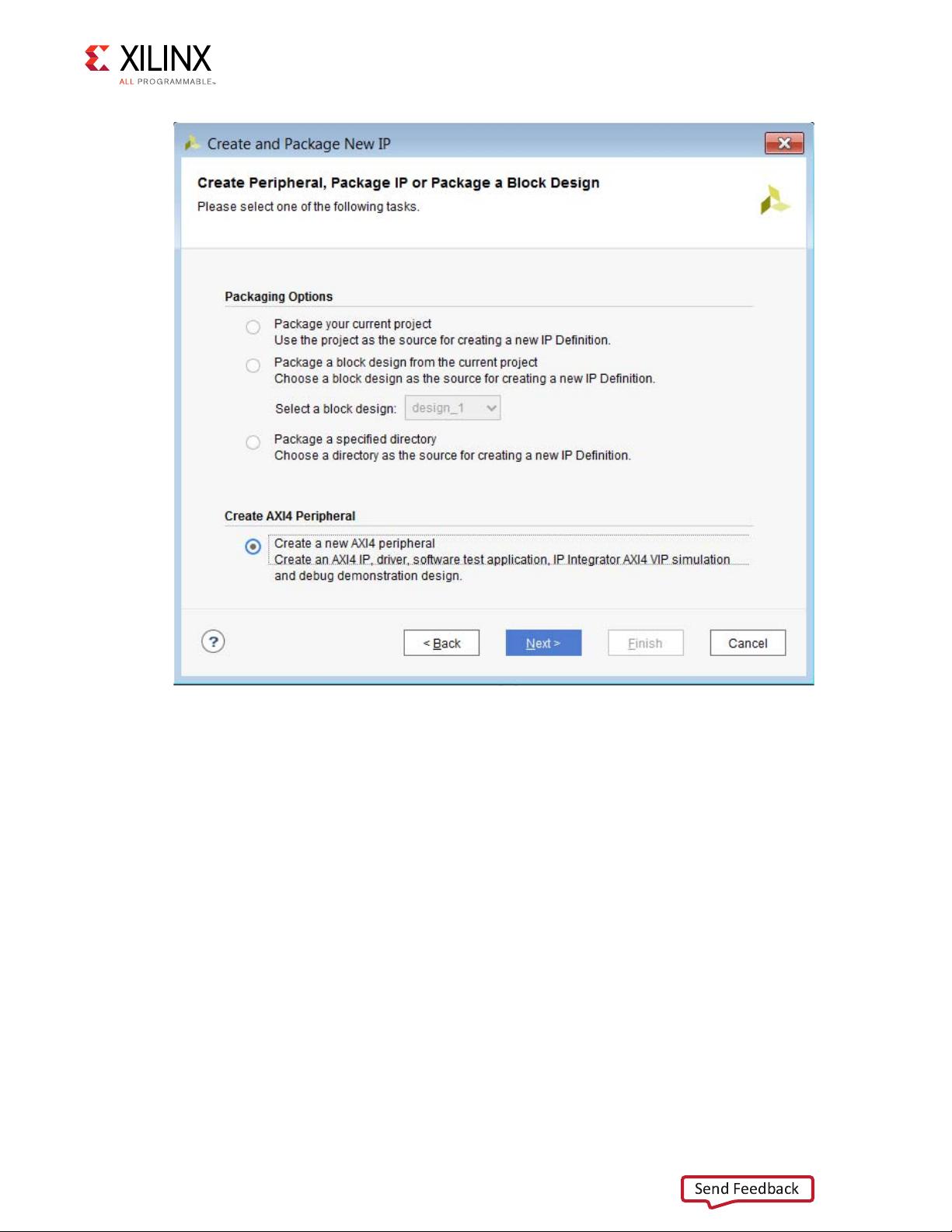

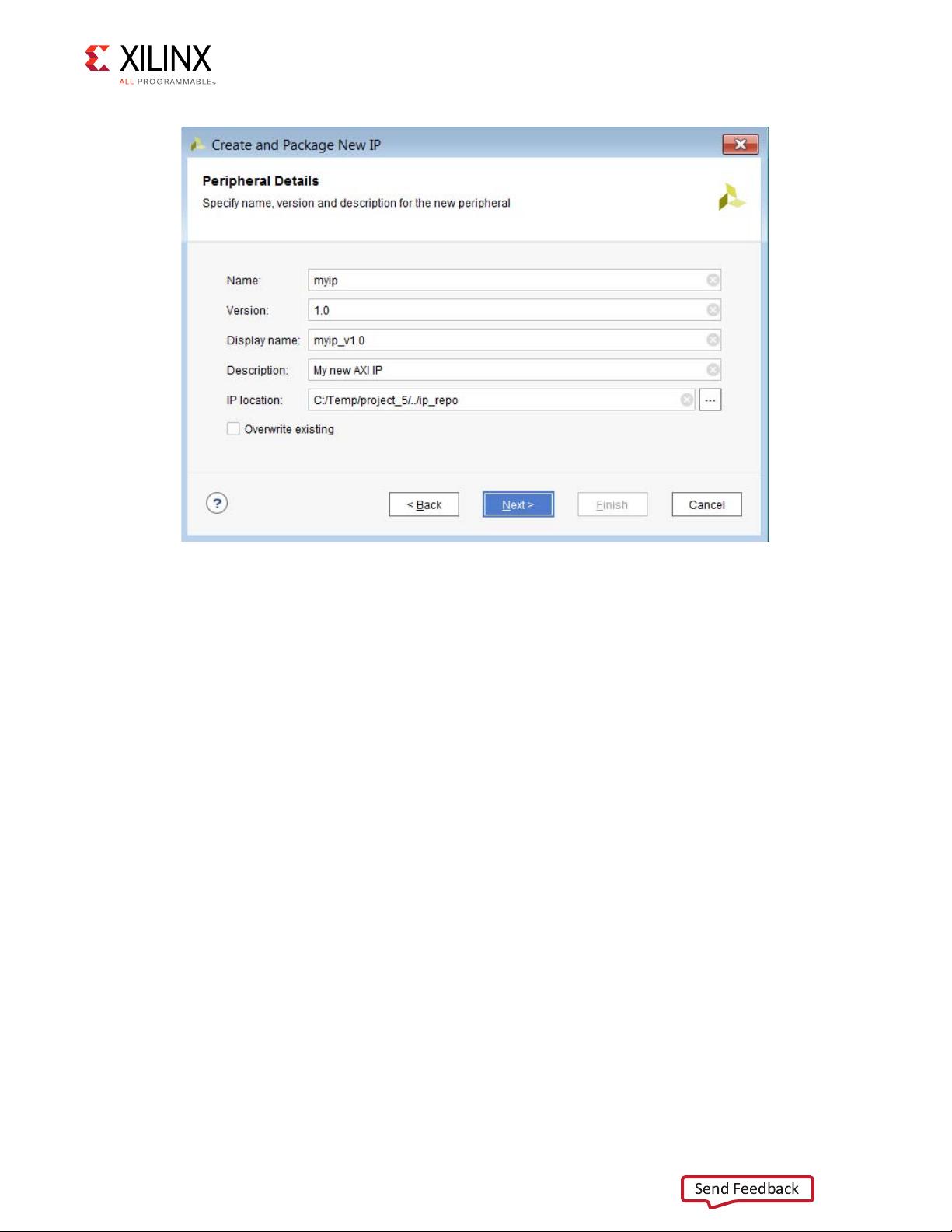

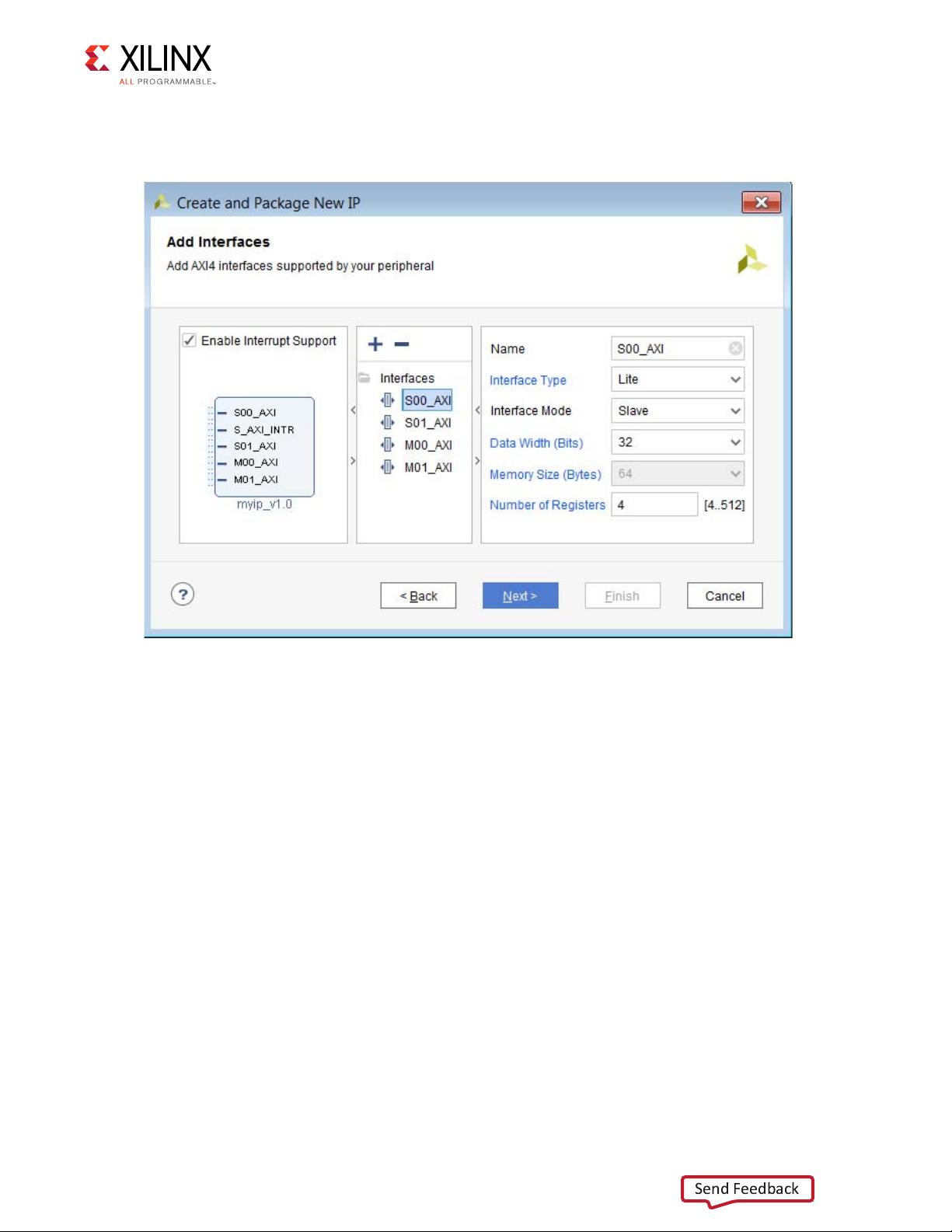

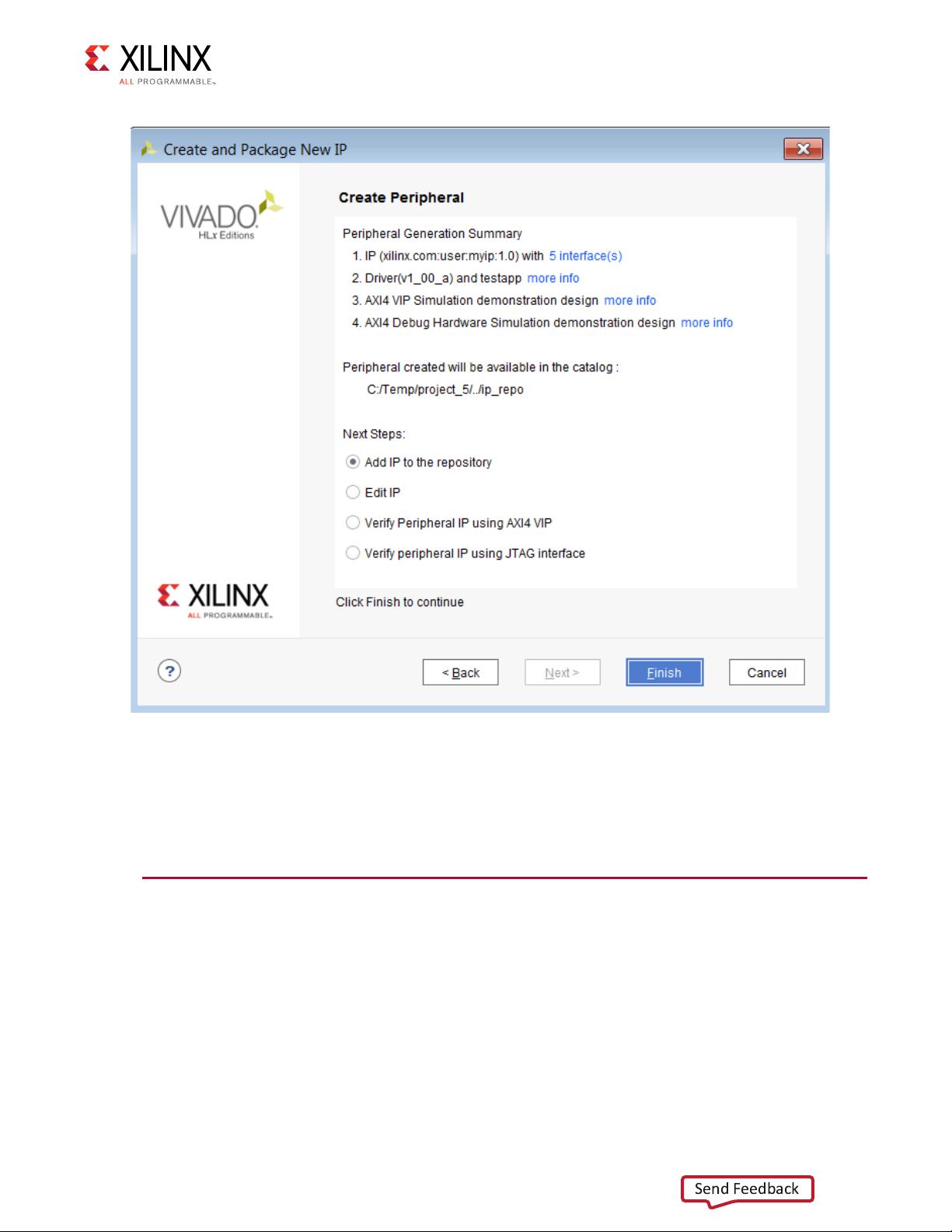

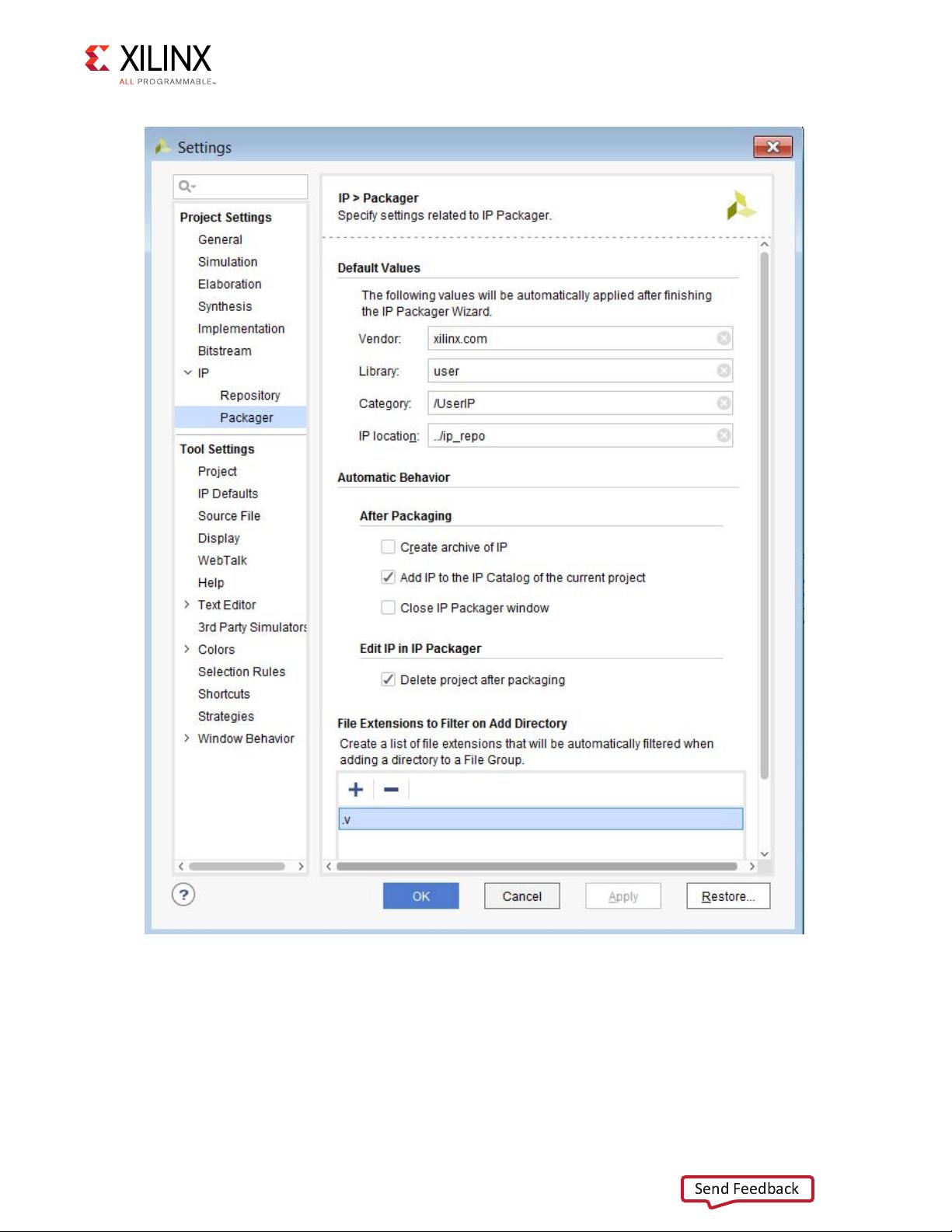

《Vivado AXI参考指南》(UG1037)是Xilinx为适应其Spartan-6、Virtex-6以及后续的UltraScale架构、7系列和Zynq-7000全可编程SoC设备而发布的文档。该指南旨在介绍高级可扩展接口(AXI)协议的关键概念,帮助用户了解如何利用Xilinx工具创建基于AXI的IP核心,并概述了Xilinx对AXI协议的采用特点。 首先,指南介绍了AXI协议的基础,这是一种高性能的系统总线标准,支持并行数据传输,被广泛应用于现代FPGA和SoC设计中,以提高系统性能和灵活性。它包含多个版本,如AXI4,AXI4-Stream和AXI4-Lite,每个版本针对不同的应用需求提供不同的特性。 在Vivado工具方面,该指南强调了Vivado Design Suite中的各种功能,包括但不限于AXI IP Catalog,这是一个丰富的IP库,提供了多种预配置的AXI接口模块,如AXI Interconnect、AXI Memory Mapped、AXI FIFO等,用于构建复杂的设计。此外,还提到了Vivado Lab工具的更新,确保用户能够利用最新的开发环境进行项目开发。 对于设计迁移,指南提供了逐步指导,帮助设计师将现有的非AXI设计迁移到使用AXI接口,这涉及到了解AXI的不同模式和特性,如地址空间映射、数据宽度选择以及交易类型(读、写、响应)。同时,针对Zynq-7000平台的特定,指南强调了Smart Connect IP和Verification IPs,如AXI Smart Connect IP用于简化连接管理,AXI Verification IP则用于验证IP之间的通信是否符合预期。 对于Zynq UltraScale+ MPSoC处理器,指南中也有所提及,这意味着设计者可以利用这些高级特性优化多核和片上系统的设计。此外,文档还提供了历史修订信息,展示了随着Vivado工具的更新和新产品的加入,指南是如何随着技术发展而不断完善的。 《Vivado AXI参考指南》为Xilinx用户提供了宝贵的资源,无论是初学者还是经验丰富的工程师,都可以从中找到关于AXI设计、开发和优化的实用信息。通过阅读和实践,设计师可以更好地利用AXI协议来提升FPGA和SoC设计的性能和效率。

剩余174页未读,继续阅读

- 粉丝: 0

- 资源: 14

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 计算机系统基石:深度解析与优化秘籍

- 《ThinkingInJava》中文版:经典Java学习宝典

- 《世界是平的》新版:全球化进程加速与教育挑战

- 编程珠玑:程序员的基础与深度探索

- C# 语言规范4.0详解

- Java编程:兔子繁殖与素数、水仙花数问题探索

- Oracle内存结构详解:SGA与PGA

- Java编程中的经典算法解析

- Logback日志管理系统:从入门到精通

- Maven一站式构建与配置教程:从入门到私服搭建

- Linux TCP/IP网络编程基础与实践

- 《CLR via C# 第3版》- 中文译稿,深度探索.NET框架

- Oracle10gR2 RAC在RedHat上的安装指南

- 微信技术总监解密:从架构设计到敏捷开发

- 民用航空专业英汉对照词典:全面指导航空教学与工作

- Rexroth HVE & HVR 2nd Gen. Power Supply Units应用手册:DIAX04选择与安装指南

信息提交成功

信息提交成功