Verilog实现任意整数分频器:节省资源与考察设计理解

在FPGA设计中,Verilog语言是一种强大的工具,用于实现各种功能,其中分频器是常见的基础组件。本文将详细介绍如何使用Verilog实现任意整数分频器,包括偶数倍和奇数倍分频。

首先,对于偶数倍分频,它相对简单,可以通过计数器来实现。例如,对于N倍分频,我们设计一个计数器,每当输入时钟(clk_in)上升沿到来时,计数器加一。当计数器值达到N/2-1时,输出时钟(clk_out)翻转,并对计数器进行复位。这种设计利用了D触发器和非门的基本逻辑,确保输出时钟周期为输入时钟周期的N倍。公式表示为:Q(n+1) = D,D = ~Q(n),clk_out = Q(n+1)。

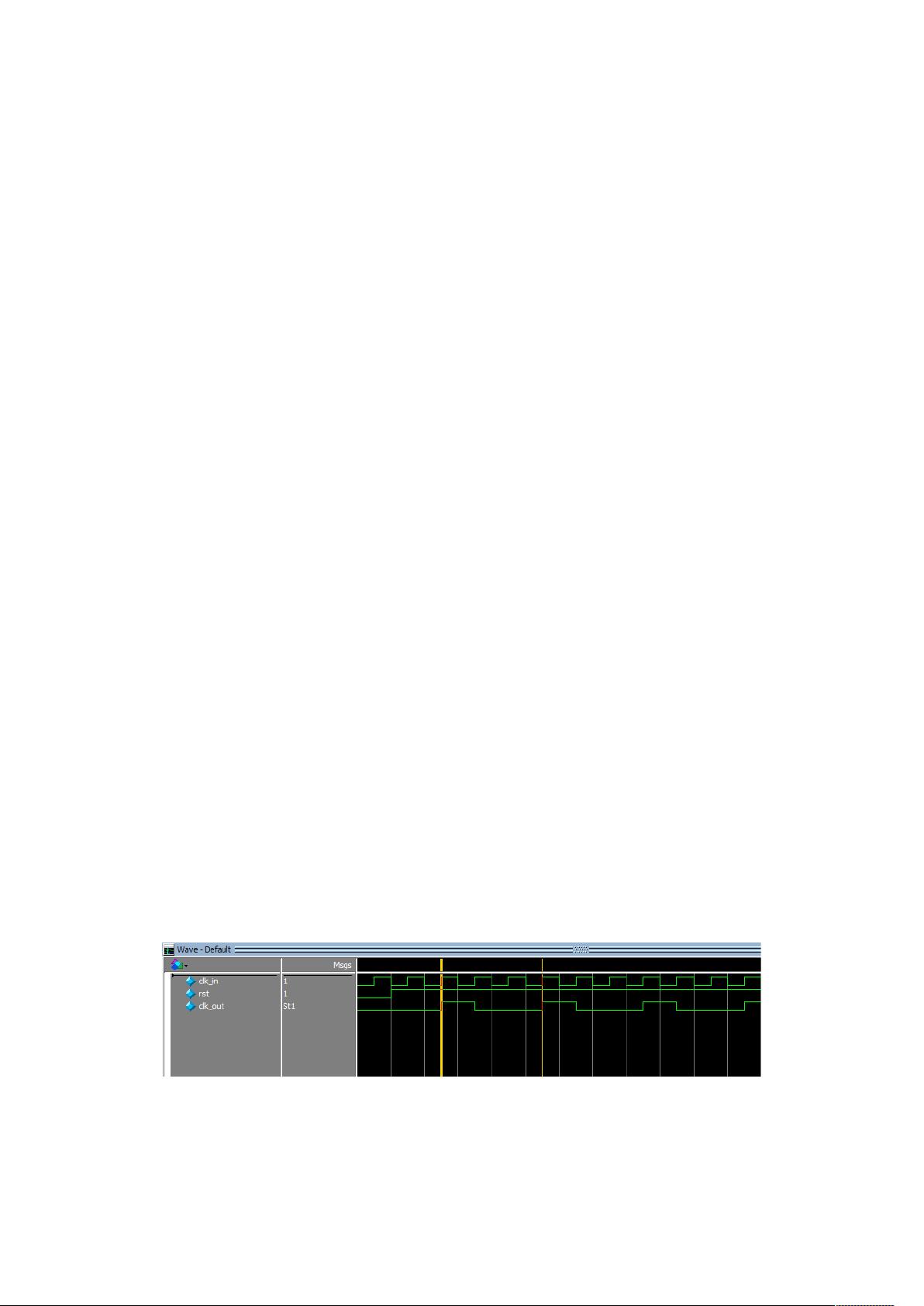

对于奇数倍分频,情况稍微复杂一些。有几种方法可以实现,这里以一个常见的例子——占空比不为50%的三分频为例。我们可以设计一个计数器,当计数器值等于1或2时,输出时钟翻转。模块`three`的Verilog代码给出了这个实现,通过`rst`引脚的复位和`clk_in`上升沿触发,计数器从0开始计数,当计数到1时输出翻转一次,计数到2时再翻转一次,从而达到非50%的占空比。

奇数倍分频器的实现依赖于对计数器行为的精确控制,这涉及到模数计算和条件判断。对于更复杂的奇数分频,可能需要使用状态机或者预设逻辑来处理不同阶段的计数和输出翻转。这不仅能体现设计者的逻辑理解和编程能力,也是面试中常用的问题,以评估应聘者的数字逻辑设计水平。

用Verilog实现任意整数分频器是一个灵活且实用的技能,不仅能够节省芯片资源,还能展示出设计者的逻辑设计和代码编写能力。在实际应用中,根据具体需求选择合适的分频方法,合理分配逻辑资源,才能优化FPGA设计并满足性能要求。学习和掌握这些基础技术,是成为一名优秀FPGA工程师的重要一步。

2022-04-08 上传

点击了解资源详情

2021-07-13 上传

2021-10-11 上传

2021-07-13 上传

点击了解资源详情

St0pH@CK

- 粉丝: 5

- 资源: 16

最新资源

- 计算机控制系统 - pdf课件 - 第四章

- 计算机控制系统 - pdf 课件 - 第三章

- LVS手册,负载均衡的常用工具手册

- 计算机控制系统 - pdf 课件 - 第二章

- 计算机控制系统 - pdf课件 - 第一章

- 黑莓8100帮助文件

- cathedral_RL_v1.1.pdf

- Qt 嵌入式图形开发(入门篇)

- 音频 水印 学习 5656

- Qt编程初步(PDF格式)

- 南开出版的全国计算机二级C的习题

- <Adam品质保证>[原版][中文][官方手册]STC12C5A60S2(STC-51系列单片机)

- 常用SQL语句--全面

- 稳压电源基础 PDF

- wsbpel-v2.0

- TMS320DM642中文手册