Micron异步NAND闪存接口详解与MT29系列规格

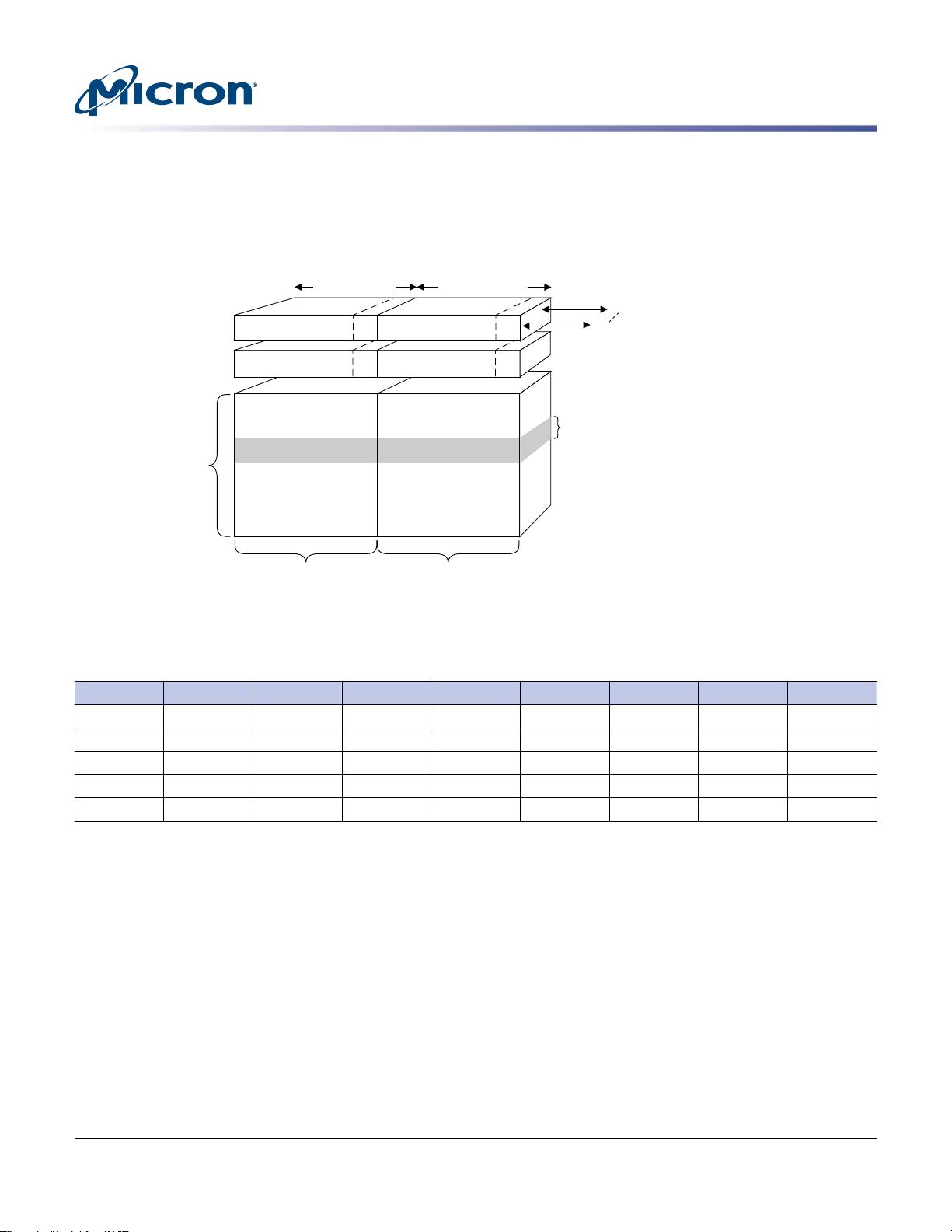

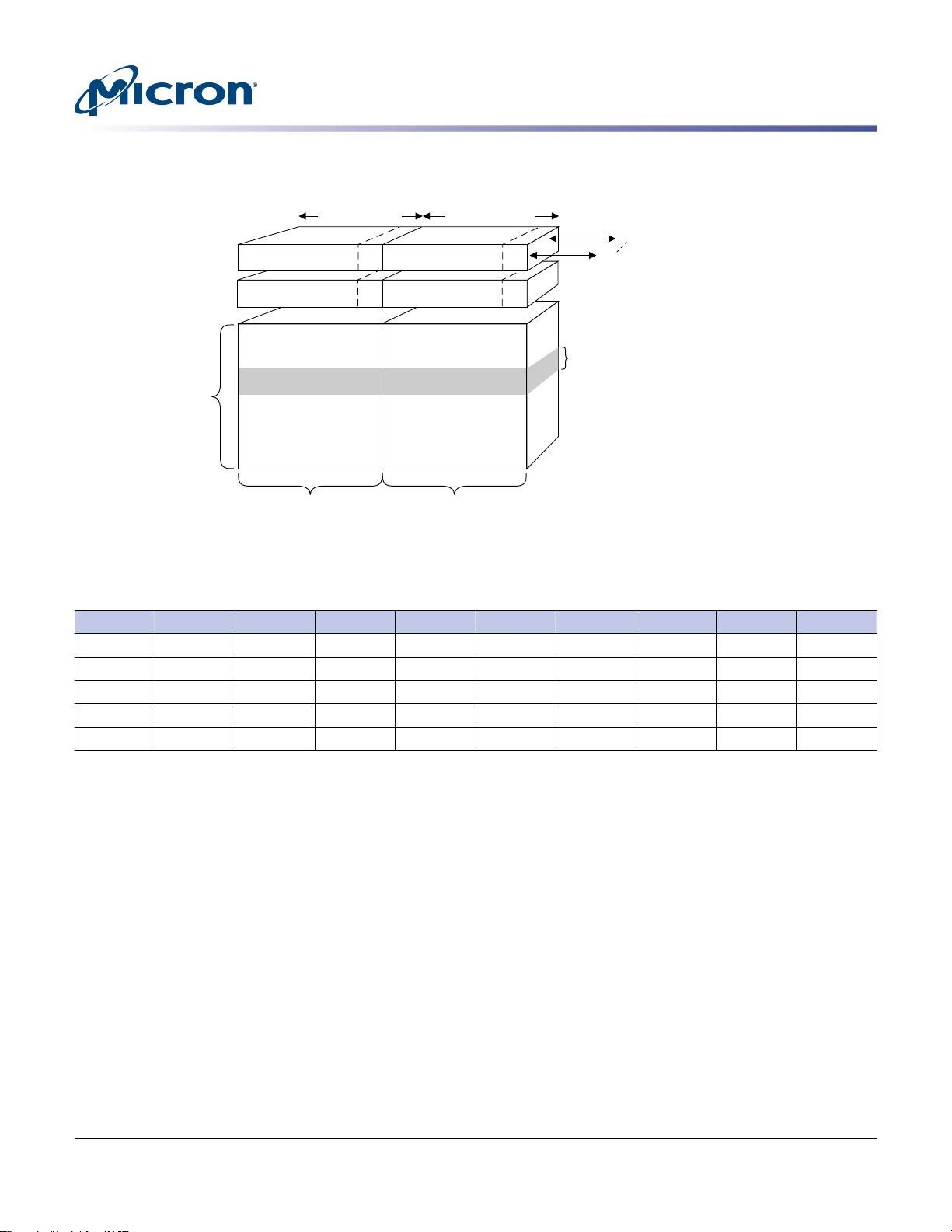

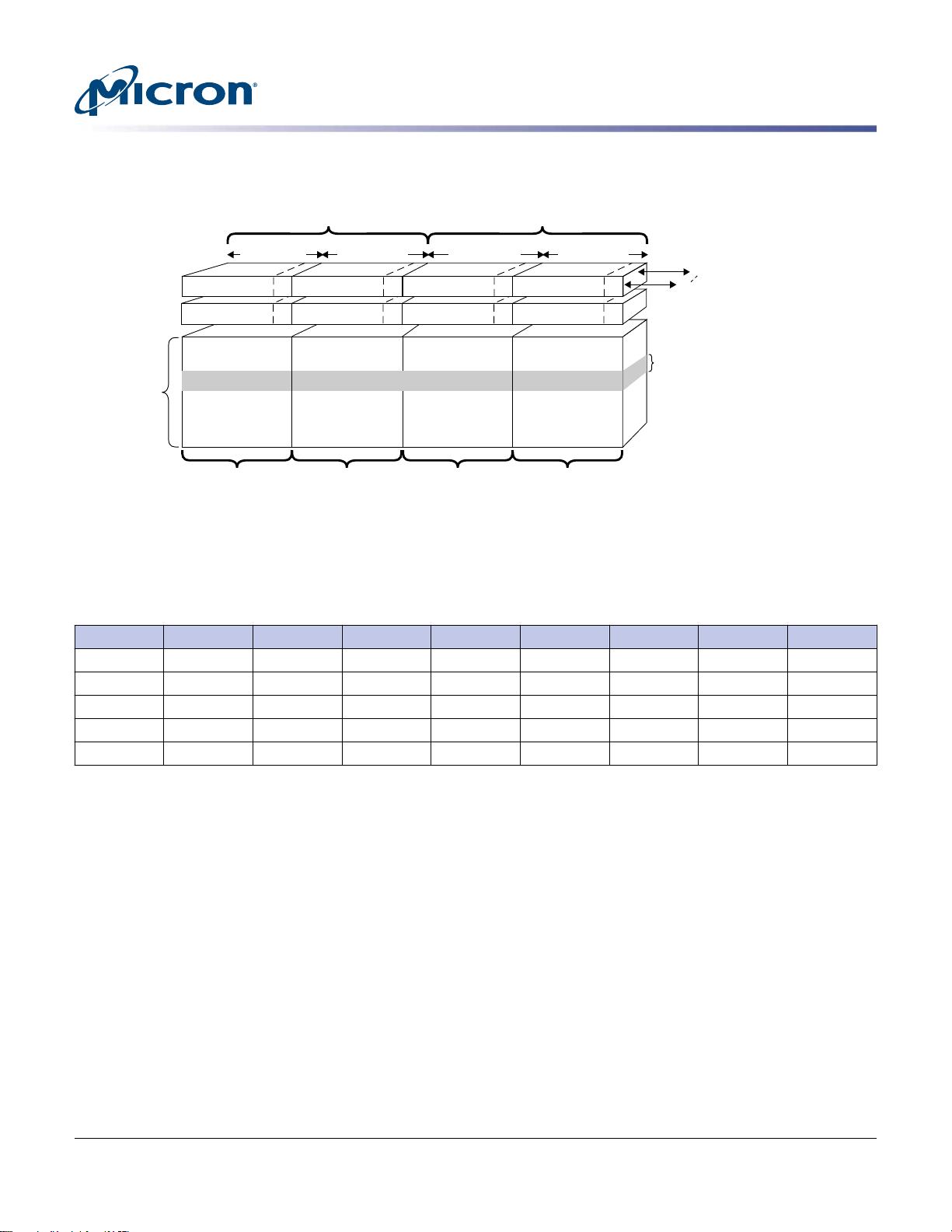

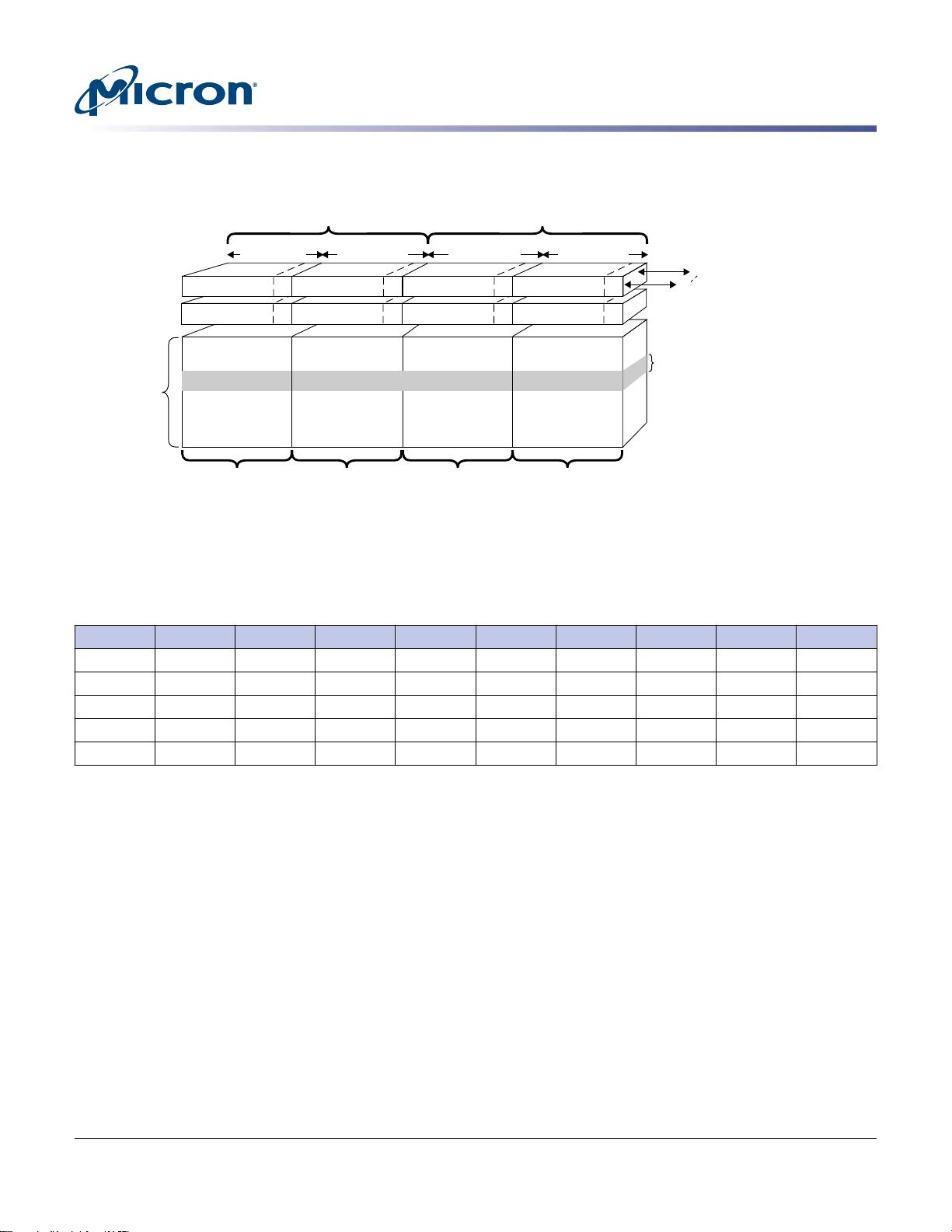

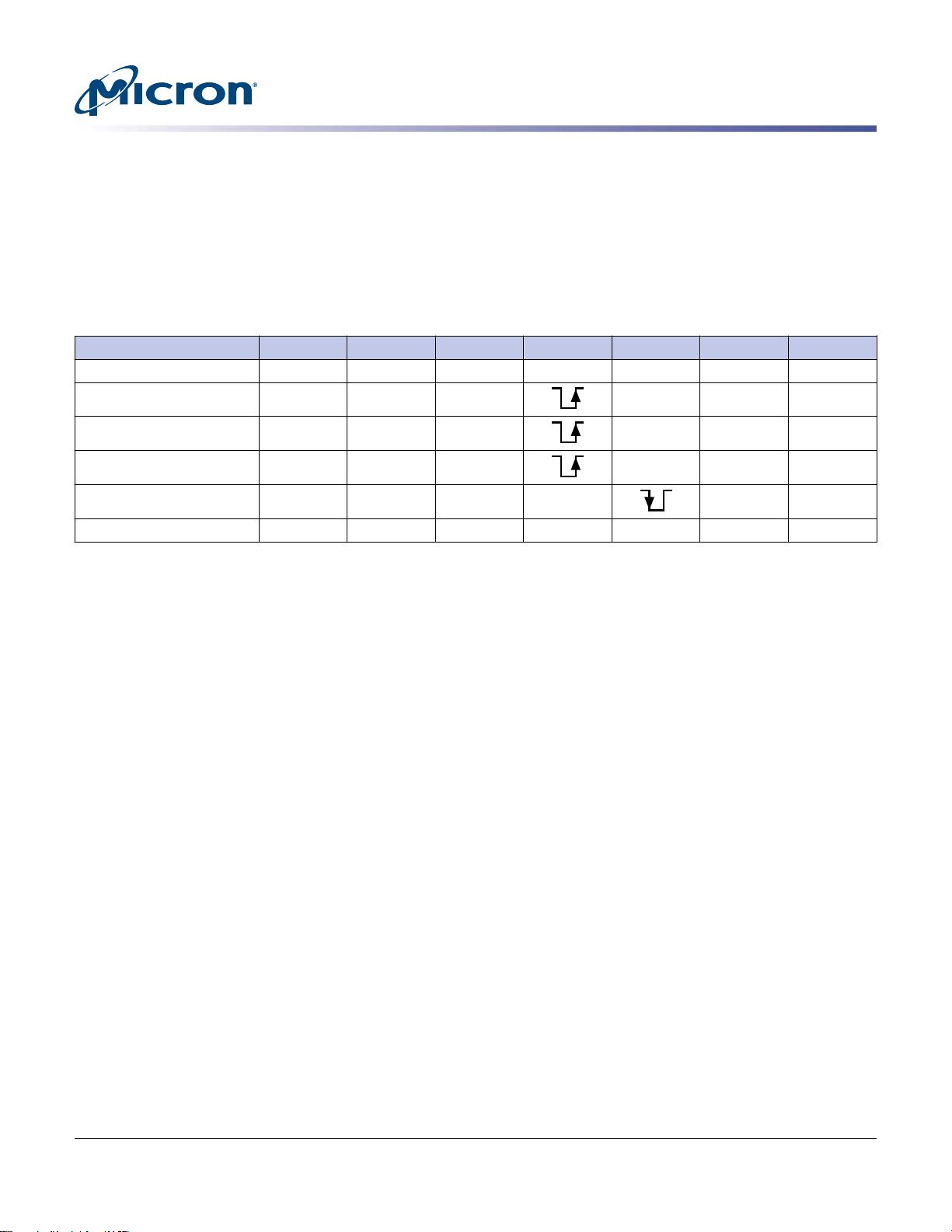

本文档介绍的是Micron公司的NAND闪存设备,具体型号包括MT29F4G08ABAWP等系列。这些设备采用了开放NAND闪存接口(ONFI)1.0标准,采用单级细胞(SLC)技术,提供高性能的异步数据接口。其关键特性包括: 1. **接口兼容性**:支持ONFI 1.0规范,便于系统集成和通信。 2. **存储单元结构**: - 页大小:x8(8位)页面为2112字节(2048+64字节),x16(16位)页面为1056个单词(1024+32个单词)。 - 块尺寸:64页,对应128KB + 4KB的存储空间。 - 飞片大小:每个设备包含2个飞片,每片有2048个块。 - 总容量:4GB、8GB、16GB型号分别对应4096块、8192块和16384块。 3. **性能指标**: - 异步I/O速度:在3.3V时,读写命令时间(tRC/tWC)分别为20ns和25ns,而在1.8V下稍有增加。 - 操作速度:典型情况下,读取一页为25μs,编程一页(典型)为1.8V时200μs或3.3V时200μs,擦除一个块为700μs。 4. **高级命令集**: - 支持程序缓存模式和读取缓存模式。 - 具备一次性编程(OTP)功能,可以设置特定参数。 - 包含两个平面的命令处理能力,支持多路存取(LUN)操作。 - 可读取唯一标识符,便于设备管理。 - 1.8V电压下支持块锁定功能。 - 内部数据移动功能,优化数据操作效率。 5. **状态字节**:设备提供操作状态字节,通过软件方法检测设备工作状态,有助于故障诊断和管理。 这些MT29F系列NAND闪存产品适用于需要高效、低功耗和高度可扩展性的应用,广泛应用于各种嵌入式系统、移动设备和固态硬盘(SSD)等场景。理解并利用这些特性对于设计和优化数据存储解决方案至关重要。

剩余131页未读,继续阅读

- 粉丝: 0

- 资源: 1

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 利用迪杰斯特拉算法的全国交通咨询系统设计与实现

- 全国交通咨询系统C++实现源码解析

- DFT与FFT应用:信号频谱分析实验

- MATLAB图论算法实现:最小费用最大流

- MATLAB常用命令完全指南

- 共创智慧灯杆数据运营公司——抢占5G市场

- 中山农情统计分析系统项目实施与管理策略

- XX省中小学智慧校园建设实施方案

- 中山农情统计分析系统项目实施方案

- MATLAB函数详解:从Text到Size的实用指南

- 考虑速度与加速度限制的工业机器人轨迹规划与实时补偿算法

- Matlab进行统计回归分析:从单因素到双因素方差分析

- 智慧灯杆数据运营公司策划书:抢占5G市场,打造智慧城市新载体

- Photoshop基础与色彩知识:信息时代的PS认证考试全攻略

- Photoshop技能测试:核心概念与操作

- Photoshop试题与答案详解

信息提交成功

信息提交成功