本文档详细介绍了在Vivado中创建和调用自定义IP核的步骤,适合初学者学习FPGA设计与IP封装流程。

在Vivado中生成自定义IP核是 FPGA 设计的关键步骤之一,这允许设计者复用已有的功能模块,提高设计效率。以下是对整个过程的详细解释:

1. 准备IP核模块:首先,你需要有一个已完成设计的Verilog或VHDL模块,这个模块将成为IP核的基础。确保模块逻辑完整且满足功能需求。

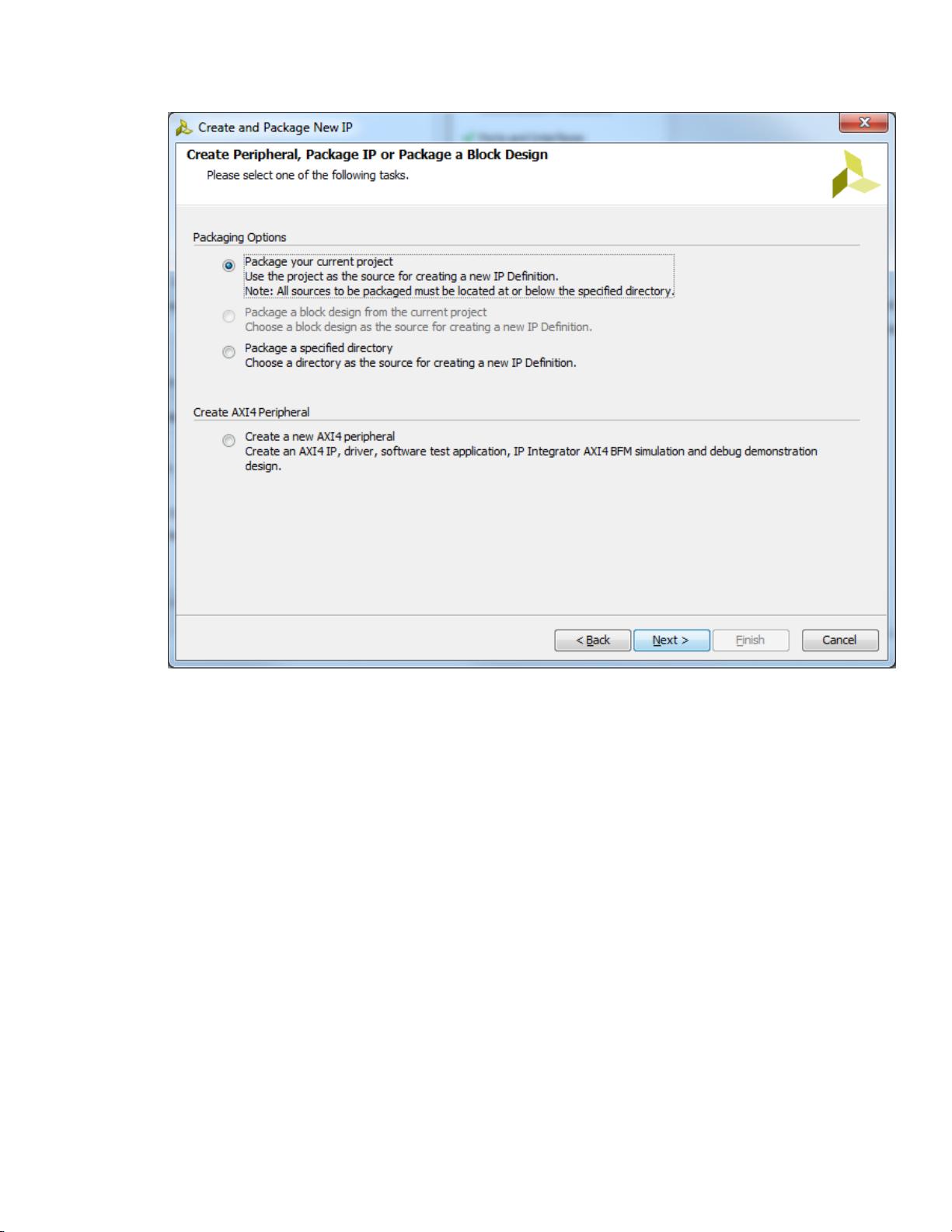

2. 启动IP核封装:在Vivado的菜单栏中,选择“工具”(Tools)> “生成并封装IP”(Create and Package IP),启动IP核封装向导。

3. 选择封装类型:在向导窗口中,按照你的需求选择相应的选项。如果要将当前项目封装为IP,选择“打包封装当前项目”。

4. 设置IP存储路径:在后续窗口中,指定IP核的存储位置,以便于管理和查找。

5. 配置IP信息:在IP核信息页面(图6),设置IP的名称、版本等基本信息,这些信息将在IP核使用时显示。

6. 选择兼容性:在IP核兼容性页面(图7),根据目标硬件平台(例如Zedboard上的Zynq芯片)选择合适的设备和库。

7. 定义接口:在IP核接口信息页面(图8),查看并确认IP核的输入/输出引脚配置,确保它们符合设计要求。

8. 查看图形模块:在图9中,可以看到封装后的IP核的图形表示,这对于原理图设计很有帮助。

9. 完成封装:在“预览和生成”页面(图10),点击“封装IP”按钮,完成IP核的创建。一旦生成,IP核就可以在其他项目中复用了。

调用生成的IP核包括以下步骤:

1. 打开工程:在Vivado中打开你的工程,如果使用原理图输入方式,你需要创建一个原理图文件。

2. 添加IP核:在原理图输入窗口,右键点击并选择“IP设置”(IP Settings),在此窗口中可以添加或删除IP核。

3. 选择IP核:点击“+”号添加IP,找到之前生成的IP核,通常它位于默认路径下。

4. 连接引脚:在添加IP核后,根据设计需要在原理图中连接相应的输入输出引脚。

通过以上步骤,你不仅了解了如何在Vivado中创建自定义IP核,还学会了如何在工程中调用这些IP核。这样的流程对于FPGA设计来说至关重要,因为它促进了设计的模块化和重用,提高了开发效率。在实际应用中,你可能还需要进行更深入的参数配置和验证,以确保IP核在目标系统中能正常工作。