没有合适的资源?快使用搜索试试~ 我知道了~

首页verilog的quartus简单教程.pdf

资源详情

资源推荐

Quartus

®

II Introduction for Verilog Users

This tutorial presents an introduction to the Quartus

®

II software. It gives a general overview of a typical CAD

flow for designing circuits that are implemented by using FPGA devices, and shows how this flow is realized in the

Quartus

®

II software. The design process is illustrated by giving step-by-step instructions for using the Quartus

®

II software to implement a simple circuit in an Altera

®

FPGA device.

The Quartus

®

II system includes full support for all of the popular methods of entering a description of the

desired circuit into a CAD system. This tutorial makes use of the Verilog design entry method, in which the

user specifies the desired circuit in the Verilog hardware description language. Another version of this tutorial is

available that uses VHDL hardware description language.

The screen captures in the tutorial were obtained using Quartus

®

II version 9.1; if other versions of the soft-

ware are used, some of the images may be slightly different.

Contents:

Getting Started

Starting a New Project

Design Entry Using Verilog Code

Compiling the Verilog Code

Using the RTL Viewer

Specifying Timing Constraints

Quartus

®

II Windows

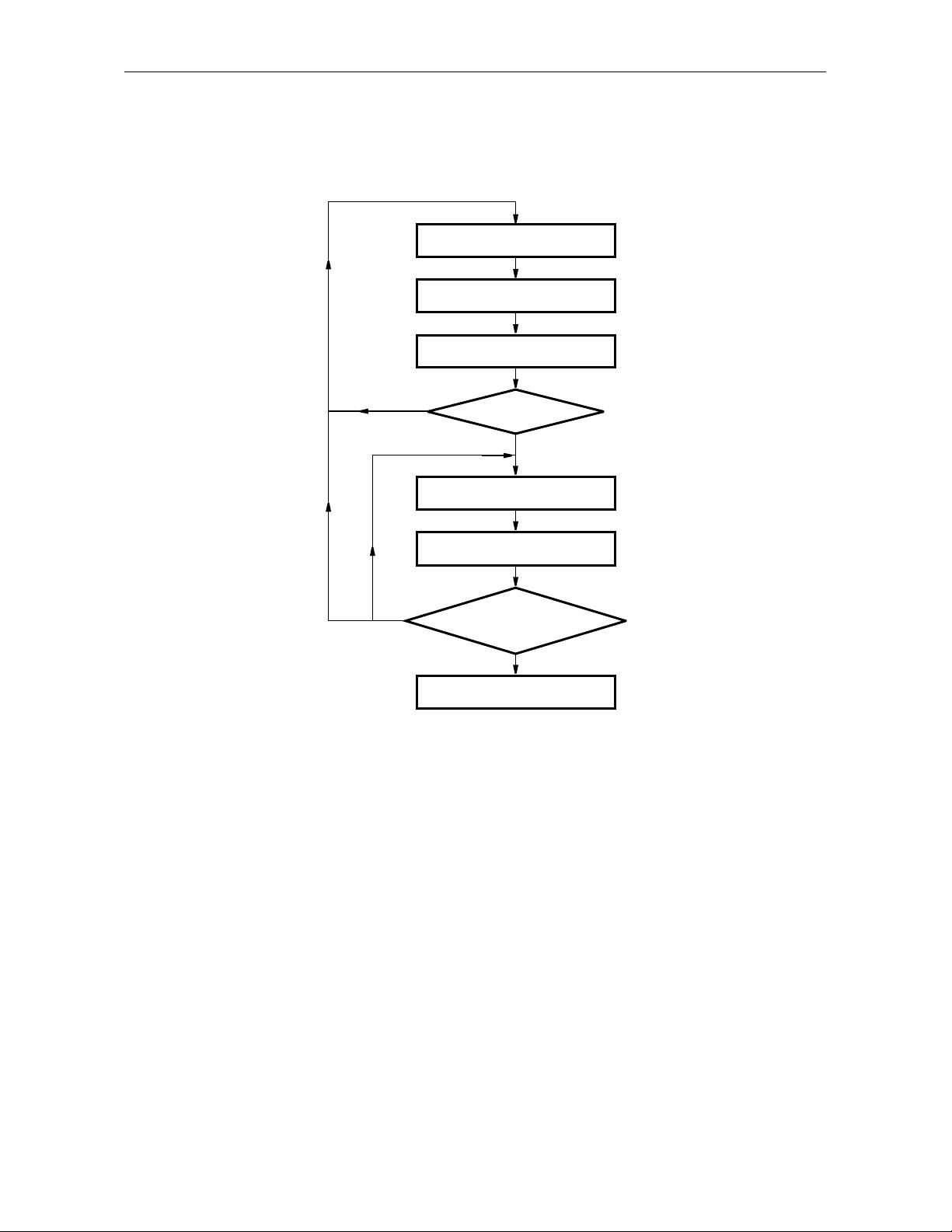

Computer Aided Design (CAD) software makes it easy to implement a desired logic circuit by using a pro-

grammable logic device, such as a field-programmable gate array (FPGA) chip. A typical FPGA CAD flow is

illustrated in Figure 1.

Design correct?

Functional Simulation

No

Yes

Synthesis

Timing requirements met?

Fitting

Timing Analysis and Simulation

Programming and Configuration

Yes

No

Design Entry

Figure 1: Typical CAD flow.

It involves the following basic steps:

• Design Entry – the desired circuit is specified either by using a hardware description language, such as

Verilog or VHDL, or by means of a schematic diagram

• Synthesis – the CAD Synthesis tool synthesizes the circuit into a netlist that gives the logic elements (LEs)

needed to realize the circuit and the connections between the LEs

• Functional Simulation – the synthesized circuit is tested to verify its functional correctness; the simulation

does not take into account any timing issues

• Fitting – the CAD Fitter tool determines the placement of the LEs defined in the netlist into the LEs in

an actual FPGA chip; it also chooses routing wires in the chip to make the required connections between

specific LEs

• Timing Analysis – propagation delays along the various paths in the fitted circuit are analyzed to provide

an indication of the expected performance of the circuit

ALTERA

®

CORPORATION

AUGUST 2009

2

QUARTUS

®

II INTRODUCTION FOR VERILOG USERS

• Timing Simulation – the fitted circuit is tested to verify both its functional correctness and timing

• Programming and Configuration – the designed circuit is implemented in a physical FPGA chip by pro-

gramming the configuration switches that configure the LEs and establish the required wiring connections

This tutorial introduces the basic features of the Quartus

®

II software. It shows how the software can be used to

design and implement a circuit specified using the Verilog hardware description language. It makes use of the

graphical user interface to invoke the Quartus

®

II commands. During this tutorial, the reader will learn about:

• Creating a project

• Synthesizing a circuit from Verilog code using the Quartus

®

II Integrated Synthesis tool

• Fitting a synthesized circuit into an Altera

®

FPGA

• Examining the report on the results of fitting and timing analysis

• Examining the synthesized circuit in the form of a schematic diagram generated by the RTL Viewer tool

• Making simple timing assignments in the Quartus

®

II software

ALTERA

®

CORPORATION

AUGUST 2009

3

QUARTUS

®

II INTRODUCTION FOR VERILOG USERS

1 GETTING STARTED

1 Getting Started

Each logic circuit, or subcircuit, being designed with the Quartus

®

II software is called a project. The soft-

ware works on one project at a time and keeps all information for that project in a single directory (folder)

in the file system. To begin a new logic circuit design, the first step is to create a directory to hold its files.

As part of the installation of the Quartus

®

II software, a few sample projects are placed into a directory called

altera\91\qdesigns\vhdl_verilog_tutorial. To hold the design files for this tutorial, we will use a directory called

quartus_tutorial. The running example for this tutorial is a simple adder/subtractor circuit, which is defined in the

Verilog hardware description language.

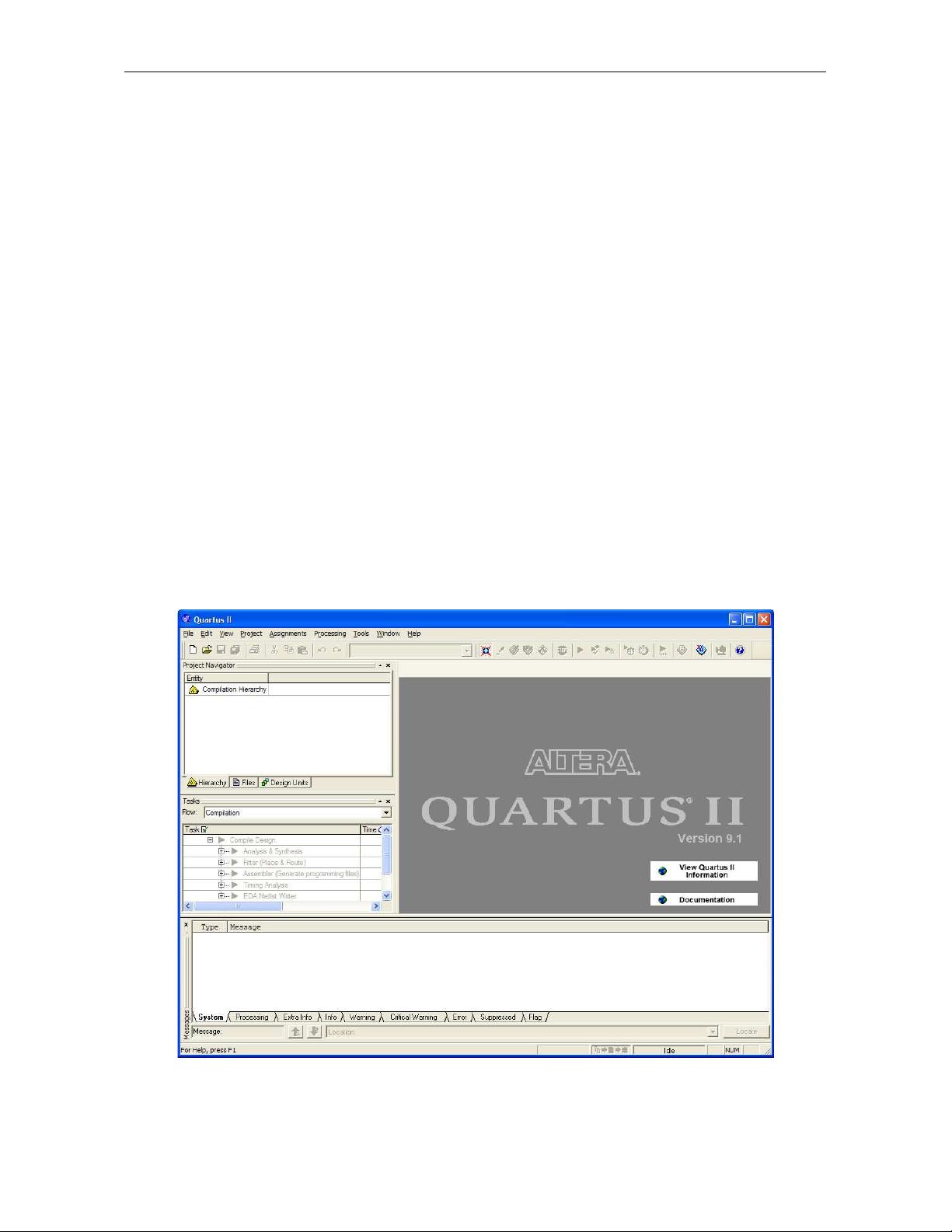

Start the Quartus

®

II software. You should see a display similar to the one in Figure 2. This display consists

of several windows that provide access to all the features of the Quartus

®

II software, which the user selects with

the computer mouse. Most of the commands provided by the Quartus

®

II software can be accessed by using a set

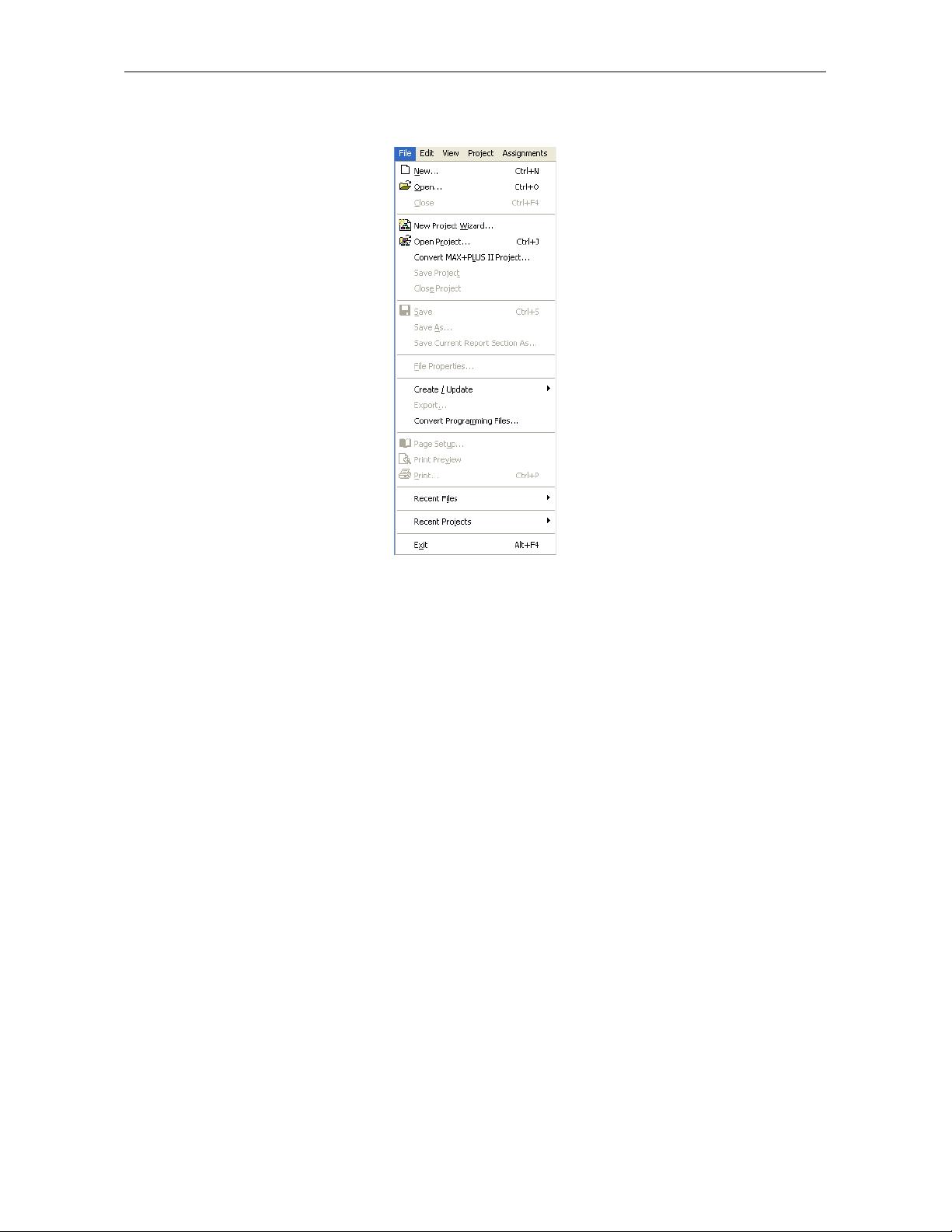

of menus that are located below the title bar. For example, in Figure 2 clicking the left mouse button on the menu

named File opens the menu shown in Figure 3. Clicking the left mouse button on the entry Exit exits from the

Quartus

®

II software. In general, whenever the mouse is used to select something, the left button is used. Hence

we will not normally specify which button to press. In the few cases when it is necessary to use the right mouse

button, it will be specified explicitly.

For some commands it is necessary to access two or more menus in sequence. We use the convention Menu1

> Menu2 > Item to indicate that to select the desired command the user should first click the left mouse button

on Menu1, then within this menu click on Menu2, and then within Menu2 click on Item. For example, File >

Exit uses the mouse to exit from the system. Many commands can be invoked by clicking on an icon displayed in

one of the toolbars. To see the list of available toolbars, select Tools > Customize > Toolbars. Once a toolbar is

opened, it can be moved using the mouse. To see the command associated with an icon, position the mouse over

the icon and a tooltip will appear that displays the command name.

It is possible to modify the appearance of the display in Figure 2 in many ways. Section 7 shows how to move,

resize, close, and open windows within the main Quartus

®

II display.

Figure 2: The main Quartus

®

II display.

ALTERA

®

CORPORATION

AUGUST 2009

4

QUARTUS

®

II INTRODUCTION FOR VERILOG USERS

1 GETTING STARTED 1.1 Quartus

®

II Online Help

Figure 3: An example of the File menu.

1.1 Quartus

®

II Online Help

The Quartus

®

II software provides comprehensive online documentation that answers many of the questions that

may arise when using the software. The documentation is accessed from the menu in the Help window. To get

some idea of the extent of documentation provided, it is worthwhile for the reader to browse through the Help

menu. For instance, selecting Help > How to Use Help gives an indication of what type of help is provided.

The user can quickly search through the Help topics by selecting Help > Search, which opens a dialog box

into which keywords can be entered. Another method, context-sensitive help, is provided for quickly finding

documentation about specific topics. While using most applications, pressing the F1 function key on the keyboard

opens a Help display that shows the commands available for the application.

ALTERA

®

CORPORATION

AUGUST 2009

5

QUARTUS

®

II INTRODUCTION FOR VERILOG USERS

剩余29页未读,继续阅读

竹涛如海

- 粉丝: 0

- 资源: 2

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 京瓷TASKalfa系列维修手册:安全与操作指南

- 小波变换在视频压缩中的应用

- Microsoft OfficeXP详解:WordXP、ExcelXP和PowerPointXP

- 雀巢在线媒介投放策划:门户网站与广告效果分析

- 用友NC-V56供应链功能升级详解(84页)

- 计算机病毒与防御策略探索

- 企业网NAT技术实践:2022年部署互联网出口策略

- 软件测试面试必备:概念、原则与常见问题解析

- 2022年Windows IIS服务器内外网配置详解与Serv-U FTP服务器安装

- 中国联通:企业级ICT转型与创新实践

- C#图形图像编程深入解析:GDI+与多媒体应用

- Xilinx AXI Interconnect v2.1用户指南

- DIY编程电缆全攻略:接口类型与自制指南

- 电脑维护与硬盘数据恢复指南

- 计算机网络技术专业剖析:人才培养与改革

- 量化多因子指数增强策略:微观视角的实证分析

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功