没有合适的资源?快使用搜索试试~ 我知道了~

首页Xilinx FPGA原语的使用方法pdf\Xilinx原语的使用方法2.pdf

Xilinx FPGA原语的使用方法pdf\Xilinx原语的使用方法2.pdf

Xilinx FPGA原语的使用方法pdf\Xilinx原语的使用方法2.pdf

资源详情

资源推荐

Xilinx 公司原语的使用方法 2

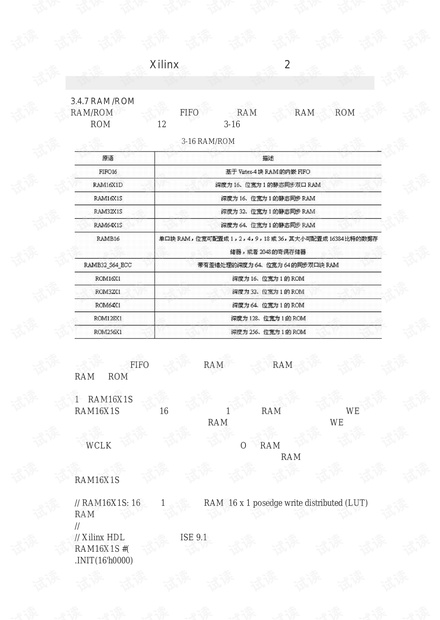

3.4.7 RAM/ROM 组件

RAM/ROM 组件可用于例化 FIFO、分布式 RAM、分布式 RAM、块 ROM 以

及块 ROM,具体包括 12 个组件,如表 3-16 所示。

表 3-16 RAM/ROM 原语列表

下面主要介绍 FIFO、分布式双口 RAM 以及块双口 RAM 原语的使用,单口

RAM 和 ROM 原语的用法类似,限于篇幅,就不再介绍。

1.RAM16X1S

RAM16X1S 是深度为 16 比特,位宽为 1 的同步 RAM。当写使能信号 WE

为低时,写端口的数据操作无效,RAM 内部的数据不会改变;当 WE 为高

时,可以在任意地址中写入比特。为了保证数据的稳定性,地址和数据应该

在 WCLK 的上升沿前保持稳定。输出信号 O 为 RAM 中由读地址信号所确

定的地址中所存数据的值。此外,还可通过属性指定 RAM 的初始值。

RAM16X1S 原语的例化代码模版如下所示:

// RAM16X1S: 16 比特 1 深度同步 RAM(16 x 1 posedge write distributed (LUT)

RAM)

// 适用芯片:所有芯片

// Xilinx HDL 库向导版本,ISE 9.1

RAM16X1S #(

.INIT(16'h0000)

//对 RAM 的内容进行初始化,这里初始化为全 1

) RAM16X1S_inst (

.O(O), // RAM output

.A0(A0), // RAM address[0] input

.A1(A1), // RAM address[1] input

.A2(A2), // RAM address[2] input

.A3(A3), // RAM address[3] input

.D(D), // RAM data input

.WCLK(WCLK), // Write clock input

.WE(WE) // Write enable input

);

// 结束 RAM16X1S 模块的例化过程

需要注意的是,RAM16X1S 原语是 Xilinx 独有的一类结构,在小数据量存

储方面非常节省资源。在综合结果分析时,RAM16X1S 原语的 RTL 结构如

图 3-45 所示。

图 3-45 原语 RAM16X1S 的 RTL 结构图

2.RAMB16

RAMB16 是 FPGA 芯片中内嵌的双口块 RAM,数据位宽可配置成 1、2、4、

9、18 以及 36 比特,每个块 RAM 的大小为 18 1024 比特,所以位宽越大,

深度越小。块 RAM 在 FPGA 中按照矩阵的方式排列,其数量完全取决于芯

片容量的大小。在使用中,可以添加坐标来约束块 RAM 的位置。例如:

LOC = RAMB16_X#Y#;

同样,也可以对块 RAM 完成初始化。块 RAM 是以硬核的方式内嵌到 FPGA

芯片中,不占用芯片的逻辑资源,是 FPGA 芯片内部非常宝贵的一种资源。

在工作时,要尽量使用芯片的块 RAM 资源,不仅能保证较高的工作频率,

还具有很低的动态功耗。

RAMB16 的 Verilog 例化代码如下所示。

// RAMB16: 块 RAM(Virtex-4 16k+2k Parity Paramatizable BlockRAM

// 适用芯片:Virtex-4 芯片

// Xilinx HDL 库向导版本,ISE 9.1

RAMB16 #(

.DOA_REG(0),

// A 端口可选的输出寄存器,可设置为 0 或 1,分别表示输出不寄存/寄存

.DOB_REG(0),

// B 端口可选的输出寄存器,可设置为 0 或 1,分别表示输出不寄存/寄存

.INIT_A(36'h000000000),

// 初始化 A 端口的输出初始值

.INIT_B(36'h000000000),

// 初始化 A 端口的输出初始值

.INVERT_CLK_DOA_REG("FALSE"),

// 反转 A 端口寄存器的时钟,可设置为"TRUE"或 "FALSE",分别表示不反

转/反转

.INVERT_CLK_DOB_REG("FALSE"),

// 反转 B 端口寄存器的时钟,可设置为"TRUE"或 "FALSE",分别表示不反

转/反转

.RAM_EXTENSION_A("NONE"),

// RAM 的 A 端口扩展选项,可设置为"UPPER"、"LOWER"或 "NONE",分

别表示作为// 高字节、低字节级联,或者不扩展

.RAM_EXTENSION_B("NONE"),

// RAM 的 B 端口扩展选项.READ_WIDTH_A(0),同 A 端口

.READ_WIDTH_A(0),

// A 端口的数据读取宽度,有效值为 1, 2, 4, 9, 18, 或 36

.READ_WIDTH_B(0),

// B 端口的数据读取宽度,有效值为 1, 2, 4, 9, 18, 或 36

.SIM_COLLISION_CHECK("ALL"),

// 碰撞检测使能信号,可设置为"ALL"、"WARNING_ONLY"、

"GENERATE_X_ONLY" // 或者"NONE"

.SRVAL_A(36'h000000000),

// 复位后 A 端口的输出值

.SRVAL_B(36'h000000000),

//复位后 A 端口的输出值

.WRITE_MODE_A("WRITE_FIRST"),

// A 端口的写模式,可设置为"WRITE_FIRST", "READ_FIRST", 或

"NO_CHANGE"

.WRITE_MODE_B("WRITE_FIRST"),

// B 端口的写模式,可设置为"WRITE_FIRST", "READ_FIRST", 或

"NO_CHANGE"

.WRITE_WIDTH_A(2),

// A 端口的数据写入宽度,有效值为 1, 2, 4, 9, 18, 或 36

.WRITE_WIDTH_B(0),

// B 端口的数据写入宽度,有效值为 1, 2, 4, 9, 18, 或 36

// 下列 INIT_xx 声明用于指定 RAM 的初始化内容

.INIT_00(256'h0000000000000000000000000000000000000000000000000000

000000000000),

剩余13页未读,继续阅读

hglikun

- 粉丝: 3

- 资源: 47

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- zigbee-cluster-library-specification

- JSBSim Reference Manual

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功