FPGA设计全攻略:从Modelsim到Synplify.Pro

需积分: 12 15 浏览量

更新于2024-09-11

收藏 236KB PDF 举报

"该资源详细介绍了FPGA设计的全流程,包括使用Modelsim编译Xilinx库、调用Xilinx CORE-Generator生成IP核、Synplify.Pro进行综合以及后续的项目执行和仿真等关键步骤。"

在FPGA设计中,全流程通常涉及多个紧密相连的阶段,确保设计的有效性和高效性。以下是对每个阶段的详细说明:

1. **Modelsim编译Xilinx库**

Modelsim是一款常用的硬件描述语言(HDL)仿真器,用于验证设计的正确性。在使用Modelsim进行FPGA设计之前,需要先编译Xilinx提供的库,如simprims、unisims和XilinxCoreLib。这些库包含了Xilinx FPGA内部结构的模型,以便在仿真时能准确模拟实际器件的行为。创建一个专门的目录存放这些库,并在Modelsim环境中指定这个目录,然后逐个编译这三个库。

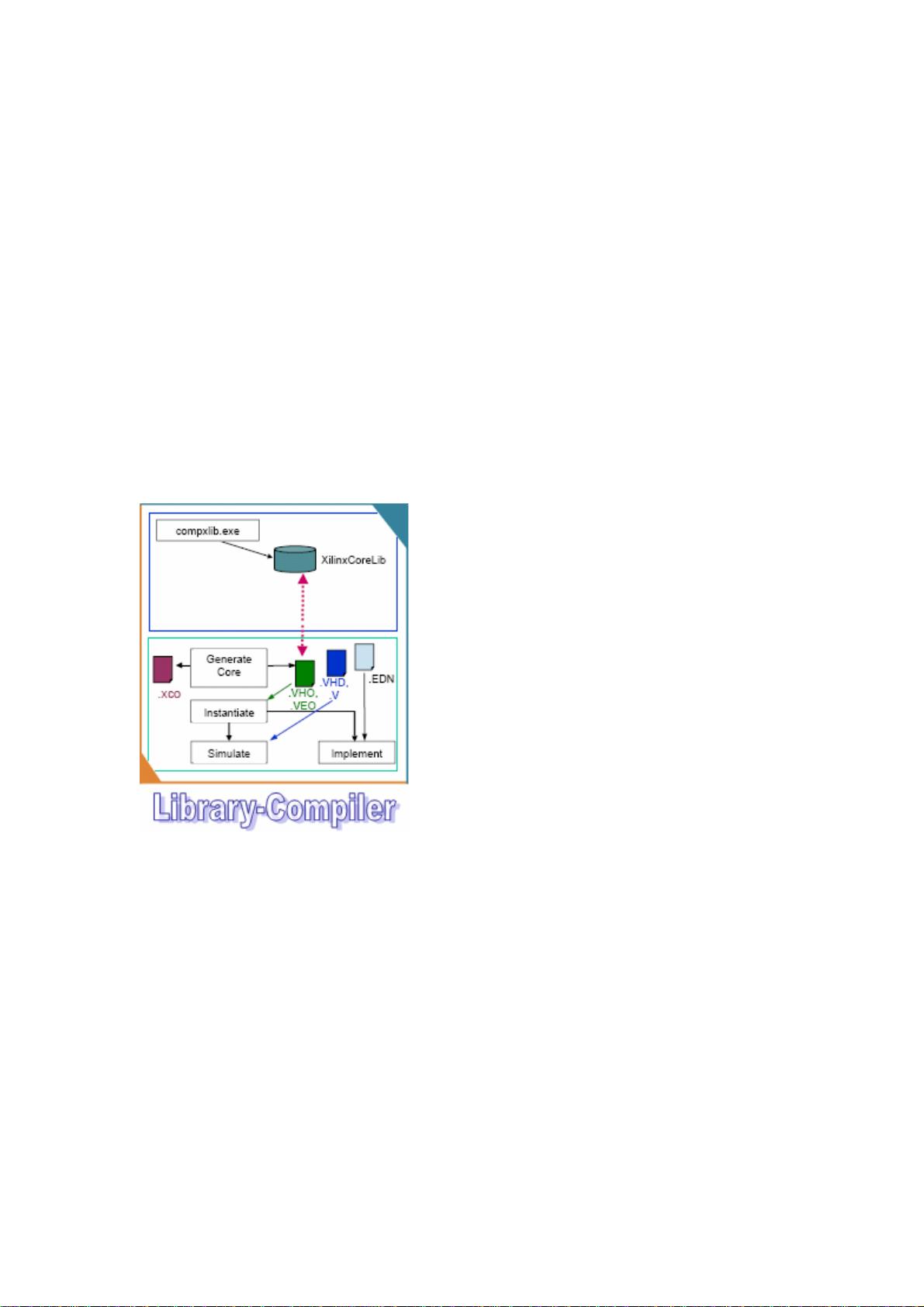

2. **调用Xilinx CORE-Generator**

Xilinx CORE-Generator是一个强大的工具,允许设计师自定义和生成各种参数化的IP核,包括数字信号处理(DSP)模块、存储器接口、时钟管理单元等。用户可以通过图形界面或HDL代码来配置IP核,然后CORE-Generator会生成相应的Verilog或VHDL代码,这些代码可以直接集成到设计中。

3. **使用Synplify.Pro综合HDL和内核**

综合是将高级语言描述(如Verilog或VHDL)转换为门级网表的过程。Synplify.Pro是一款高效的综合工具,它可以优化设计,减少逻辑资源的使用,提高速度。在这一阶段,设计师将编写好的HDL代码和CORE-Generator生成的IP核输入到Synplify.Pro中,进行逻辑优化和映射,得到适配目标FPGA架构的门级网表。

4. **综合后的项目执行**

综合完成后,生成的网表会被导入到Xilinx的集成开发环境ISE中,进行布局布线。布局布线器会根据FPGA的物理特性将逻辑门分配到特定的逻辑单元和I/O引脚上,同时考虑功耗、时序约束等因素。

5. **不同类型结构的仿真**

在设计流程的最后阶段,会进行功能仿真和时序仿真,以确保设计在实际硬件上的行为正确且满足性能要求。功能仿真检查设计逻辑是否正确,而时序仿真则评估设计在给定时钟周期下的性能,包括最大工作频率和时序裕量。

每个阶段都至关重要,设计师需要理解每个工具的功能和操作,以确保设计的成功实现。此外,还需要注意时序约束的设置、功耗优化、面积优化等方面,以达到最佳的设计效果。在整个流程中,良好的文档管理和版本控制也是必不可少的,以确保设计的可维护性和团队协作的效率。

点击了解资源详情

155 浏览量

点击了解资源详情

2022-09-23 上传

2011-04-09 上传

2009-03-17 上传

384 浏览量

点击了解资源详情

点击了解资源详情

lovermm123

- 粉丝: 0

- 资源: 3