优化高速PCB电源地噪声设计策略

需积分: 9 77 浏览量

更新于2024-08-13

收藏 248KB DOC 举报

高速电路PCB的电源地噪声设计是一项关键任务,因为在高速电子系统中,噪声可能导致信号质量下降、性能受损甚至设备间电磁兼容性(EMC)问题。本文将深入探讨电源系统的阻抗特性、谐振效应以及如何通过有效的设计策略来减少噪声。

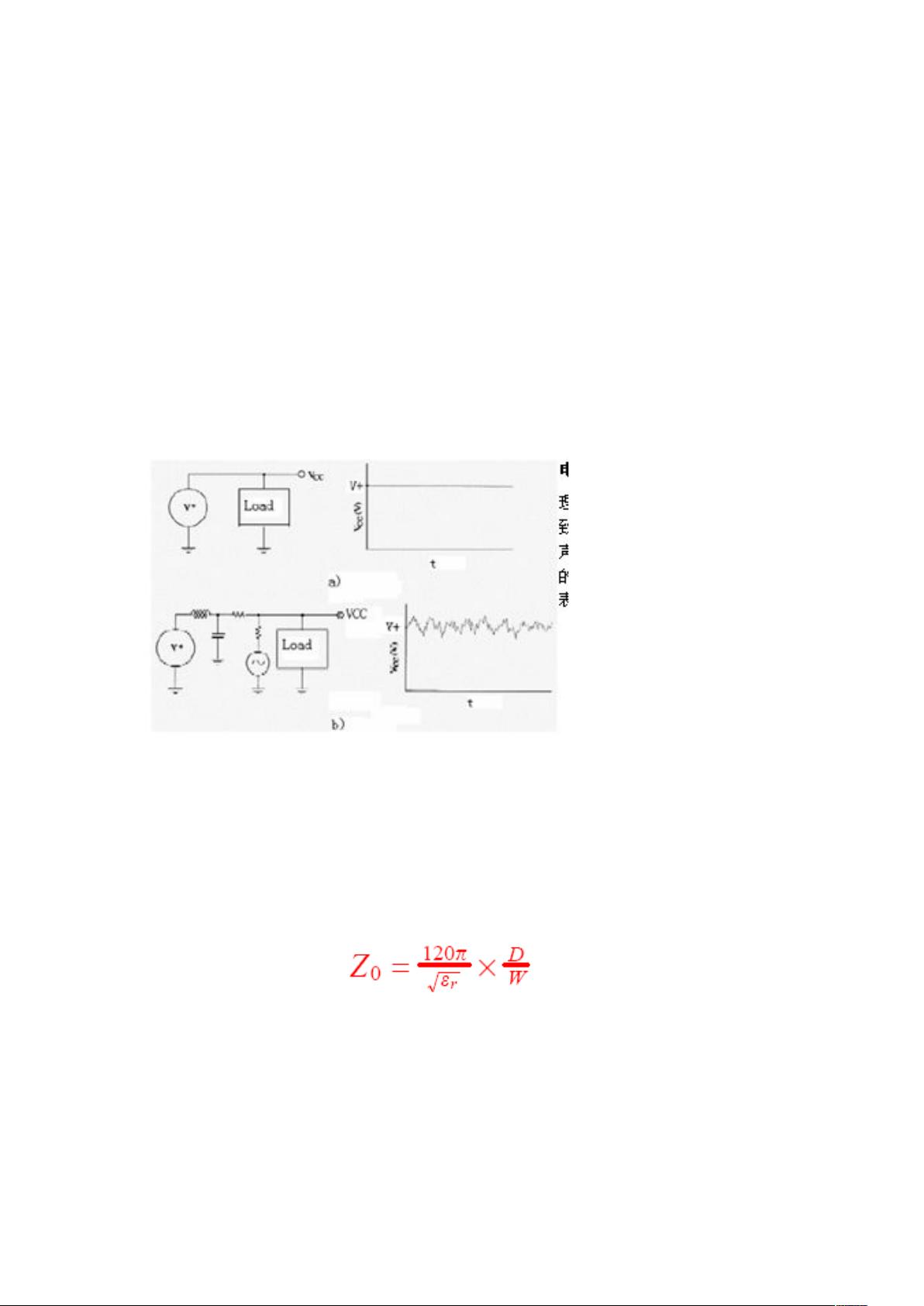

首先,理解电源系统的阻抗至关重要。理想情况下,电源阻抗应接近零,这样可以保证电压传输的完整性。然而,在实际应用中,电源由电阻、电感和电容组成,形成非零阻抗,如图1所示。在PCB设计中,通常采用电源地平面作为低阻抗电源分配方式,但必须注意的是,当工作频率接近地平面的谐振频率时,其阻抗会显著升高,形成潜在的干扰源。

对于高速电路板,特别是在小型板子上,由于物理尺寸限制,谐振频率可能会较高,如6cm×6cm板子的第一个谐振频率可能在800MHz左右。噪声来源包括纹波与开关电源的高频干扰、高速总线的瞬态噪声(如过冲、振铃和串扰)、器件辐射发射、电源地反弹以及大功率模拟电路如功放和大电流继电器产生的噪声。

开关电源由于其高效但纹波较大的特性,在高要求的应用中,如使用LC滤波器可以有效减小高频噪声。相比之下,线性电源虽然干扰较小,但效率较低且功率损耗大,通常仅需电容滤波就能满足需求。因此,在设计过程中,工程师需要平衡电源的噪声水平、效率和功率消耗,以确保系统的稳定性和可靠性。

设计策略包括优化电源层叠布局,比如使用屏蔽层来减少辐射,使用多层电源地平面来分散噪声,以及选择合适的滤波技术。同时,信号走线应遵循合理的布线规则,如保持最小的回路面积和最短的路径,以减小串扰和反射。在可能的情况下,选择低噪声的元器件,并进行合理的电源分配,以降低噪声对系统的影响。

总结来说,高速电路PCB的电源地噪声设计需要深入了解电源阻抗特性、谐振效应,以及针对不同噪声源采取针对性的解决方案,以实现最佳的信号质量和系统性能。通过综合考虑设计策略和技术手段,可以显著提升高速电路板的整体性能和可靠性。

2020-10-15 上传

2023-10-15 上传

2023-09-24 上传

2023-10-05 上传

2023-06-26 上传

2023-03-07 上传

2023-08-16 上传

2023-03-31 上传

2023-11-20 上传

weixin_38662367

- 粉丝: 4

- 资源: 912

最新资源

- 解决本地连接丢失无法上网的问题

- BIOS报警声音解析:故障原因与解决方法

- 广义均值移动跟踪算法在视频目标跟踪中的应用研究

- C++Builder快捷键大全:高效编程的秘密武器

- 网页制作入门:常用代码详解

- TX2440A开发板网络远程监控系统移植教程:易搭建与通用解决方案

- WebLogic10虚拟内存配置详解与优化技巧

- C#网络编程深度解析:Socket基础与应用

- 掌握Struts1:Java MVC轻量级框架详解

- 20个必备CSS代码段提升Web开发效率

- CSS样式大全:字体、文本、列表样式详解

- Proteus元件库大全:从基础到高级组件

- 74HC08芯片:高速CMOS四输入与门详细资料

- C#获取当前路径的多种方法详解

- 修复MySQL乱码问题:设置字符集为GB2312

- C语言的诞生与演进:从汇编到系统编程的革命