PCIe总线FPGA设计技术解析

需积分: 10 76 浏览量

更新于2024-10-17

收藏 617KB PDF 举报

"本文介绍了PCIE总线的FPGA设计方法,包括采用第三方PHY接口器件和低成本FPGA的实现方案,并对比了两者的优缺点。"

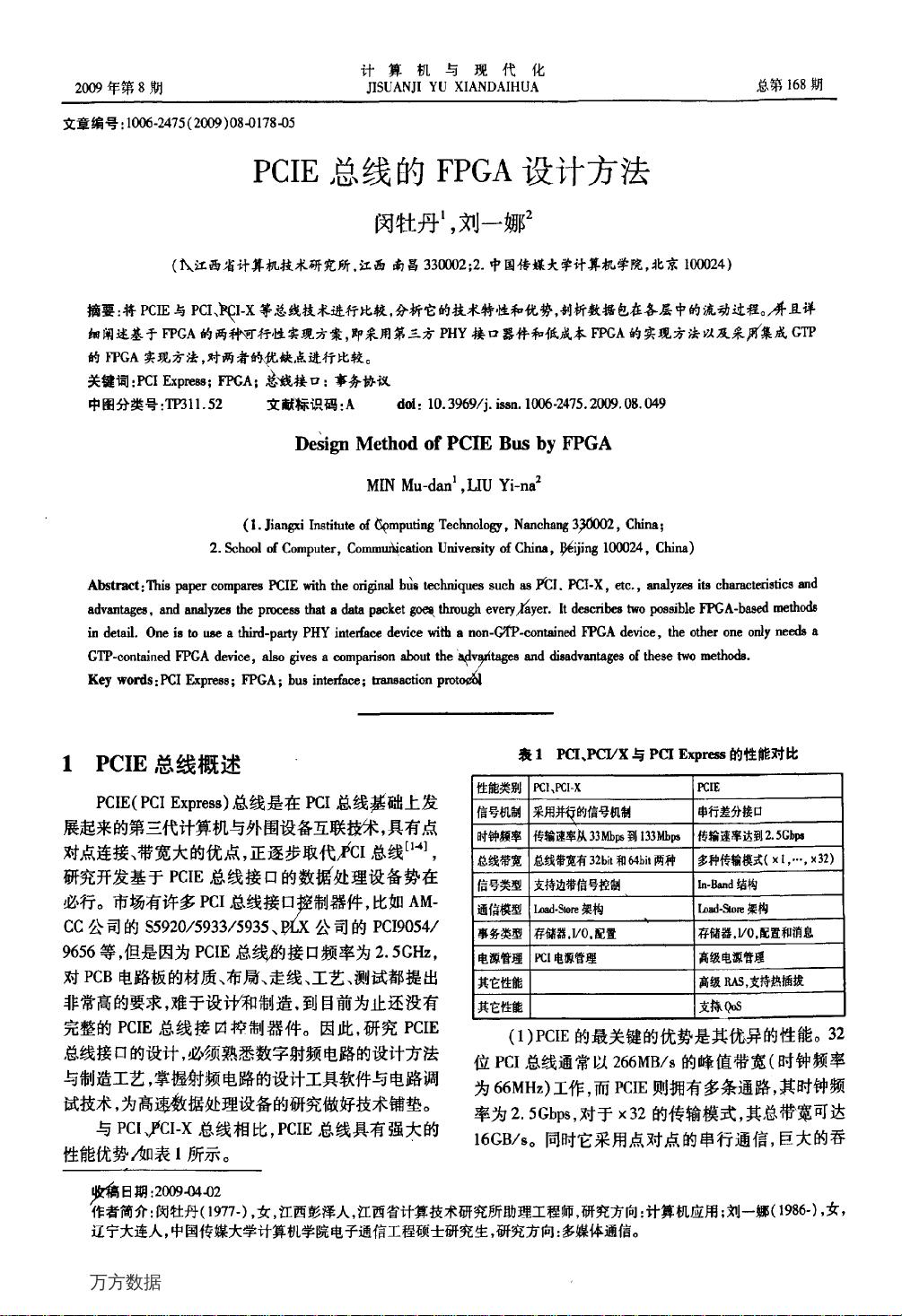

PCI Express(PCIE)是一种高速串行计算机扩展总线标准,它在传输速率、带宽效率和低延迟方面优于传统的PCI和PCI-X总线。PCIE采用点对点连接方式,每个设备都有独立的数据通道,通过分层的协议结构来处理数据传输,包括物理层(PHY)、链路层(Link Layer)和交易层(Transaction Layer)。数据包在这些层中进行编码、解码和错误检测,确保数据的可靠传输。

FPGA(Field-Programmable Gate Array)是可编程逻辑器件,能灵活地实现各种数字逻辑功能,因此在PCIE设计中扮演重要角色。使用FPGA设计PCIE接口主要有以下两种方法:

1. 采用第三方PHY接口器件的实现方法:这种方法通常适用于高性能应用,因为独立的PHY器件可以提供优化的信号质量和稳定性。第三方PHY提供了与PCIE物理层标准兼容的接口,FPGA主要负责处理链路层和交易层的协议。这种方式的优点是性能出色,但成本较高,且需要更多的电路板空间。

2. 低成本FPGA实现方法:这种方法适合预算有限或对尺寸有严格要求的设计。一些现代FPGA内置了PCIE PHY,可以减少外部组件的需求,从而降低成本和板级空间。然而,这种方法可能会牺牲一些性能,因为内置PHY可能不如专用器件优化。

在选择实现方案时,需要权衡性能、成本和设计复杂度。采用第三方PHY的方案可能需要更复杂的时序约束和调试,而内置PHY的FPGA设计则简化了硬件集成,但可能需要更深入地理解FPGA内部工作原理。

PCIE总线的FPGA设计涉及到多层协议栈的理解和实现,包括物理层的信号传输规范、链路层的通信管理和交易层的数据包转换。通过FPGA,设计者可以根据具体需求定制高效的PCIE接口,以满足不同应用场景的性能和成本要求。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-07-13 上传

2022-11-27 上传

2021-07-13 上传

2021-07-13 上传

cglict

- 粉丝: 4

- 资源: 4

最新资源

- The Next 700 Programming Languages

- 2009年上半年信息系统监理师上午题。

- 2009年上半年信息处理技术员上午题

- AT&T asm guide for newbie

- DSP开发板电路原理图之主图

- 管理软件的实施与销售

- The estimation of synergy or antagonism

- Measuring additive interaction using odds ratios

- 数据库课程设计126个经典题

- 【启动项目就是开机的时候系统会在前台或者后台运行的程序】

- 云母填充改性聚乙烯的初步研究

- 某高校学生学籍管理信息系统设计与开发

- 编程相关日语词汇(PDF格式)

- Ubuntu中文参考手册

- 计算机网络 第四版 习题答案 谢希仁

- J2ME手机游戏开发技术详解