ZYNQ PL端SGMII网口扩展与PS控制调试详解

版权申诉

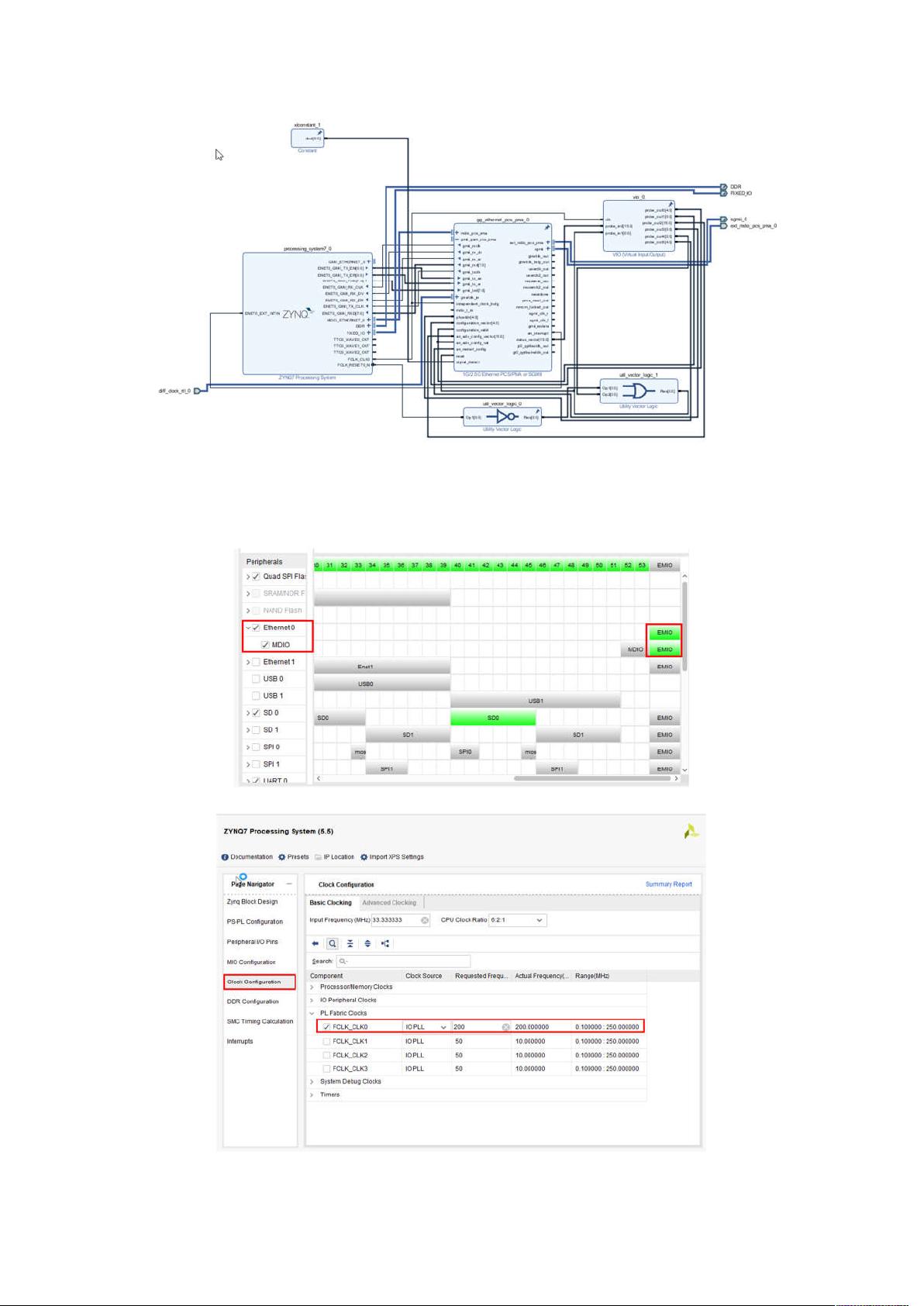

本文档详细介绍了在ZYNQ系列XC7Z045芯片上,如何通过程序逻辑部分(PL)利用System Generator IP核实现SGMII网口的扩展,以便于PS端网络控制器控制,从而支持千兆网通信。ZYNQ的PS端原生支持GMII或RGMII接口,但不直接支持SGMII,因此需要通过PS端的EMIO接口映射GMII到PL,利用PL上的1G/2.5G Ethernet PCS/PMA或SGMII IP核进行协议转换。

系统设计流程包括以下几个关键步骤:

1. **系统结构**:

- 主要使用XC7Z045 Zynq芯片作为核心处理器,其PL部分通过高速接口GTX连接外部PHY芯片,如88E1111,该PHY支持SGMII电接口模式。

- 88E1111的MDIO接口不再需要,因为PHY已经配置为SGMII模式,简化了网络配置过程。

- 整体系统架构包含PS端的U-Boot和Linux操作系统,以及PL端的网口接口转换逻辑。

2. **PL端设计**:

- 采用Top层连线的方式,利用ZYNQ的PL设计了一个IP核,将GMII协议转换为SGMII,以便与PHY芯片相兼容。

- 高速接口GTX的设计是关键技术,它负责物理信号的传输和处理,确保数据的有效交换。

3. **PS端工作**:

- PS端的U-Boot和Linux内核需要进行相应修改,以支持通过EMIO映射的GMII接口与PL通信,然后由PL处理SGMII数据。

- U-Boot的合成与下载使用了Vivado 2018.2工具,而Linux内核则基于Xilinx官方提供的源码。

4. **测试与验证**:

- 作者亲自进行了系统测试,包括在U-Boot和Linux内核环境下执行ping指令,以确认网络通信的正常工作。

通过这个过程,ZYNQ的PL端扩展SGMII网口实现了对高速网络通信的支持,且无需额外复杂的MDIO配置,提高了系统的灵活性和易用性。这对于在嵌入式系统和FPGA应用中扩展网络功能具有重要的实践参考价值。

4366 浏览量

2529 浏览量

点击了解资源详情

点击了解资源详情

201 浏览量

126 浏览量

点击了解资源详情

点击了解资源详情

少林and叔叔

- 粉丝: 7547

最新资源

- Essential C++中文版配套程序深度解析

- 网页优化利器:多余CSS清除工具发布

- 深入解析projeto-html-css3项目中的HTML与CSS3应用

- AJAX技术实现表单提交的具体实例解析

- 易语言MySql5.0类模块源码:数据库操作与连接指南

- LBP与SVM结合的实验数据分析

- LINUX与UNIX Shell编程指南参考文档

- 阎石数电第五版第六至十一章学习资料

- CVX工具包:基于Matlab的凸优化解决方案

- ESP8266微控制器编程教程与固件刷新指南

- 易语言硬件信息模块源码解析与应用

- FC/NES交叉汇编器Vikings1.3版发布,一万行代码重定义汇编方式

- 线上数据模型维护与数据治理平台应用方法专利

- 网页设计神器:虚拟尺屏测量工具

- 基于Cocoa的Document-Base应用视图切换方法

- 高级PID算法集合:神经网络PID与模糊PID解析