【ZYNQ连接无忧】:PL端SGMII网口连接问题的快速解决方案

发布时间: 2025-01-02 19:44:40 阅读量: 5 订阅数: 10

# 摘要

本文系统地介绍了ZYNQ平台下SGMII网口的基础知识和连接理论,详细阐述了SGMII协议的历史、工作原理及特点,并探讨了在ZYNQ平台上的网络协议栈架构及其各层协议的实现方式。进一步地,本文深入分析了SGMII连接过程中的问题诊断和分析方法,包括硬件配置和初始化、常见问题及故障排除策略。通过实践案例,展示了如何在ZYNQ的PL端配置和优化SGMII连接,并提供了高级解决方案,如使用先进诊断工具和软件监控调试技术。文章最后讨论了SGMII连接的持续维护和升级策略,以确保长期稳定的网络性能和可靠性。

# 关键字

ZYNQ;SGMII协议;网络协议栈;硬件配置;故障诊断;性能优化

参考资源链接:[ZYNQ PL端SGMII网口扩展与PS控制调试详解](https://wenku.csdn.net/doc/6xisjeyhzk?spm=1055.2635.3001.10343)

# 1. ZYNQ与SGMII网口的基础知识

## 1.1 ZYNQ平台简介

ZYNQ平台是由Xilinx开发的一款独特的处理器平台,它集成了ARM处理器核心和可编程逻辑阵列(FPGA)于单颗芯片中。这种集成结构使得ZYNQ能够提供高性能计算和灵活的硬件自定义功能,适用于广泛的嵌入式和网络应用。

## 1.2 SGMII接口概述

SGMII(Serial Gigabit Media Independent Interface)是一种用于在物理层上实现10/100/1000Mb/s以太网通信的串行接口标准。它广泛应用于网络设备中,特别是那些需要高速数据传输的应用,如交换机和路由器。

## 1.3 ZYNQ与SGMII的结合

在ZYNQ平台上实现SGMII接口,能够提供高性能的数据传输能力,这对于需要处理大量数据的嵌入式系统尤为重要。通过在ZYNQ的PL(可编程逻辑)区域实现SGMII接口,开发者可以利用FPGA的灵活性,来优化和定制网络协议栈的性能。

为了充分利用SGMII接口在ZYNQ平台上的潜力,开发人员需要了解基础的硬件设计和网络协议栈的工作原理。接下来的章节将深入探讨SGMII的理论基础和ZYNQ平台上的实现。

# 2. SGMII网口连接的理论基础

### 2.1 SGMII协议简介

#### 2.1.1 SGMII的历史和应用背景

Serial Gigabit Media Independent Interface (SGMII) 是一种串行接口标准,主要用于高速串行数据通信。SGMII协议基于IEEE 802.3标准,针对1000BASE-X Serdes 设计,广泛应用于千兆以太网设备。SGMII 的诞生是为了降低高速网络连接的成本,简化硬件设计。

SGMII 可以在单一双绞线上实现1000Mbps的数据传输率,相比传统的并行接口,其所需的I/O数量更少,线路之间的串扰也更小,因此,它被普遍应用于FPGA(现场可编程门阵列)和ASIC(专用集成电路)等设备的高速串行通信接口。

SGMII 连接的实现通常需要在FPGA内部或外部实现相应的SerDes(串行器/解串器)逻辑,这使得设计者能够利用SGMII实现千兆级别的以太网通信能力。

#### 2.1.2 SGMII的工作原理和主要特点

SGMII 工作原理涉及到电信号的串行发送和接收。SGMII接口通过在物理层使用差分信号(通常为LVDS,即低压差分信号)来传输数据。在这种机制下,数据不是并行传输,而是串行地逐位发送,每个时钟周期传输一位数据。

SGMII 的主要特点包括:

1. 高速数据传输:SGMII 支持高达1Gbps的数据传输速率。

2. 低功耗设计:由于使用差分信号,SGMII 可以在较低的电压下工作,降低功耗。

3. 灵活的物理接口:SGMII 可以用在FPGA内部SerDes以及外部物理层设备上。

4. 降低材料成本:SGMII 减少了所需的I/O引脚数量,因此可以减少系统成本。

### 2.2 ZYNQ平台上的网络协议栈

#### 2.2.1 ZYNQ网络协议栈的架构

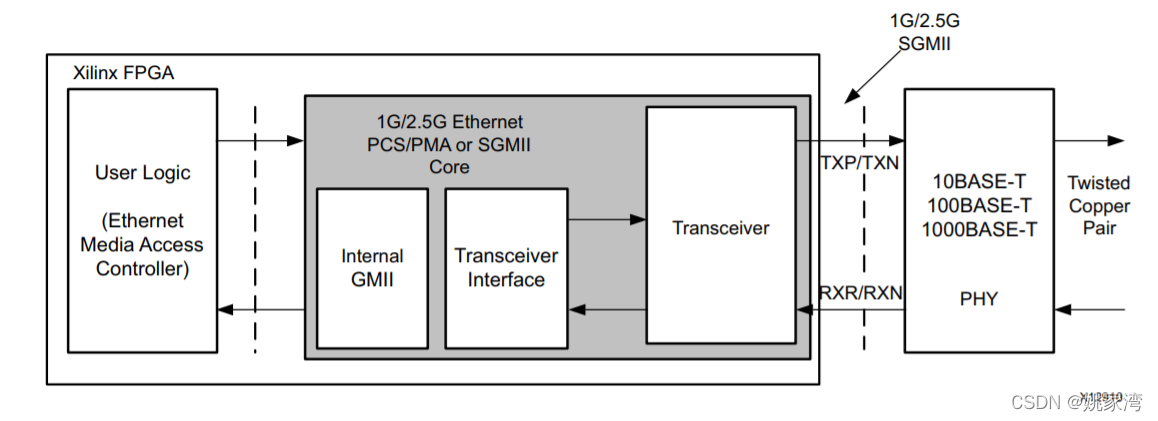

ZYNQ平台由ARM处理器和FPGA两部分组成。在ZYNQ平台的网络协议栈中,ARM部分运行标准的Linux网络协议栈,负责处理IP层以上的数据包处理;而FPGA部分则通过SGMII接口与网络物理设备连接,处理以太网帧的封装与解析,保证高速数据传输。

协议栈的这种设计充分利用了ARM的处理能力和FPGA的硬件加速能力。ARM处理器负责复杂的网络协议处理,如TCP/IP协议,而FPGA则负责高速数据吞吐,两者通过接口桥接协同工作。

#### 2.2.2 各层协议在ZYNQ上的实现方式

在ZYNQ平台上,各层协议的实现方式可以分为以下几个层次:

1. **物理层**:通过SGMII接口实现,负责将比特流通过电信号的方式进行发送和接收。

2. **数据链路层**:在FPGA上实现的MAC(媒体访问控制)子层处理MAC帧,包括帧的封装、错误检测、地址识别等功能。

3. **网络层和传输层**:在ARM核心的Linux系统中实现,处理IP包的路由、分片、重组以及TCP/UDP端口的管理等功能。

4. **应用层**:同样在ARM核心的Linux系统中实现,处理HTTP、FTP、DNS等应用层协议。

### 2.3 SGMII连接的硬件配置

#### 2.3.1 硬件连接方式

SGMII 连接通常涉及到一组差分信号线,包括一对发送线(TXP/TXN)和一对接收线(RXP/RXN)。在ZYNQ平台与网络物理设备(如PHY芯片或光收发器)之间的连接需要确保正确的差分对配对。

硬件连接通常使用以下方式:

- **直接连接**:ZYNQ的SGMII接口直接与PHY芯片连接。

- **通过变压器**:如果使用的是变压器耦合方式,需要确保变压器的类型和匹配阻抗,这样可以实现更好的信号完整性。

- **使用电平转换器**:在某些情况下,可能需要使用电平转换器来适配不同电平标准的芯片。

#### 2.3.2 硬件初始化过程

SGMII 的硬件初始化涉及到FPGA内部的配置以及与物理层设备的同步过程。以下是一个简化的初始化过程:

1. **FPGA配置加载**:首先,FPGA需要加载包含SGMII接口逻辑的配置文件。

2. **PHY芯片复位**:通过PHY芯片的复位引脚使其复位到初始状态。

3. **自动协商**:FPGA通过SGMII接口与PHY芯片进行自动协商,确定链接速率、双工模式等参数。

4. **链接建立**:一旦参数协商完成,SGMII链接就建立了,数据就可以开始发送和接收。

硬件初始化过程中可能涉及的故障排查方法包括:

- 使用逻辑分析仪检查SGMII接口的信号质量。

- 确认PHY芯片的固件是否为最新版本,并且与ZYNQ平台兼容。

- 检查电源供应是否稳定,以保证硬件的正常工作。

```mermaid

graph LR

A[启动FPGA] --> B[加载SGMII配置]

B --> C[复位PHY芯片]

C --> D[自动协商链接参数]

D --> E[建立SGMII链接]

```

```mermaid

sequenceDiagram

participant Z as ZYNQ

participant P as PHY芯片

participant U as 用户

U->>Z: 开机或重启

Z->>P: 加载配置并复位

P->>P: 自

```

0

0