【ZYNQ维护与升级】:PL端SGMII网口的维护和升级最佳实践

摘要

本文旨在深入探讨ZYNQ平台中SGMII网口的实现、维护与升级策略。首先介绍了ZYNQ和SGMII网口的基础知识,包括SGMII协议的工作原理及信号标准,以及ZYNQ平台如何在硬件层面上实现SGMII网口。接着,本文详细论述了维护SGMII网口的最佳实践,包括故障诊断、问题定位、维护工具选择以及硬件测试步骤。文章还提供了升级SGMII网口时的详细流程,强调了系统备份、风险评估以及软件和硬件升级的注意事项。通过分析具体实践案例,本文总结了维护和升级过程中的成功经验、挑战及应对策略,并对未来的ZYNQ技术和SGMII网口应用趋势进行了展望。

关键字

ZYNQ平台;SGMII网口;故障诊断;维护策略;系统升级;最佳实践

参考资源链接:ZYNQ PL端SGMII网口扩展与PS控制调试详解

1. ZYNQ和PL端概述

1.1 ZYNQ技术简介

ZYNQ是一种高度集成的自定义可编程逻辑系统芯片(SoC),将ARM处理器核心和可编程逻辑资源(FPGA)集成在同一芯片上。这种结构允许设计者利用ARM处理器强大的处理能力和灵活的FPGA硬件资源,以实现高性能和高灵活性的系统设计。

1.2 ZYNQ中的PL端

在ZYNQ中,PL(Programmable Logic)端指的是FPGA部分,它允许设计者通过硬件描述语言(HDL)来实现各种硬件逻辑和功能。与处理器端(PS, Processing System)相比,PL端在数据处理、接口功能实现及并行运算方面具有明显优势,使得ZYNQ SoC成为实现高效能嵌入式系统的关键技术之一。

1.3 应用领域和优势

ZYNQ技术广泛应用于通信、图像处理、工业控制、机器视觉等领域。它之所以备受欢迎,主要是因为其能够提供系统级的集成,降低硬件复杂性,缩短产品开发周期,并具有出色的性能和灵活性。通过PL端的定制化设计,开发者可以将特定的功能直接映射到硬件层面,从而提高整体系统的性能。

2. SGMII网口的基础知识

2.1 SGMII网口的工作原理

2.1.1 SGMII协议简介

串行千兆媒体独立接口(Serial Gigabit Media Independent Interface,简称SGMII)是一种基于差分对传输的串行接口标准,常用于实现千兆以太网(Gigabit Ethernet)的物理层。SGMII协议将物理层(PHY)与媒体访问控制器(MAC)进行接口,以串行方式传输数据,提供比传统并行接口更低的功耗和更简单的布线要求,因此被广泛应用于FPGA和ASIC设计中。

SGMII协议是IEEE 802.3标准的一部分,能够支持全双工的1000BASE-X千兆以太网操作。在ZYNQ等可编程逻辑设备中,SGMII接口不仅可以实现与外部PHY芯片的连接,还能提供与高速串行收发器(SerDes)的直接通信,从而简化了网络接口的硬件设计。

2.1.2 信号和接口标准

SGMII接口使用两对差分信号线来实现数据的发送和接收(TX和RX),以及一对用于时钟恢复的差分信号线。每一组信号线都是高速差分对,能够在高速传输中保持更好的信号完整性和抗干扰能力。

接口标准通常遵循以下要求:

- 全双工操作,支持1.25Gbps的线速传输;

- 使用低压差分信号(LVDS)或低电压正发射极耦合逻辑(LVPECL)电平;

- 为接收器提供参考时钟信号,允许PHY器件锁定到正确的数据速率。

为了保证通信的可靠性,SGMII协议还规定了信号的电气特性和时序要求。为了减少信号的串扰和反射,设计时需要考虑信号的阻抗匹配、终端匹配和布局布线等因素。

2.2 ZYNQ中SGMII网口的实现

2.2.1 ZYNQ平台架构

ZYNQ是一种将ARM处理器核心与FPGA逻辑资源集成在同一芯片上的异构计算平台。它通过集成的双核ARM Cortex-A9处理器、丰富的FPGA逻辑单元以及高性能的内存管理系统,为用户提供了高度灵活的可编程系统集成解决方案。

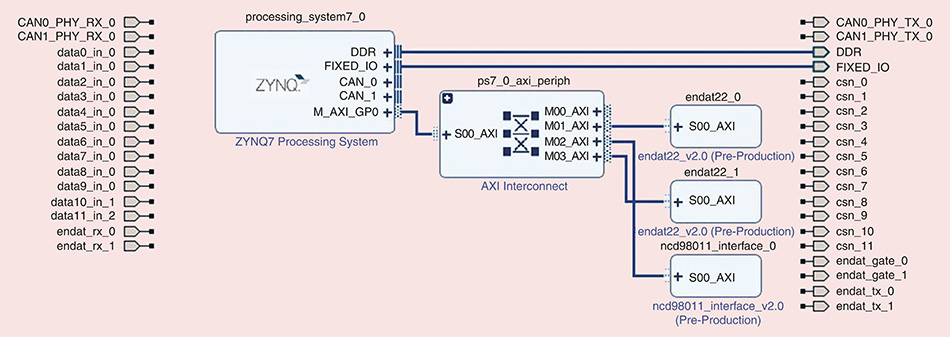

ZYNQ平台的SGMII网口实现通常需要通过其集成的PL(Programmable Logic)端来完成,PL端提供了直接与外部PHY芯片连接的接口。利用ZYNQ内置的高速串行收发器,可以很容易地在用户设计的逻辑中实现符合SGMII标准的物理层通信功能。

2.2.2 硬件设计要点

在实现ZYNQ的SGMII网口时,需要考虑硬件设计的多个关键要点:

- 首先,需要确保物理层(PHY)和ZYNQ的PL端之间的布线符合SGMII协议对信号完整性的要求;

- 其次,ZYNQ平台的参考时钟配置必须正确,以便与外部PHY芯片同步;

- 再次,电源和地线的布局对于避免干扰和信号失真至关重要;

- 最后,还应考虑温度对硬件性能的影响,确保在工作温度范围内能稳定运行。

为了在硬件设计中实现这些要点,设计者通常会使用高性能的模拟/数字转换器(ADC/DAC)、高速差分信号驱动器和接收器,以及精确的时钟管理单元。通过综合布线设计和信号完整性仿真,可以在物理层面上确保SGMII网口的稳定工作。

SGMII网口的硬件设计是一个复杂的过程,涉及到许多信号处理和布局布线的技巧。接下来的章节将详细介绍SGMII网口的维护策略,包括故障诊断、维护工具和方法,以及升级流程。

3. SGMII网口的维护策略

3.1 故障诊断与分析

3.1.1 常见问题及其诊断

在进行SGMII网口的维护时,对常见故障的识别和诊断是至关重要的一步。常见的故障类型包括但不限于物理层故障、配置错误以及数据链路层的故障。

在物理层故障中,可能是由于网线损坏、端口故障或连接不稳导致的网络传输问题。诊断此类故障的常用方法包括检查电缆连接是否正确和牢固,以及使用网络诊断工具(如ping命令、端口扫描工具等