【ZYNQ系统集成全攻略】:将SGMII网口完美融入ZYNQ PL端

发布时间: 2025-01-02 20:33:01 阅读量: 6 订阅数: 10

# 摘要

本文综合分析了ZYNQ系统与SGMII网口的设计、集成及其在高性能系统中的应用。首先介绍了ZYNQ SoC架构,重点在于可编程逻辑(PL)与处理器系统(PS)的交互以及SGMII协议的技术特点。接着详细探讨了SGMII网口在ZYNQ PL端的设计与实现,包括硬件设计、信号完整性分析与软件开发。之后,分析了RTOS和高级网络协议栈在ZYNQ系统上的集成、优化和安全机制实现。通过案例分析,本文展示了ZYNQ系统集成的实际应用,并对其性能进行了评估和测试。最后,展望了ZYNQ系统集成的未来趋势,包括行业发展的新方向和技术创新的应用案例。

# 关键字

ZYNQ系统;SGMII网口;SoC架构;硬件设计;RTOS集成;网络性能优化

参考资源链接:[ZYNQ PL端SGMII网口扩展与PS控制调试详解](https://wenku.csdn.net/doc/6xisjeyhzk?spm=1055.2635.3001.10343)

# 1. ZYNQ系统与SGMII网口概述

## 1.1 ZYNQ与网络技术的发展

ZYNQ是一种结合了ARM处理器核心和可编程逻辑(PL)的SoC架构。它允许开发者在同一个芯片上实现高性能的处理器控制和灵活的硬件加速,成为现代网络技术集成的理想选择。SGMII(Serial Gigabit Media Independent Interface)作为一种高速串行通信协议,提供了与传统以太网芯片的兼容性,为ZYNQ系统提供了强有力的网络接口支持。

## 1.2 SGMII网口的基本概念

SGMII协议是用于在芯片间或芯片与物理层(PHY)之间传输以太网数据包的接口技术。它以1.25 GHz的速度运行,支持10/100/1000 Mbps的数据速率,并广泛应用于通信设备中。SGMII网口为ZYNQ系统提供了高速和低功耗的网络连接能力,适合用于构建需要高数据吞吐量的嵌入式网络应用。

## 1.3 ZYNQ系统与SGMII的集成优势

将SGMII网口集成到ZYNQ系统中,可以带来多方面的优势。首先,ZYNQ的双处理器系统架构(PS和PL)使得硬件和软件的协同工作变得更加高效。其次,SGMII网口的集成,不仅保留了与现有以太网芯片的兼容性,还大幅度提高了系统的数据传输速率。这一组合为实现高性能的网络设备,例如工业自动化、物联网(IoT)设备和网络通信处理器等,提供了强大的支持。

通过下一章,我们将深入探讨ZYNQ SoC架构的细节,以及如何在该平台上高效利用SGMII网口技术。

# 2. 深入理解ZYNQ SoC架构

## 2.1 ZYNQ的可编程逻辑(PL)与处理器系统(PS)

### 2.1.1 PL和PS的基本概念

ZYNQ SoC是一种独特的片上系统,它将双核心ARM处理器(PS,Processor System)与可编程逻辑(PL,Programmable Logic)紧密集成。这种集成提供了一个强大的硬件平台,适用于广泛的嵌入式计算需求。PL由FPGA(Field Programmable Gate Array)构成,提供了硬件级的自定义能力,允许设计者实现特定的硬件加速功能、接口和定制数据处理流程。PS部分包含一个双核ARM Cortex-A9处理器、内存控制器、外设接口和其他系统级功能。

PS作为ZYNQ SoC中的处理核心,负责执行操作系统、运行应用程序和控制PL。而PL则提供了灵活的硬件资源,可以定制化实现各种高速并行处理逻辑。两者通过高级互连结构(AXI接口等)紧密相连,不仅实现了高速数据交换,也使得硬件和软件的协同工作成为可能。

### 2.1.2 PL与PS的交互机制

ZYNQ的PL与PS交互机制是通过AXI总线接口实现的,提供了高性能的通信方式。例如,AXI4-Stream接口用于高效的数据流传输,而AXI4-Lite接口用于处理器对FPGA内部寄存器的访问。PS可以将一些计算密集型的任务卸载到PL,利用FPGA的并行处理优势来提升系统性能。

此外,ZYNQ还提供了PS与PL之间的中断通信机制。这意味着当PL中的某些硬件操作完成或出现特定事件时,可以通过中断信号通知PS,并由PS中的软件处理这些中断事件。这种中断机制的实施对于实时响应和多任务处理环境至关重要。

## 2.2 ZYNQ上的网络接口技术

### 2.2.1 常见的网络接口技术概览

在ZYNQ SoC中,实现网络通信通常需要借助于网络接口技术。常见的网络接口技术包括但不限于MII(Media Independent Interface)、RGMII(Reduced Gigabit Media Independent Interface)、GMII(Gigabit Media Independent Interface)以及SGMII(Serial Gigabit Media Independent Interface)。这些接口在物理层面上处理信号,并通过特定协议与网络进行数据交换。

MII接口是一种早期的并行接口,其带宽为10/100Mbps;RGMII通过减少信号线数量,提升了传输效率至10/100/1000Mbps;GMII则直接支持1000Mbps的速率,但需要较多的I/O引脚;SGMII进一步提高了传输效率至1Gbps,同时减少了对I/O引脚的需求。这些技术各有优势,在不同的应用场景下被选用。

### 2.2.2 SGMII协议的技术特点

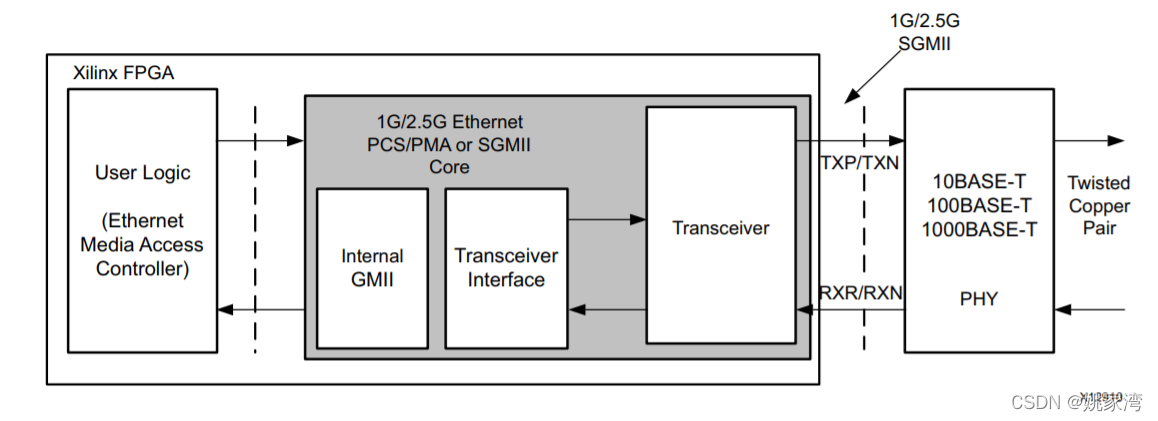

SGMII(Serial Gigabit Media Independent Interface)是Gigabit Ethernet的一种实现方式,它以串行形式传输数据,大大减少了硬件需求。与GMII相比,SGMII在保持同样数据传输速率的同时,仅需要更少的物理引脚,减少了成本和空间占用,非常适合在FPGA上实现。

SGMII使用差分信号进行数据传输,并通过特定的编码和解码机制确保数据的完整性和可靠性。它支持自动协商,可以与网络设备自动协商速度和双工模式。此外,SGMII支持简化的物理层配置,使得硬件设计和调试更加便捷。

## 2.3 ZYNQ与SGMII集成的理论基础

### 2.3.1 硬件描述语言(HDL)的角色

在ZYNQ SoC上实现SGMII网口,硬件描述语言(HDL)发挥了核心作用。硬件描述语言(HDL)如VHDL和Verilog,是用来设计、描述和模拟电子系统硬件功能的编程语言。它们允许工程师以文本形式描述硬件电路的行为和结构,进而生成可以被综合到FPGA中的门级网表。

使用HDL设计SGMII接口通常涉及对信号速率、同步机制、协议层处理等的精确控制。设计者需利用HDL编写描述SGMII协议的数据发送和接收逻辑,编码/解码过程,以及时钟域交叉处理。这些复杂的逻辑通过HDL编写、仿真和调试后,再综合成FPGA上可用的硬件逻辑。

### 2.3.2 网络接口的IP核集成

为了简化开发流程,网络接口的IP核(Intellectual Property Core)在ZYNQ SoC上集成了许多常用的网络功能。IP核是一种预先设计好的硬件功能模块,可以被集成到更大的FPGA设计中。在实现SGMII接口时,可以选用现成的以太网IP核,它提供了协议栈中的一部分或者全部功能。

集成IP核使得设计者不必从零开始设计整个SGMII接口,而是能够站在巨人的肩膀上,将精力集中在系统级的集成和优化上。使用这些IP核时,设计者仍需理解其内部结构和接口定义,以确保与ZYNQ SoC的其他部分良好集成。这包括对IP核参数的配置,以及对生成的HDL代码进行适当的修改和扩展。

在本章节中,我们深入了解了ZYNQ SoC架构的核心组成部分,包括可编程逻辑(PL)与处理器系统(PS)的概念和交互机制,以及如何将网络接口技术集成到ZYNQ SoC中。特别是,我们聚焦于SGMII协议的技术特点和集成细节,包括硬件描述语言在设计中的作用,以及网络接口IP核的使用。

以上章节内容详细分析了ZYNQ SoC的架构,以及如何利用这些特性来构建高效的网络通信接口。在接下来的章节中,我们将深入探讨如何在ZYNQ PL端设计与实现SGMII网口,包括硬件和软件设计的实践操作。这将涉及更多细节,例如硬件接口的配置和调试,以及驱动程序的编写和用户空间程序的接口开发。

# 3. SGMII网口在ZYNQ PL端的设计与实现

## 3.1 设计思路与方法论

在ZYNQ PL端实现SGMII网口设计,首先要明确设计目标与约束。对于设计目标,我们需要确保SGMII网口能够提供高速、稳定的网络连接,并且能够满足实时数据传输的需求。同时,为了满足不同应用场景的需求,设计还应具有一定的灵活性和扩展性。

### 3.1.1 确定设计目标与约束

设计约束通常包括以下几点:

- 硬件资源:需要考虑ZYNQ的FPGA资源是否足够实现所需功能。

- 功耗限制:设计时应尽量优化功耗,尤其是在移动或嵌入式环境中。

- 接口标准:SGMII协议有明确的电气特性和信号规范,设计需遵循标准。

- 软

0

0