【ZYNQ稳定设计】:创建可靠PL端SGMII网口设计方案的关键步骤

摘要

本文对ZYNQ平台及SGMII接口进行了全面的概述与分析。首先介绍了ZYNQ平台的基础知识以及SGMII协议的技术细节,然后深入探讨了硬件设计的理论基础,包括ZYNQ的PL端接口、SGMII信号定义、电气特性、高速信号完整性原理和差分信号设计要点。接着,文章详细阐述了SGMII接口在硬件设计中的实践步骤,包含PCB布局、信号布线、阻抗控制等关键环节。此外,本文还探讨了软件与固件开发的相关内容,如Linux内核网络接口驱动开发和硬件抽象层设计。最后,针对性能测试、故障诊断与解决进行了系统的测试与优化讨论,为高性能网络接口设计提供了理论依据和实践经验。

关键字

ZYNQ平台;SGMII接口;硬件设计;信号完整性;固件编程;性能测试;故障诊断。

参考资源链接:ZYNQ PL端SGMII网口扩展与PS控制调试详解

1. ZYNQ平台及SGMII接口概述

1.1 ZYNQ平台简介

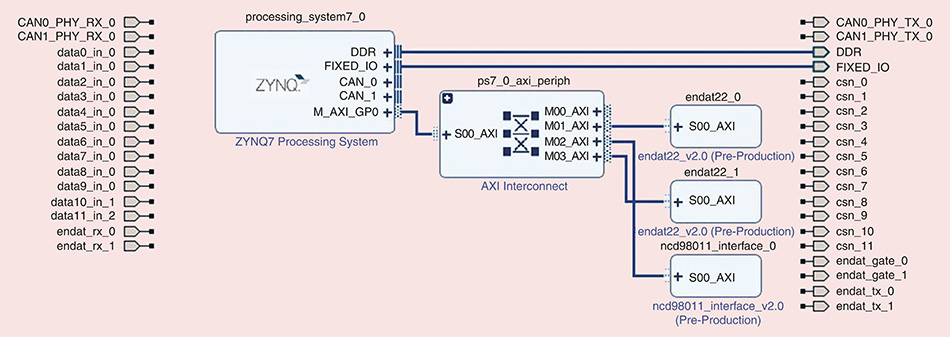

ZYNQ平台是由Xilinx推出的一款集成了ARM处理器与FPGA的片上系统(SoC)。这种独特的架构设计使其在需要高性能和灵活性的应用中具有明显优势。ZYNQ平台中的处理器子系统(PS)部分包括一个或多个ARM处理器核心,而可编程逻辑(PL)部分则提供了丰富的FPGA资源,用户可以根据自己的需求进行逻辑设计和实现。

1.2 SGMII接口的角色

SGMII(Serial Gigabit Media Independent Interface)是一种高速串行接口标准,广泛用于实现以太网的物理层接口。该接口可以支持高达1 Gbps的双工通信,适用于千兆位以太网的芯片间通信。在ZYNQ平台上,SGMII接口通常被用于与外部网络物理层(PHY)设备或者千兆以太网MAC核通信。

1.3 SGMII接口的重要性

在高速数据通信领域,信号完整性和电气特性是两个非常关键的因素。SGMII接口以其高速率、低功耗以及与旧有IEEE 802.3标准的良好兼容性,在FPGA和网络设备的通信中占据重要地位。理解SGMII接口的工作机制,对于设计高性能的网络通信系统至关重要。本章节将从ZYNQ平台和SGMII接口的基础出发,为后续深入探讨硬件设计和固件开发奠定理论基础。

2. 硬件设计理论基础

2.1 ZYNQ的PL端接口概述

2.1.1 ZYNQ架构简介

ZYNQ是一类将ARM处理器与FPGA逻辑相结合的SoC(System on Chip)设备,由Xilinx公司开发。ZYNQ设备的最大特点是其内置了双核ARM Cortex-A9处理器,并且为用户提供了可编程逻辑器件的灵活性。这种结构允许硬件设计人员在设计时既能够利用强大的处理器核心进行高性能计算,又能够利用FPGA逻辑来实现自定义的硬件加速和接口。

ZYNQ架构中的PL(Programmable Logic)端通常指的是FPGA部分。这部分可编程逻辑具有高灵活性,可以实现复杂的信号处理、数据转换和控制算法。在ZYNQ平台中,PS(Processing System)端和PL端通过AMBA(Advanced Microcontroller Bus Architecture)总线相互连接,这为整个系统提供了高速的通讯能力。

2.1.2 PL端接口标准和SGMII协议

在PL端,ZYNQ提供了包括SGMII(Serial Gigabit Media Independent Interface)在内的多种接口标准。SGMII是一种用于以太网通信的串行接口协议,广泛用于实现高速网络连接。利用SGMII协议的接口,可以在FPGA中实现10/100/1000 Mbps的以太网收发器。

SGMII接口设计的关键在于它的差分信号传输能力,可以大幅减少信号损失和干扰。SGMII协议还规定了包括时钟恢复、信号同步、以及传输错误检测等机制,确保了数据传输的可靠性。

2.2 SGMII接口信号和电气特性

2.2.1 SGMII信号定义

SGMII接口的信号主要包括以下几个部分:

- TXP/TXN:差分对输出信号,用于发送数据。

- RXP/RXN:差分对输入信号,用于接收数据。

- REFCLKP/REFCLKN:差分对时钟参考信号,通常由专用的时钟源提供。

- TX_EN:发送使能信号,用于控制数据的发送。

信号的差分传输方式不仅可以减少电磁干扰,还能提高信号传输的抗干扰性和信号的完整性。

2.2.2 电气特性及要求

SGMII接口的电气特性要求严格,以确保高速信号的完整性和可靠性。例如,SGMII标准规定了传输线的特征阻抗必须是100欧姆。为了满足这一要求,设计时需使用具有均匀阻抗的传输线,并确保在印刷电路板(PCB)布局中对信号线进行合理的隔离。

SGMII信号的输出电平和输入门限也都有明确的规格。为了使SGMII接口能够正确地接收和发送数据,需要确保信号电平符合电气标准,例如信号的最大和最小电压范围。

2.3 硬件设计的理论基础

2.3.1 高速信号完整性原理

高速信号完整性是硬件设计领域的一个关键概念。它关注的是信号在传输路径上的行为,包括信号的上升沿和下降沿,以及信号反射、串扰、电磁干扰等现象。由于SGMII接口数据传输速率高达1Gbps,因此信号完整性问题会更突出。

为了保证高速信号的完整性,需要通过合理的PCB布局和布线设计来控制阻抗、减少反射和串扰。设计时还需考虑到信号的传输延迟、信号时序等要素。

2.3.2 差分信号设计要点

差分信号设计是提高信号完整性的关键之一。差分信号由一对线路组成,两线路中的信号电压振幅相等但相位相反。差分信号设计要点包括:

- 确保差分对的阻抗匹配,避免阻抗失配引起的反射。

- 确保差分对线路保持紧密的耦合,并在PCB上保持等长,以保持相位一致。

- 差分对周围应避免布置高速信号或高速时钟信号,防止串扰。

差分信号设计的好坏直接关系到信号质量,因此在高速通信系统设计中是不可忽视的部分。通过PCB设计仿真工具和实际测试,可以有效验证差分信号的设计效果。

3. 硬件设计实践步骤

3.1 SGMII接口的硬件布局

3.1.1 PCB布局原则和技巧

PCB布局是硬件设计中的重要环节,尤其在实现高速SGMII接口时,布局的质量直接影响到信号的完整性和系统的性能。以下是一些在设计SGMII接口时需要遵循的PCB布局原则和技巧:

- 元件排列:将SGMII相关的高速接口器件靠近ZYNQ处理器布局,以缩短迹线长度和减少信号路径上的干扰。

- 走线优化:使用直角或45度角走线,避免锐角或锐角走线以减少信号反射。

- 差分对走线:差分信号对应的走线应等长等间距,并保持平行以维持阻抗一致性。

- 去耦合:在电源和地之间放置去耦电容,靠近电源引脚,减小电源噪声。

3.1.2 信号回流路径和去耦合设计

信号回流路径是指信号在传输路径上的返回路线。在设计SGMII接口时,需要特别注