没有合适的资源?快使用搜索试试~ 我知道了~

首页汽车雷达与频谱挑战:《模拟对话》第52卷第3期深度解析

《模拟对话》第52卷第三期是一份由ADI公司发行的专注于科技领域的免费月刊,自1967年起便以其作为业界交流平台的角色而知名。本期杂志探讨了多个关键的IT和电子工程话题: 1. 汽车雷达传感器与无线电频谱拥堵:文章关注了在城市环境中,随着ADAS(先进驾驶辅助系统)的普及,多个雷达应用如何共存,以及它们是否会导致无线电频谱的资源争夺,甚至可能影响彼此的性能。这是一个关于电子战场的议题,提示了现代汽车电子系统面临的复杂挑战。 2. 为信息娱乐设备供电的汽车启停系统:现代汽车的启停系统旨在节能,但电池在低温下可能无法提供足够的电力支持信息娱乐设备。文章讨论了这个问题及其对电池寿命的影响,强调了电源管理的重要性。 3. 锁相环(PLL)基础原理:PLL是高频电子设计的关键组件,文章深入解析了PLL的工作原理,涵盖其在不同应用场景中的作用,如时钟净化、无线通信链路和高速信号合成。 4. 非常见问题解答:针对工程师的实用问题,本期提供了关于仪表放大器增益范围的讨论,探讨了是否可以通过复用器实现可编程增益,挑战了常规设计思维。 5. 接收器技术进展:回顾了接收器技术的百年历史,从早期的无线电技术到超外差接收器,再到SDR(软件定义收发器),展示了技术演进的重要里程碑。 6. 200mA精密基准电压源的用途:Refulator是一款集成式高精度电压和电流源,特别适合那些对稳定性、精确度有高要求的应用,如精密测量和测试设备。 这些内容不仅提供了技术深度,也鼓励读者了解最新的行业动态,激发创新设计灵感。通过阅读《模拟对话》第52卷第三期,工程师们可以深入理解并解决实际设计中的问题,提升技术水平。

资源详情

资源推荐

《模拟对话》第52卷第3期

12

0

100

0.0001 0.001 0.01 0.1 1 10

Efficiency (%)

Power Loss (mW)

Load Current (A)

10

20

30

40

50

60

70

80

0.1

10k

1

10

100

1k

90

f = 2.1 MHz

Burst Mode Operation

Burst Loss

V

IN

= 12 V

V

OUT1

= 5 V

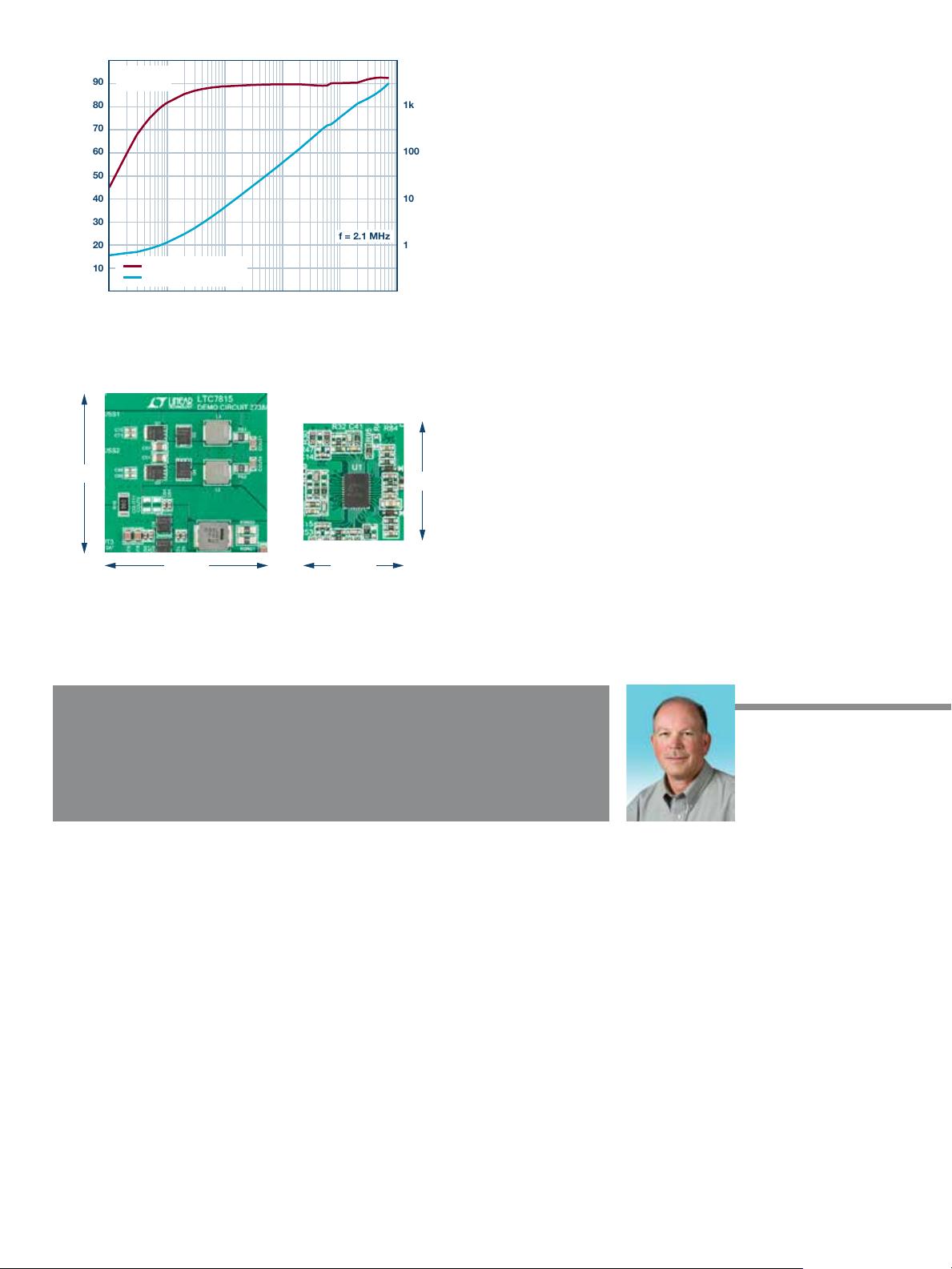

图3. LTC7815在不同转换器部分的效率与负载电流。

图4为LTC7815演示板(原理图如图1所示),最宽部分为48 mm。

46 mm

48 mm

18 mm

17 mm

图4. LTC7815演示板顶层和底层的尺寸与布局。

保护特性

LTC7815可配置为通过使用DCR(电感器阻抗)或检流电阻来检测输

出电流。两种电流检测方案之间的选择主要权衡成本、功耗和

精度。DCR检测日益流行,因为它省去了昂贵的电流感测电阻,

功率效率更高,特别是在大电流应用中。而检流电阻是更精确的

电流检测方法。

片上比较器监测降压输出电压,当输出大于标称值10%时,发

出过压条件信号。检测到这种情况时,顶部MOSFET关断,底

部MOSFET导通,直至过压条件清除。只要过压条件持续,底部

MOSFET就持续导通。如果输出电压恢复至安全水平,则自动恢

复正常操作。

在温度较高或内部功耗引起片内过度自热的情况下,过温关断

电路将关断LTC7815。当结温超过大约170°C时,过温电路将禁用

片上偏置LDO,从而使偏置电源降至0 V,并顺序有效地关断整个

LTC7815。一旦结温降回大约155°C,LDO重新导通。

结论

汽车起停系统可节省燃料,并在未来几年继续演进。为板载信

息娱乐系统和导航系统供电必须很小心,这些系统需要的电压

高达5 V,甚至超过5 V。当引擎重新起动时,若汽车电池电压降

至5 V以下,这些系统可能复位。LTC7815通过将电池电压提升至

安全操作水平来解决此问题。这一特性结合两个降压控制器,

非常适合在配置起停系统的汽车中为诸多汽车电子设备供电。

Bruce Haug [bruce.haug@analog.com]于1980年毕业于圣何塞州立大学,获电

气工程学士学位。2006年4月,加盟凌力尔特(现为ADI公司的一部分),担任产

品营销工程师。此前,Bruce曾在Cherokee International、Digital Power和福

特宇航供职。他还热衷于参与体育活动。

Bruce Haug

《模拟对话》第52卷第3期

13

锁相环(PLL)基本原理

作者:Ian Collins

F

REF

N × F

REF

VCO

Low-Pass

Filter

÷ N

Counter

Phase

Detector

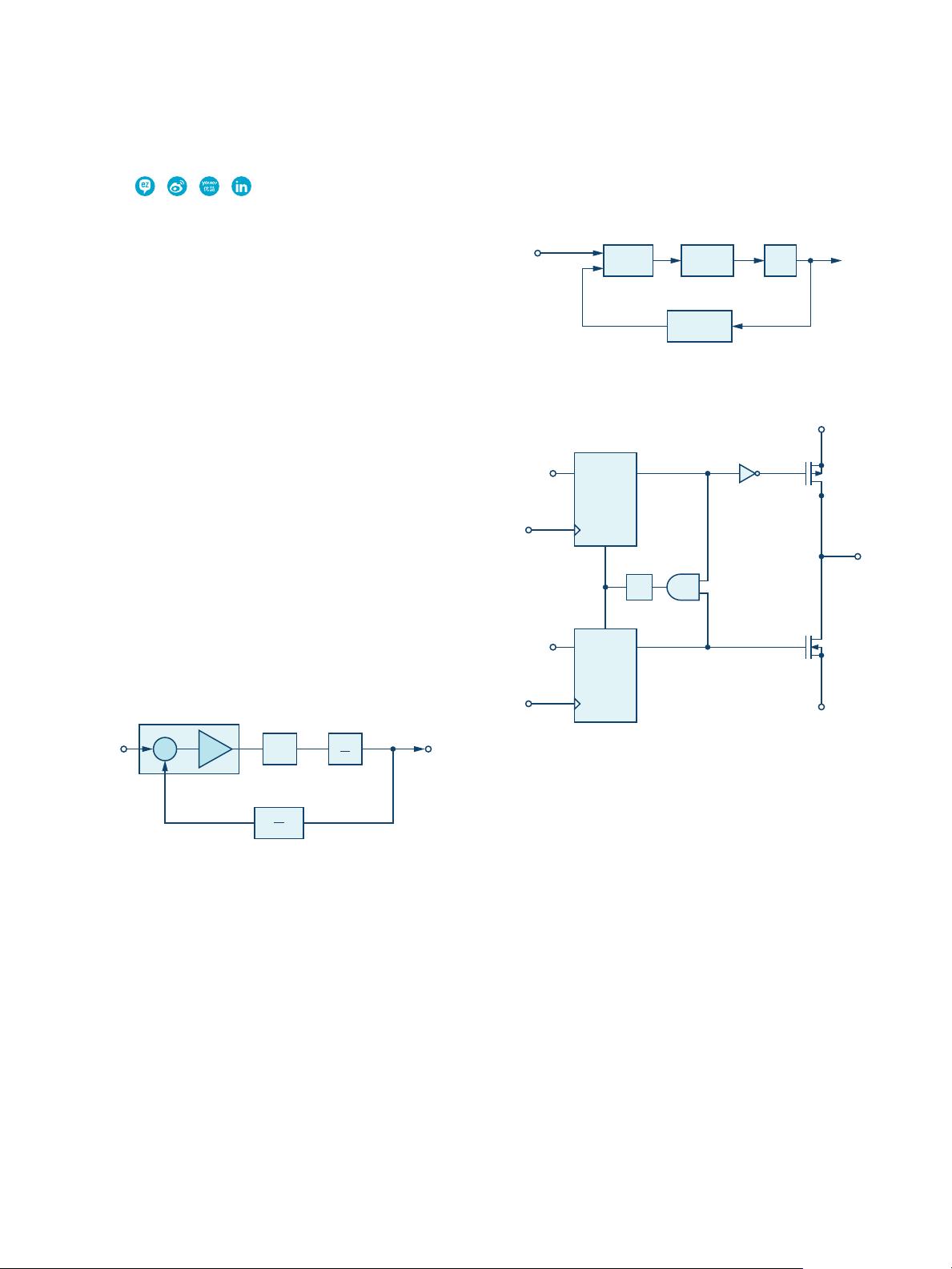

图2. PLL基本配置

鉴频鉴相器

–IN

+IN

HI

HI

Up

U4

V+

P1

N1

OUT

V– (0 V)

Down

Delay

U3

D2 Q2

D1 Q1

U2

U1

CLR2

CLR1

图3. 鉴频鉴相器

图3中的鉴频鉴相器将+IN端的F

REF

输入与和–IN端的反馈信号进行

比较。它使用两个D型触发器和一个延迟元件。一路Q输出使能正

电流源,另一路Q输出使能负电流源。这些电流源就是所谓电荷

泵。有关PFD操作的更多详细信息,请参阅“用于高频接收器和

发射器的锁相环”。

使用这种架构,下面+IN端的输入频率高于–IN端(图4),电荷

泵输出会推高电流,其在PLL低通滤波器中积分后,会使VCO

调谐电压上升。这样,–IN频率将随着VCO频率的提高而提

高,两个PFD输入最终会收敛或锁定到相同频率(图5)。如果–

IN频率高于+IN频率,则发生相反的情况。

摘要:

锁相环(PLL)电路存在于各种高频应用中,从简单的时钟净化电路

到用于高性能无线电通信链路的本振(LO),以及矢量网络分析仪

(VNA)中的超快开关频率合成器。本文将参考上述各种应用来介绍

PLL电路的一些构建模块,以指导器件选择和每种不同应用内部

的权衡考虑,这对新手和PLL专家均有帮助。本文参考ADI公司的

ADF4xxx和HMCxxx系列PLL和压控振荡器(VCO),并使用ADIsimPLL(ADI

公司内部PLL电路仿真器)来演示不同电路性能参数。

基本配置:时钟净化电路

锁相环的最基本配置是将参考信号(F

REF

)的相位与可调反馈信号

(RF

IN

) F

0

的相位进行比较,如图1所示。图2中有一个在频域中工

作的负反馈控制环路。当比较结果处于稳态,即输出频率和相

位与误差检测器的输入频率和相位匹配时,我们说PLL被锁定。

就本文而言,我们仅考虑ADI公司ADF4xxx系列PLL所实现的经典数

字PLL架构。

该电路的第一个基本元件是鉴频鉴相器(PFD)。PFD将输入到REF

IN

的频率和相位与反馈到RF

IN

的频率和相位进行比较。ADF4002是一

款可配置为独立PFD(反馈分频器N = 1)的PLL。因此,它可以与高

质量压控晶体振荡器(VCXO)和窄低通滤波器一起使用,以净化高

噪声REF

IN

时钟。

Feedback Divider

Loop Filter

Error Detector

VCO

1

N

Z(s)

e(s)+

–

K

V

s

K

d

F

REF

(θ

REF

)

F

O

(θ

O

)

CP

PD

图1. PLL基本配置

分享至

《模拟对话》第52卷第3期

14

+IN

–IN

OUT

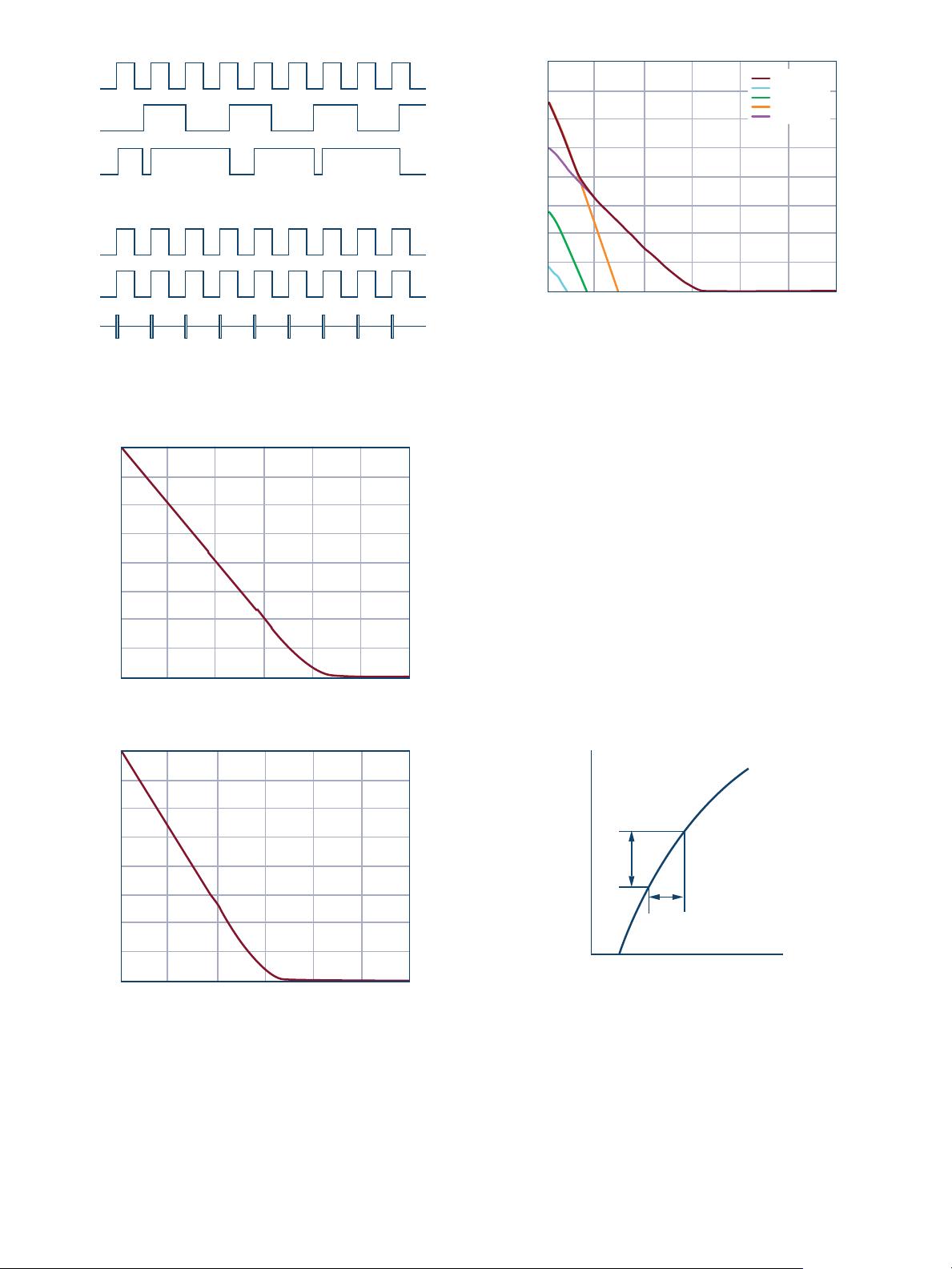

图4. PFD错相和频率失锁

+IN

–IN

OUT

图5. 鉴频鉴相器、频率和锁相

回到原先需要净化的高噪声时钟例子,时钟、自由运行VCXO和闭

环PLL的相位噪声曲线可以在ADIsimPLL中建模。

SSB Phase Noise (dBc

/Hz)

100 1k

Offset Frequency (Hz)

–80

–90

–100

–110

–120

–130

–140

–150

–160

100M

10k 100k 1M 10M

图6. 参考噪声

–80

–90

–100

–110

–120

–130

–140

–150

–160

SSB Phase Noise (dBc

/Hz)

100 1k

Offset Frequency (Hz)

100M10k 100k 1M 10M

图7. 自由运行VCXO

–80

–90

–100

–110

–120

–130

–140

–150

–160

Phase Noise (dBc/Hz)

100 1k

Frequency (Hz)

100M10k 100k 1M 10M

Total

Loop Filter

Chip

Ref

VCO

图8. 总PLL噪声

从所示的ADIsimPLL曲线中可以看出,REF

IN

的高相位噪声(图6)由低

通滤波器滤除。由PLL的参考和PFD电路贡献的所有带内噪声都

被低通滤波器滤除,只在环路带宽外(图8)留下低得多的VCXO噪

声(图7)。当输出频率等于输入频率时,PLL配置最简单。这种PLL

称为时钟净化PLL。对于此类时钟净化应用,建议使用窄带宽(<1

kHz)低通滤波器。

高频整数N分频架构

为了产生一系列更高频率,应使用VCO,其调谐范围比VCXO更宽。

这常用于跳频或扩频跳频(FHSS)应用中。在这种PLL中,输出是参

考频率的很多倍。压控振荡器含有可变调谐元件,例如变容二极

管,其电容随输入电压而改变,形成一个可调谐振电路,从而

可以产生一系列频率(图9)。PLL可以被认为是该VCO的控制系统。

反馈分频器用于将VCO频率分频为PFD频率,从而允许PLL生成

PFD频率倍数的输出频率。分频器也可以用在参考路径中,这

样就可以使用比PFD频率更高的参考频率。ADI公司的ADF4108就

是这样的PLL。PLL计数器是电路中要考虑的第二个基本元件。

VCO Tuning Voltage (V)

K

V

= ΔF/ΔV

ΔF

ΔV

VCO Output Frequency (MHz)

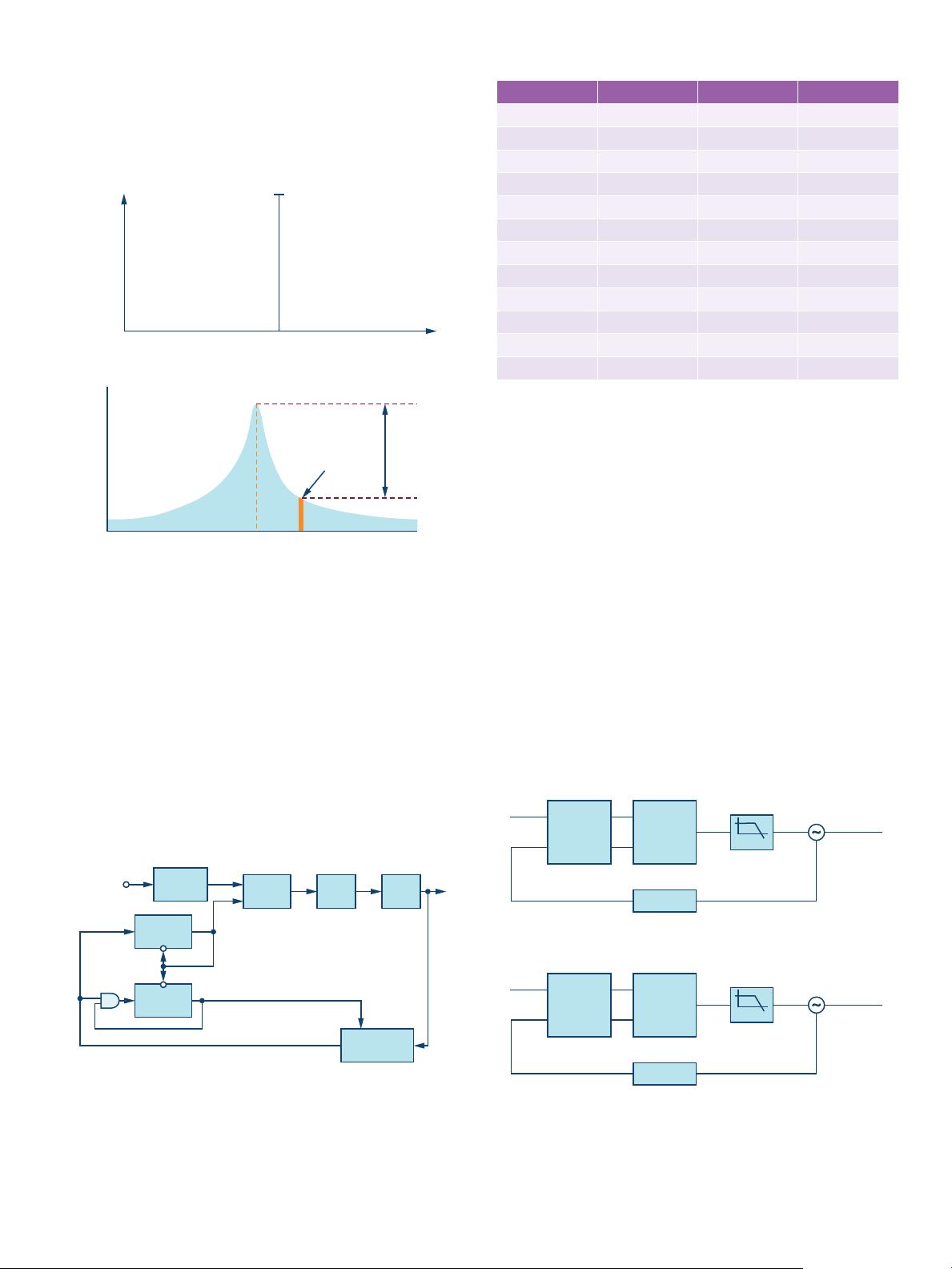

图9. 压控振荡器

《模拟对话》第52卷第3期

15

PLL的关键性能参数是相位噪声、频率合成过程中的多余副产物或

杂散频率(简称杂散)。对 于 整 数 N PLL分 频 ,杂 散 频 率 由 PFD频率产

生。来自电荷泵的漏电流会调制VCO的 调 谐 端 口 。低 通 滤 波 器 可 减

轻这种影响,而且带宽越窄,对杂散频率的滤波越强。理想单音信

号没有噪声或额外杂散频率(图10),但 在 实 际 应 用 中 ,相 位 噪 声 像

裙摆一样出现在载波边缘,如图11所 示 。单 边 带 相 位 噪 声 是 指 在

距离载波的指定频率偏移处,1 Hz带宽内相对于载波的噪声功率。

No Noise

–∞

No Unwanted Discrete Tones

(That Is, Spurs)

Fc (Carrier Frequency)

图10. 理想LO频谱

Amplitude

1 Hz

P

S

P

SSB

S

C

(f) = P

SSB

/P

S

ff

0

Frequency

图11. 单边带相位噪声

整数N和小数N分频器

在窄带应用中,通道间隔很窄(通常<5 MHz),反馈计数器N很高。

通过使用双模P/P + 1预分频器,如图12所示,可以利用一个小电

路获得高N值,并且N值可以利用公式N = PB + A来计算;以8/9预

分频器和90的N值为例,计算可得B值为11,A值为2。对于A或2

个周期,双模预分频器将进行9分频。对于剩余的(B-A)或9个周

期,它将进行8分频,如表1所示。预分频器一般利用较高频率

电路技术设计,例如双极性射极耦合逻辑(ECL)电路,而A和B计

数器可以接受这种较低频率的预分频器输出,它们可以利用低

速CMOS电路制造,以减少电路面积和功耗。像ADF4002这样的

低频净化PLL省去了预分频器。

F

OUT

F

1

F

REF

Load

Load

÷ B

Counter

Reference

Divider

÷ R

Phase

Detector

Low-

Pass

Filter

VCO

Dual Modulus

Prescaler

÷ P/P + 1

Control:

Low P,

High (P = 1)

Total Number of Counts of F

OUT

in a Full F

1

Cycle

A × (P + 1) + (B – A)P

AP + A + BP – AP

BP + A

F

OUT

= F

1

× (BP + A)

F

OUT

= (F

REF

/R) × (BP + A)

÷ A

Counter

图12. 具有双模N计数器的PLL

表1. 双模预分频器操作

N Value P/P + 1 B Value A Value

90 9 11 2

81 9 10 1

72 8 9 0

64 8 8 0

56 8 7 0

48 8 6 0

40 8 5 0

32 8 4 0

24 8 3 0

16 8 2 0

8 8 1 0

0 8 0 0

带内(PLL环路滤波器带宽内)相位噪声受N值直接影响,带内噪声

增幅为20log(N)。因此,对于N值很高的窄带应用,带内噪声主要

由高N值决定。利用小数N分频合成器(例如ADF4159或HMC704),可

以实现N值低得多但仍有精细分辨率的系统。这样一来,带内相

位噪声可以大大降低。图13至图16说明了其实现原理。在这些

示例中,使用两个PLL来生成适合于5G系统本振(LO)的7.4 GHz至

7.6 GHz频率,通道分辨率为1 MHz。ADF4108以整数N分频配置使

用(图13),HMC704以小数N分频配置使用。HMC704(图14)可以使用

50 MHz PFD频率,这会降低N值,从而降低带内噪声,同时仍然支

持1 MHz(或更小)的频率步长——可注意到性能改善15 dB(在8 kHz偏

移频率处)(图15与图16对比)。但是,ADF4108必须使用1 MHz PFD才

能实现相同的分辨率。

对于小数N分频PLL务必要小心,确保杂散不会降低系统性能。对

于HMC704之类的PLL,整数边界杂散(当N值的小数部分接近0或1

时产生,例如147.98或148.02非常接近整数值148)最需要关注。

解决措施是对VCO输出到RF输入进行缓冲,以及/或者做精心的

规划频率,改变REF

IN

以避免易发生问题的频率。

LPF

N = 7400

N = 7401

7400 MHz

7401 MHz

Charge

Pump

Loop Bandwidth ≤ F

PFD

/10

VCO

F

PFD

1 MHz

F

PFD

1 MHz

PFD

/N

图13. 整数N分频PLL

LPF

N = 148 + 0/50

N = 148 = 1/50

7400 MHz

7401 MHz

Charge

Pump

Loop Bandwidth ≤ F

PFD

/10

VCO

F

PFD

50 MHz

F

PFD

50 MHz

PFD

/N

图14. 小数N分频PLL

剩余71页未读,继续阅读

JasonFreeman

- 粉丝: 74

- 资源: 43

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- C++标准程序库:权威指南

- Java解惑:奇数判断误区与改进方法

- C++编程必读:20种设计模式详解与实战

- LM3S8962微控制器数据手册

- 51单片机C语言实战教程:从入门到精通

- Spring3.0权威指南:JavaEE6实战

- Win32多线程程序设计详解

- Lucene2.9.1开发全攻略:从环境配置到索引创建

- 内存虚拟硬盘技术:提升电脑速度的秘密武器

- Java操作数据库:保存与显示图片到数据库及页面

- ISO14001:2004环境管理体系要求详解

- ShopExV4.8二次开发详解

- 企业形象与产品推广一站式网站建设技术方案揭秘

- Shopex二次开发:触发器与控制器重定向技术详解

- FPGA开发实战指南:创新设计与进阶技巧

- ShopExV4.8二次开发入门:解决升级问题与功能扩展

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功