Spartan6 FPGA DDR2控制器设计:MIG应用指南

"Xilinx Spartan 6 FPGA的DDR2 IP核使用手册"

DDR2之MIG应用是Xilinx公司提供的一种高效、便捷的方式来在Spartan 6 FPGA中集成DDR2内存控制器。MIG(Memory Interface Generator)是Xilinx ISE Design Suite中的一个组件,专门用于创建针对不同内存类型(如DDR2)的接口IP核。这个工具允许设计师通过一个图形用户界面(GUI)定制控制器,以适应特定的内存芯片和系统需求。

在Spartan 6 FPGA中,内存控制器块(MCB)是一个硬核单元,它不仅支持DDR3,还兼容多种制造商的DDR2内存芯片,例如Micron、Elpida和Hynix。MCB的优势在于它的错误检测和校正能力,以及高精度的PLL_ADV,这些特性提升了设计的可靠性和性能。

MIG工具使得用户能够轻松地生成DDR2控制器的HDL(硬件描述语言)源代码和约束文件。在MIG的GUI中,设计师可以选择相应的内存芯片模型、总线宽度、速度等级,以及设置其他关键参数,如CAS延迟、突发长度和引脚分配。如果所选内存芯片不在MIG的预定义列表中,设计师可以在生成代码后进行自定义修改。

MIG生成的DDR2控制器简化了用户的控制接口,使用通用FIFO的读写方式,而不是复杂的DDR2读写逻辑。同时,它通过sram的地址映射方式处理行、列地址选择,降低了设计复杂度。

文档的结构通常包括以下步骤:

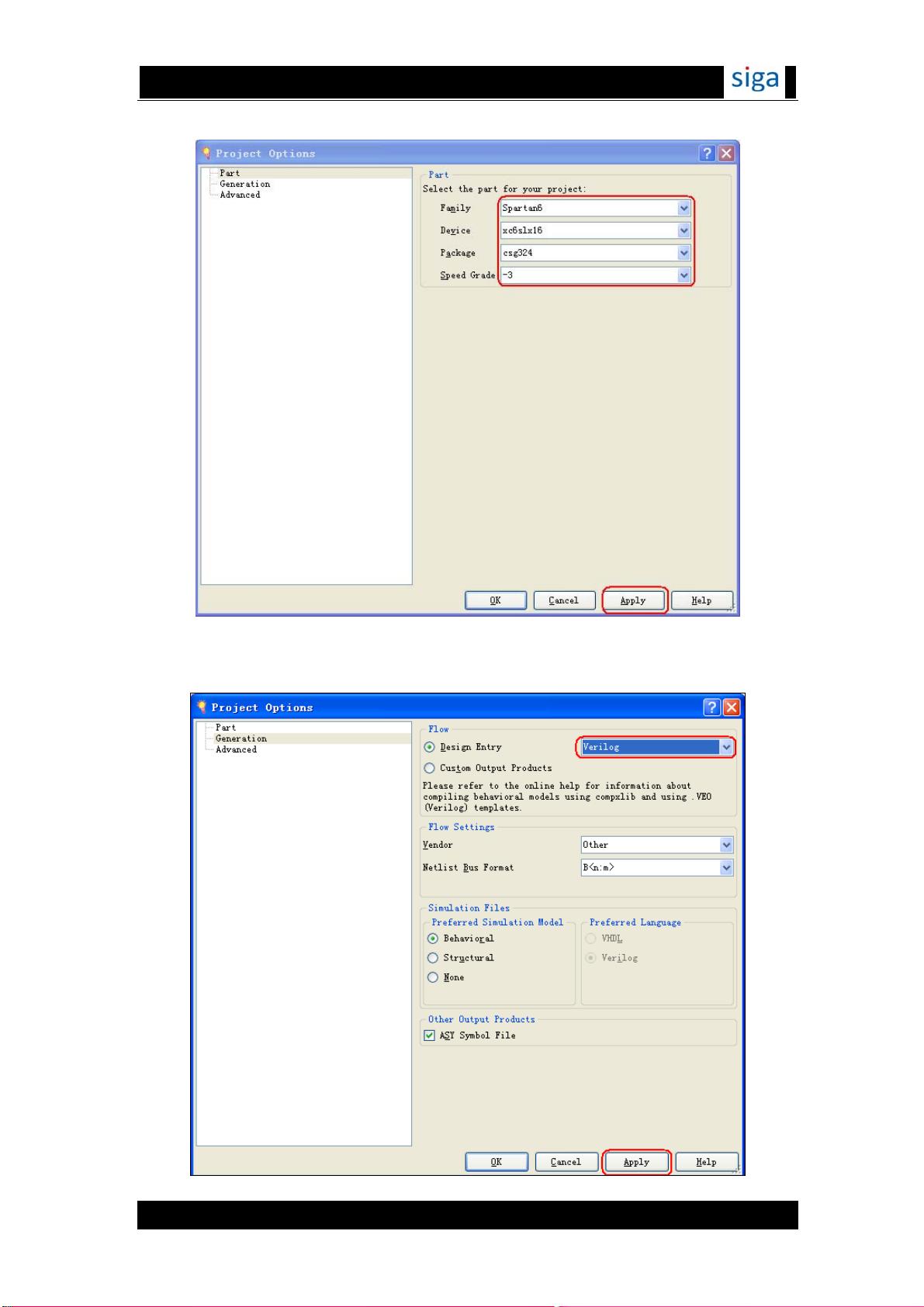

1. **MIG向导产生DDR2控制器**:在CORE Generator中启动新项目,选择DDR2控制器,输入相关参数,生成控制器的HDL和约束文件。

2. **生成ISE工程文件**:将MIG产生的文件导入ISE设计环境,创建一个新的工程。

3. **更新UCF文件**:更新用户约束文件(UCF),指定FPGA引脚与DDR2接口信号的映射。

4. **更新RTL文件**:可能需要根据实际需求对生成的HDL代码进行微调。

5. **编译生成Bit文件**:在ISE中编译整个工程,生成编程文件(Bit文件),这将是配置FPGA的文件。

6. **ChipScope调试**:利用ChipScope集成逻辑分析器工具进行DDR2读写操作的调试,确保数据传输的正确性。

通过MIG,设计师可以快速、准确地实现DDR2内存接口的设计,而无需深入理解底层的DDR2协议细节,极大地提高了设计效率和成功率。对于Siga-S16 Spartan6 FPGA开发板来说,这份手册提供了一条清晰的路径,帮助用户成功地运用MIG工具完成DDR2控制器的设计和验证。

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-10-04 上传

2021-09-29 上传

2021-09-11 上传

2022-07-15 上传

Tring_on

- 粉丝: 0

- 资源: 1

最新资源

- CoreOS部署神器:configdrive_creator脚本详解

- 探索CCR-Studio.github.io: JavaScript的前沿实践平台

- RapidMatter:Web企业架构设计即服务应用平台

- 电影数据整合:ETL过程与数据库加载实现

- R语言文本分析工作坊资源库详细介绍

- QML小程序实现风车旋转动画教程

- Magento小部件字段验证扩展功能实现

- Flutter入门项目:my_stock应用程序开发指南

- React项目引导:快速构建、测试与部署

- 利用物联网智能技术提升设备安全

- 软件工程师校招笔试题-编程面试大学完整学习计划

- Node.js跨平台JavaScript运行时环境介绍

- 使用护照js和Google Outh的身份验证器教程

- PHP基础教程:掌握PHP编程语言

- Wheel:Vim/Neovim高效缓冲区管理与导航插件

- 在英特尔NUC5i5RYK上安装并优化Kodi运行环境