VerilogHDL整合篇:从基础到高级技巧

"VerilogHDL 那些事儿 整合篇"

《VerilogHDL 那些事儿 整合篇》是一本面向初学者的教程,它着重讲解了在Verilog HDL设计中如何将建模和时序概念进行有效整合。作者通过深入探讨在实际设计中遇到的问题,比如计数器和定时器的集成,以及如何提高模块的可读性和可扩展性,帮助读者理解Verilog HDL的精髓。

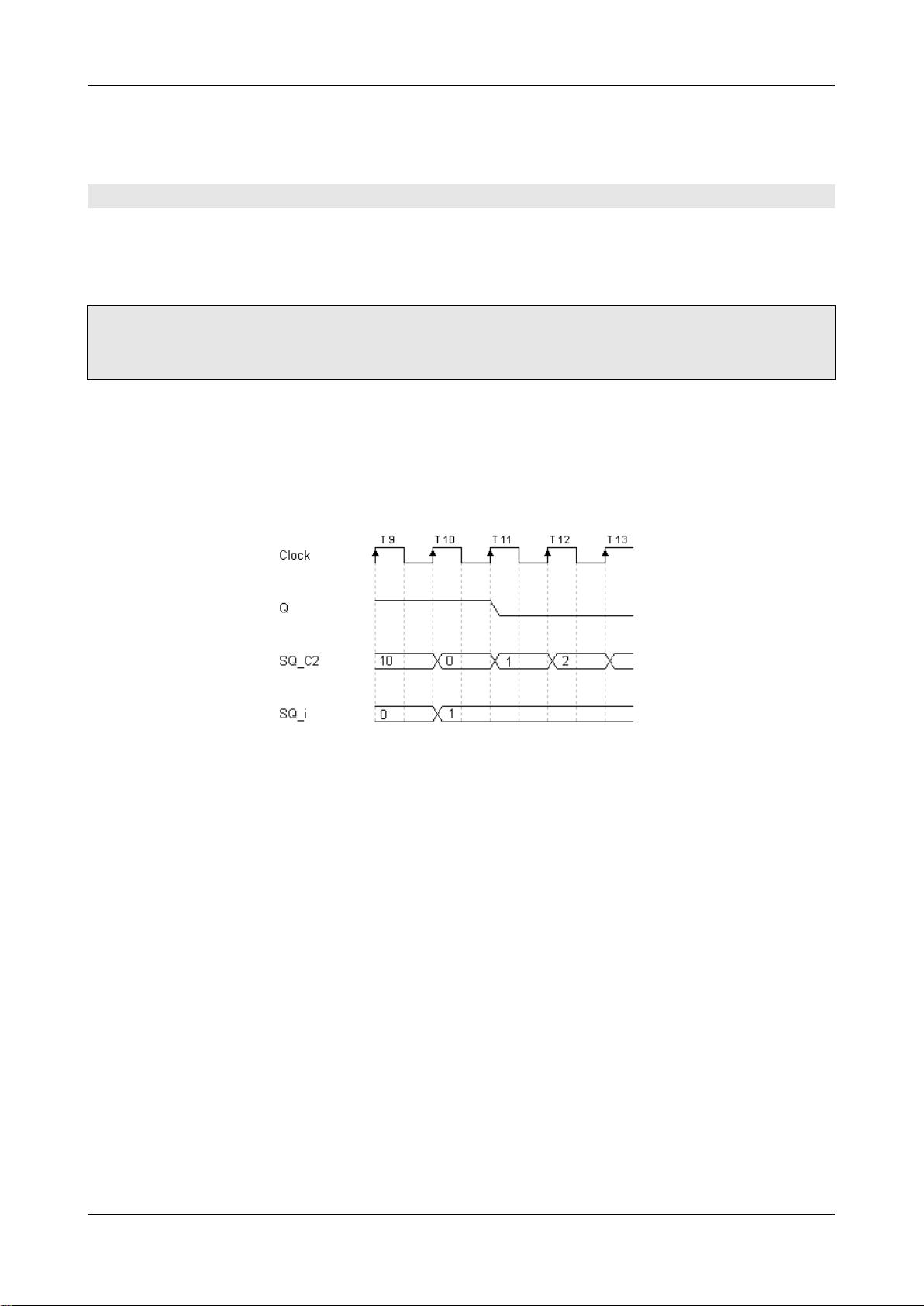

在整合篇中,作者特别关注了如何在Verilog中实现类似for、while和do-while等顺序编程语言中的循环结构。尽管Verilog HDL本身并不直接支持这些循环语句,但可以通过巧妙的逻辑设计来模拟它们。第一章介绍了如何模仿这些循环,而第五章则进一步阐述了如何利用Verilog的特性,通过指向步骤的变量和整合技巧来实现各种循环。

另一个关键议题是理想时序与物理时序的整合。理想时序反映了Verilog HDL的行为模型,而物理时序对应于实际硬件的行为。在两者之间找到平衡点是一项挑战,但也是设计高效模块的关键。通过理解和利用它们之间的"黏糊点",可以编写出同时满足行为和硬件需求的模块。

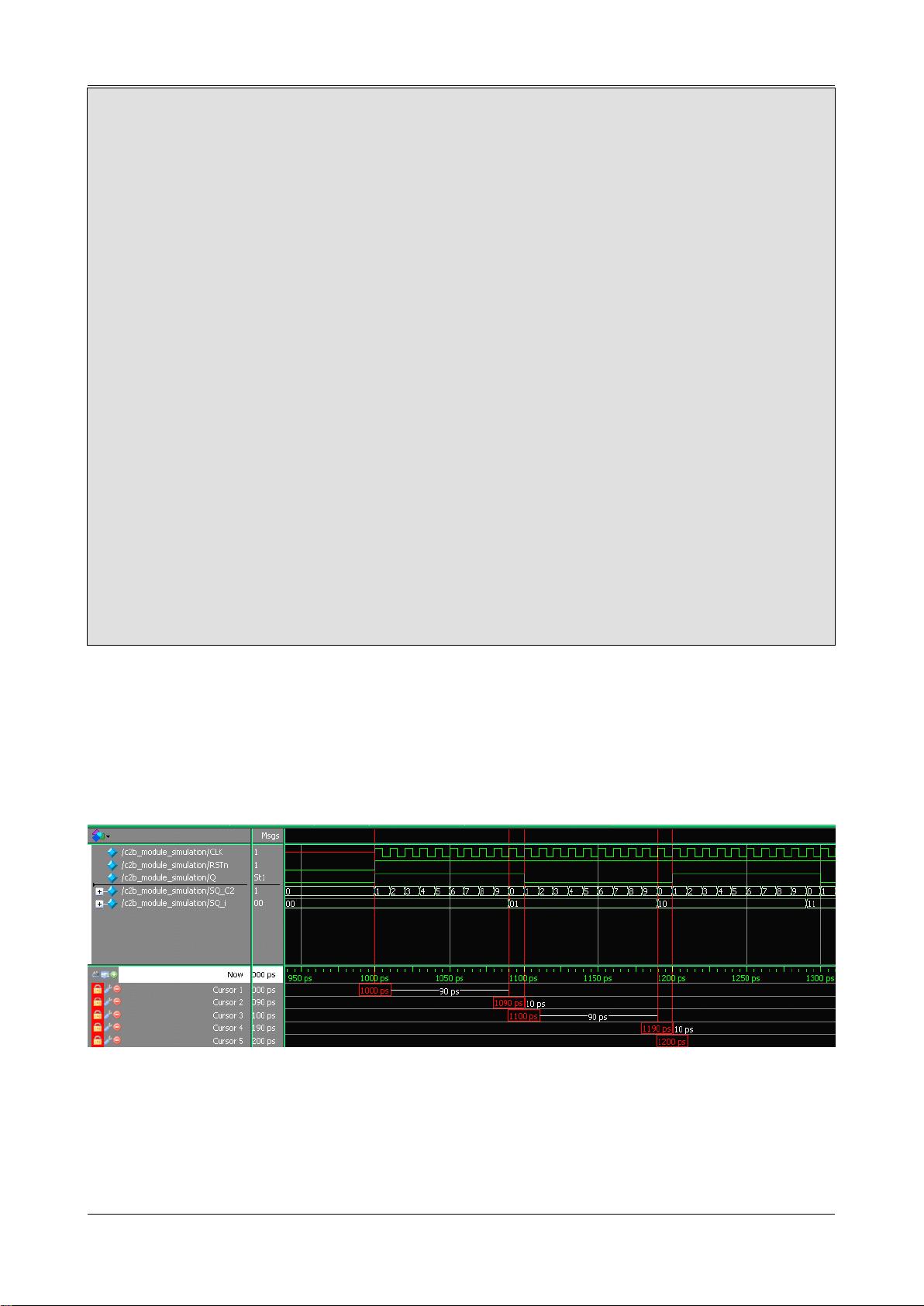

教程还强调了"精密控时"的概念,这是数字系统设计中的一个重要方面。作者提到了两种方法:被动式设计和主动式设计。被动式设计依赖于仿真和时钟精度估算,这种方法虽然有效,但效率较低。相比之下,主动式设计通过利用理想时序、建模技巧和仿顺序操作,可以在设计阶段就实现精确的时序控制,对于复杂的接口协议如IIC和SDRAM尤其适用。

在整合篇中,作者还触及了Verilog HDL中鲜有资料的浮点数处理。鉴于浮点运算在许多应用中的重要性,作者介绍了浮点加法器、减法器、乘法器和除法器的基本工作原理,不仅补充了相关资料的空白,也为后续章节的优化和平衡提供了实例基础。

最后,模块的优化和平衡是整合篇的压轴内容。优化旨在提高设计的效率,减少资源消耗,而平衡则涉及到在性能、功耗和面积之间的权衡。这部分内容指导读者如何通过调整和重构代码,实现设计性能的最优化。

《VerilogHDL 那些事儿 整合篇》是一部全面的教程,它涵盖了从基础到高级的Verilog HDL设计技巧,尤其是关于整合、时序理解和优化策略,对于初学者和有一定经验的工程师来说都是宝贵的资源。

265 浏览量

215 浏览量

114 浏览量

2019-07-11 上传

183 浏览量

116 浏览量

111 浏览量

265 浏览量

点击了解资源详情

blue0432

- 粉丝: 41

- 资源: 25

最新资源

- 初级java笔试题-coding-interview-university:编码面试大学

- cetrainer-unpacker:从可执行文件中提取和解密CheatEngine训练器

- 客户评分:客户评分组件

- 超市理货员岗位职责

- stores-rest-api

- aclipp clipper-crx插件

- VsCommandBuddy:VsCommandBuddy示例,帮助信息,更新信息和支持交流

- zarmarathon2021

- 阅读笔记

- 超市收银组长的工作细则

- 高仿糗事百科客户端应用源码完整版

- 初级java笔试题-awesome-c-mirror:awesome-c的镜子

- HomeAssistant

- JDK8版本jdk-8u202-linux-arm64-vfp-hflt.tar(gz).zip

- Day05:第五天

- xrcs-python:Python练习