VerilogHDL整合篇:循环与时序的智慧融合

需积分: 49 197 浏览量

更新于2024-07-21

1

收藏 15.19MB PDF 举报

"VerilogHDL那些事儿-整合篇"

在深入探讨VerilogHDL时,整合篇是继建模篇和时序篇之后的重要学习阶段。本书主要关注如何将不同设计元素有效地融合在一起,以提升模块的解读性和扩展性。作者强调了在VerilogHDL中理解和应用循环结构(如for、while和dowhile)的重要性,尽管这些在传统的顺序编程语言中非常常见,但在硬件描述语言中实现它们的方式有所不同。

首先,对于Verilog中的循环,作者指出可以通过模拟for和while等循环来实现,但这并非最佳实践。随着对Verilog不同运行模式的理解加深,可以利用基本的计数器和一些整合技巧来创建任何所需的循环,这在第五章中进行了详细阐述。这种方法避免了单纯模仿软件循环的局限性,使设计更加高效。

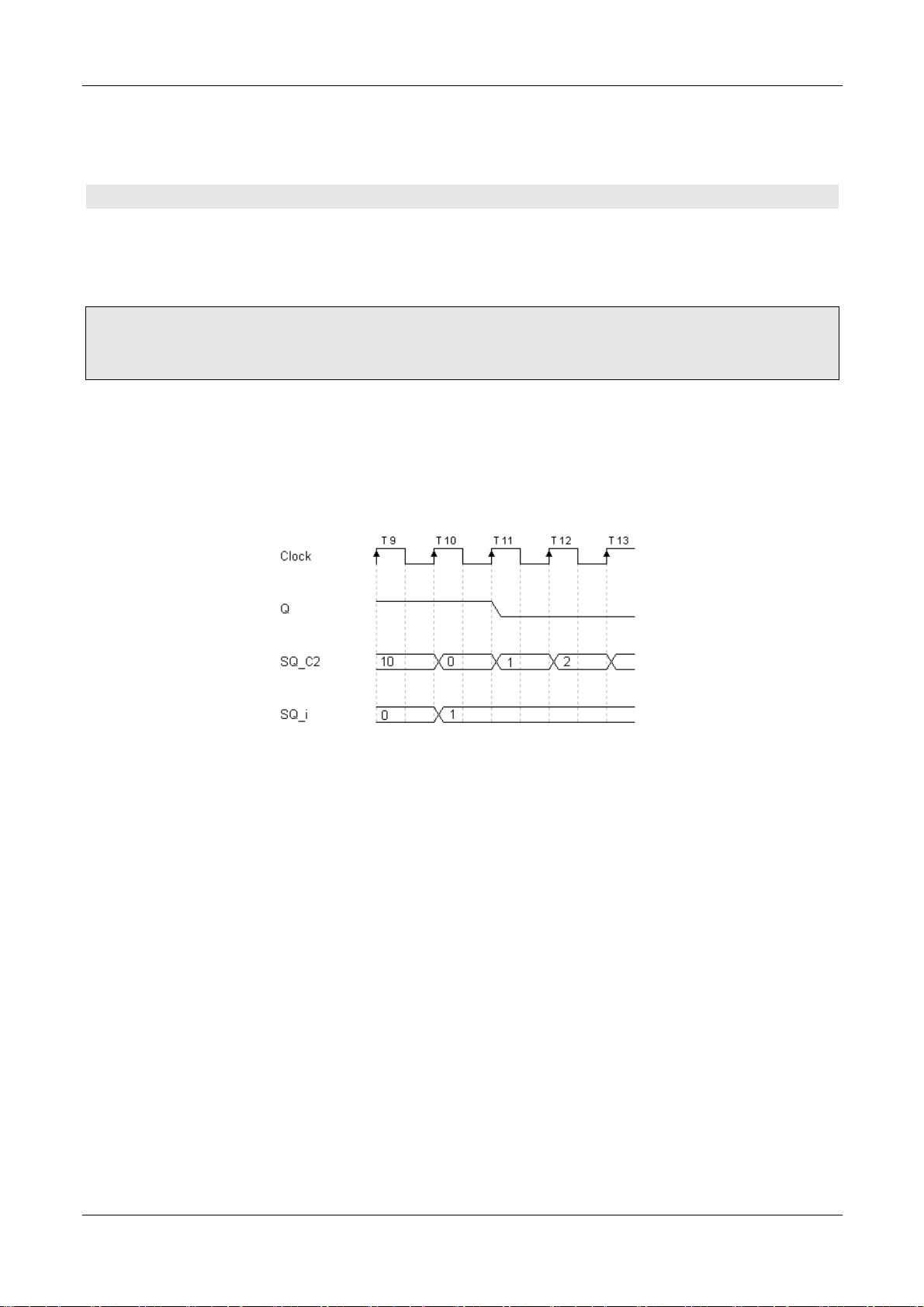

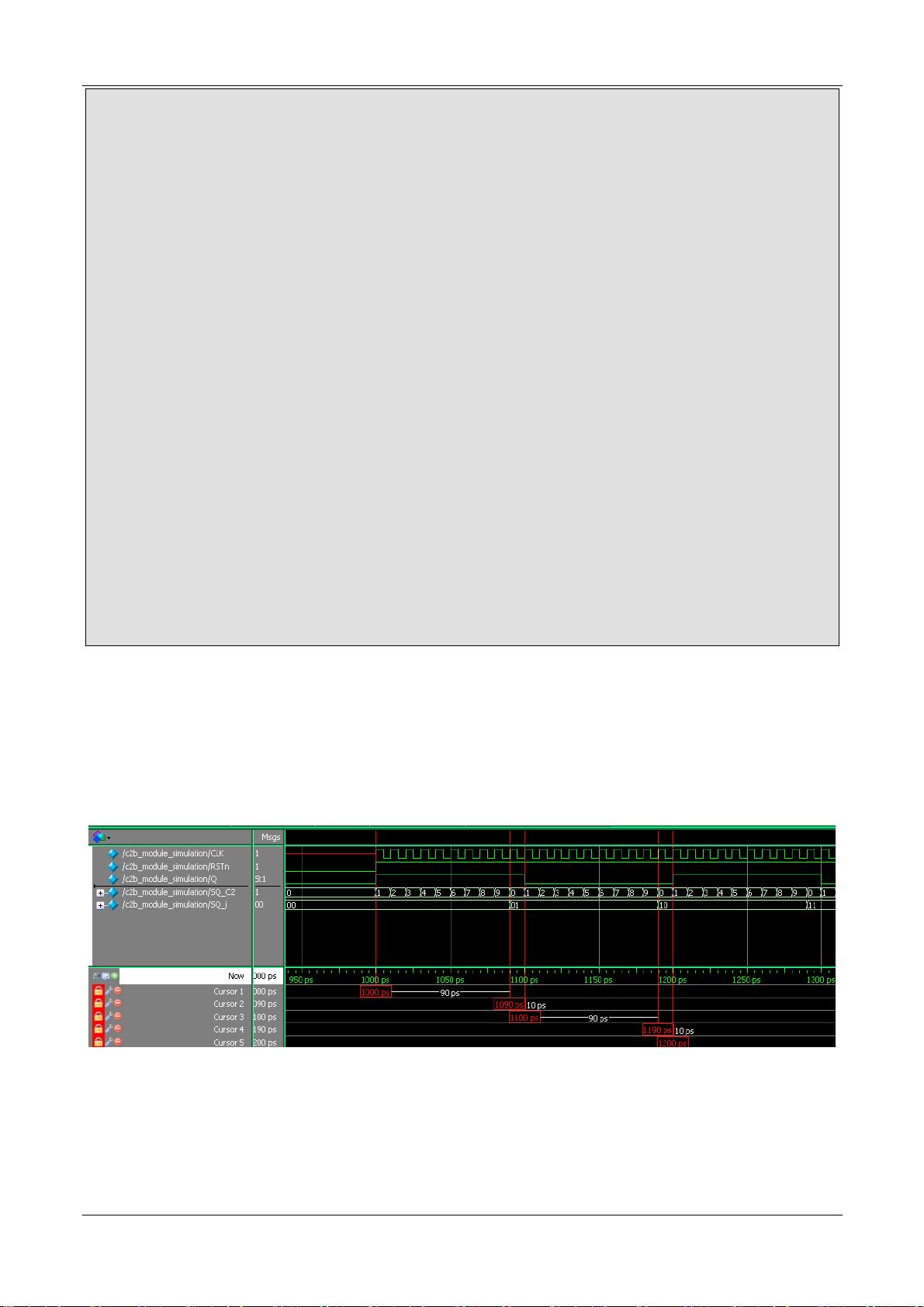

其次,整合篇的核心议题之一是理想时序与物理时序的融合。理想时序代表Verilog的行为模型,而物理时序对应实际硬件的运行方式。尽管两者之间存在一定的冲突,但通过巧妙利用它们之间的"黏糊点",设计者可以编写出同时符合两种时序要求的模块。充分理解理想时序是实现这一目标的关键。

此外,书中的"精密控时"部分讨论了设计方法的差异。传统的被动设计方法依赖于仿真和时钟控制精度的估算,这种方式虽然可行,但效率低下。相反,主动式设计方法提倡在代码层面和概念层面上实现精确时序控制,它基于理想时序建模技巧和仿顺序操作,能更有效地实现复杂的时序需求,如驱动IIC和SDRAM等硬件。

值得注意的是,书中还触及了在Verilog中处理浮点数的罕见主题。由于相关资料稀缺,作者通过构建浮点数加法器、减法器、乘法器和除法器的实例,不仅补充了这方面的资料,也为最后一章的优化和平衡提供了素材。

在模块的优化和平衡部分,作者阐述了如何在保持功能完整性的前提下,减少资源使用,提高性能。优化不仅仅是简化代码,还包括了在设计流程的各个阶段寻找平衡,确保设计既满足功能需求,又能在硬件资源上达到最优。

《Verilog那些事儿-整合篇》是关于VerilogHDL深度学习的一份宝贵资源,它深入探讨了循环结构、时序融合、精确时序控制以及模块优化等关键问题,对提升FPGA设计者的技能大有裨益。

115 浏览量

2019-07-11 上传

215 浏览量

117 浏览量

点击了解资源详情

119 浏览量

蒲公英291

- 粉丝: 104

最新资源

- JavaScript实现影片压缩技术解析

- Duilib文件选择示例深入解析

- LeagueSharp 大会:深入C#编程交流

- 深入理解Spring Boot:基础知识与构建基石

- MATLAB无限循环运行程序直到按键结束操作教程

- STM32CubeMX 5.1.0:微控制器配置与代码生成工具

- TAC项目文档:物联网技术与教育资源共享

- Fiblary Python模块:简化Fibaro Home Center REST API操作

- ttyplot:终端实时数据绘图工具

- 2-16进制转换算法实验简易教程

- MATLAB中不清除命令窗口的ASCII进度条实现

- 全面支持WSLD开发的SoapUI开发包

- React Redux教程核心文件详解

- iOS数据持久化方案性能对比研究

- Raize.v5.5压缩包下载与软件介绍

- Shell脚本实践:文件管理与图像转换技巧