没有合适的资源?快使用搜索试试~ 我知道了~

首页深度解析:内存高手进阶之路与技术误区

深度解析:内存高手进阶之路与技术误区

需积分: 9 2 下载量 136 浏览量

更新于2024-07-24

收藏 4.03MB PDF 举报

"高手进阶终极内存技术"是一份旨在深入探讨内存技术的专业指南,它强调了内存作为计算机性能基石的重要性。在早期,内存主要被看作是购买主板和CPU时的附加品,人们对它的关注仅限于速度层面。然而,1998年440BX主板推出后,内存的时序参数如CL参数开始受到DIYer的关注,这标志着内存技术逐渐从基础走向专业。 自那时起,内存技术的发展进入了一个新阶段,如VIA芯片组的4路交错内存控制(4-Way Interleave)在2000年底/2001年初引入,这使得内存的优化和理解更为复杂。《本刊》在2001年第2期对此进行了详细的解析,首次正确解释了这种交错控制的工作原理和容量限制。这个时期,许多深入的内存技术文章涌现,推动了DIY领域对内存知识的需求提升。 然而,这个知识普及的过程中也存在误区,不少早期的技术文章存在错误,包括对DDR和RDRAM内存的介绍。国内媒体虽然试图引进国外先进的内存技术,但未能确保信息的准确性。这导致了一些读者被引入了错误的理解,尽管如此,对内存技术的热情并未减退,越来越多的玩家渴望深入了解内存的深层次知识,尽管这些知识可能暂时无直接应用,但能满足他们的好奇心和求知欲。 自2001年初以来,媒体对于内存技术文章的接受度持续增长,反映了用户需求的升级。他们不再仅仅满足于基本的内存使用,而是追求对内存工作原理、性能优化等高级知识的掌握。这份"高手进阶终极内存技术"指南正是为了满足这部分技术爱好者的需求,提供一个全面且深入的学习平台,帮助他们突破现有认知,提升系统的性能潜力。

资源详情

资源推荐

从图中可以看出,在 CS#、L-Bank 定址的同时,RAS(Row Address Strobe,行

地址选通脉冲)也处于有效状态。此时 An 地址线则发送具体的行地址。如图中

是 A0-A11,共有 12 个地址线,由于是二进制表示法,所以 共有 4096 个行

(212=4096),A0-A11 的不同数值就确定了具体的行地址。由于行有效的同时

也是相应 L-Bank 有效,所以行有效也可称为 L-Bank 有效。

列读写

行地址确定之后,就要对列地址进行寻址了。但是,地址线仍然是行地址所用的

A0- A11(本例)。没错,在 SDRAM 中,行地址与列地址线是共用的。不过,读/

写的命令是怎么发出的呢?其实没有一个信号是发送读或写的明确命令的,而是

通过芯片的可写状态的控制来达到读/写的目的。显然 WE#信号就是一个关键。

WE#无效时,当然就是读取命令。

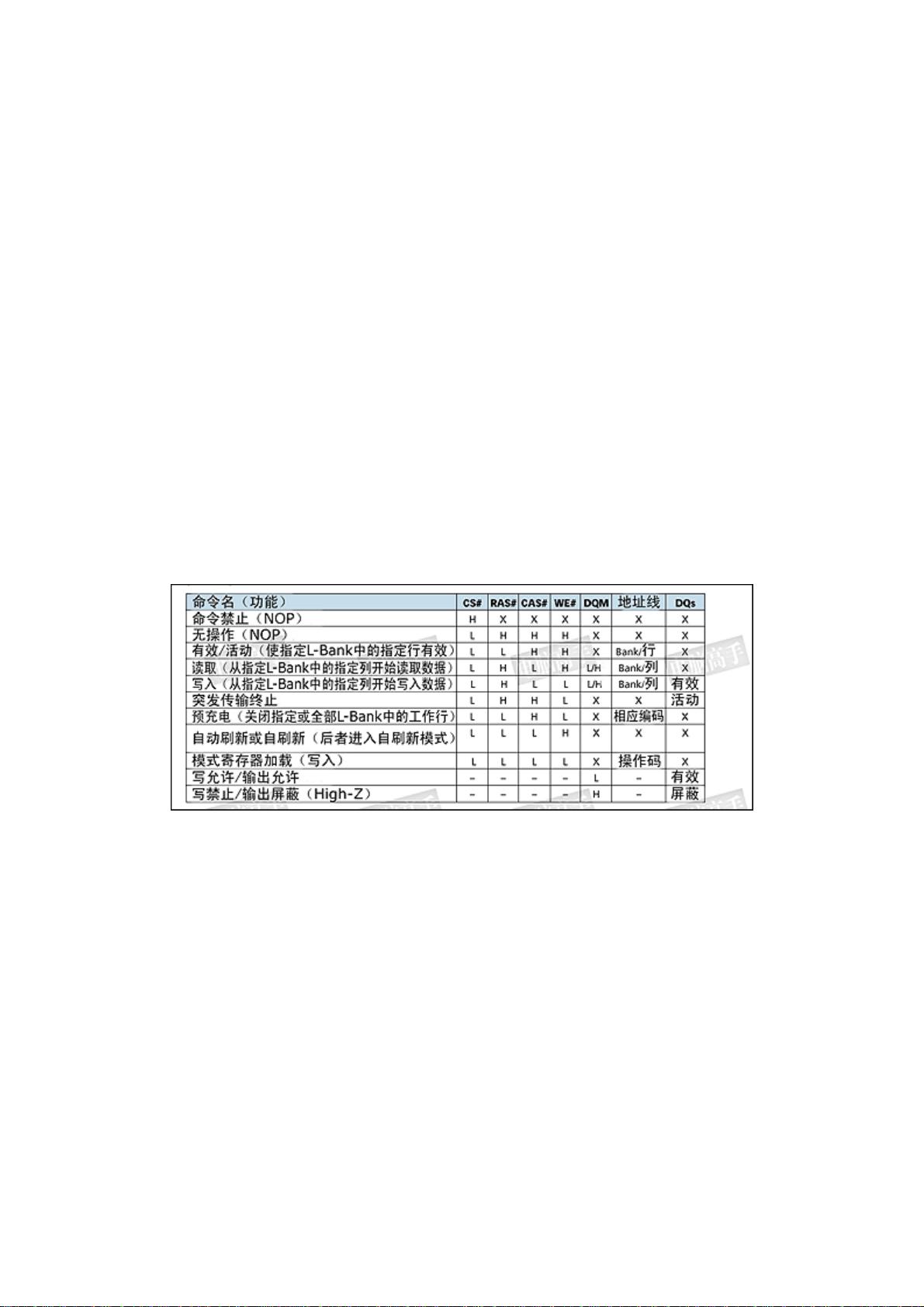

SDRAM 基本操作命令(上表可点击放大), 通过各种控制/地址信号的组合来完

成(H 代表高电平,L 代表低电平,X 表示高低电平均没有影响)。此表中,除

了自刷新命令外,所有命令都是默认 CKE 有效。对于自刷新命令,下文有详解

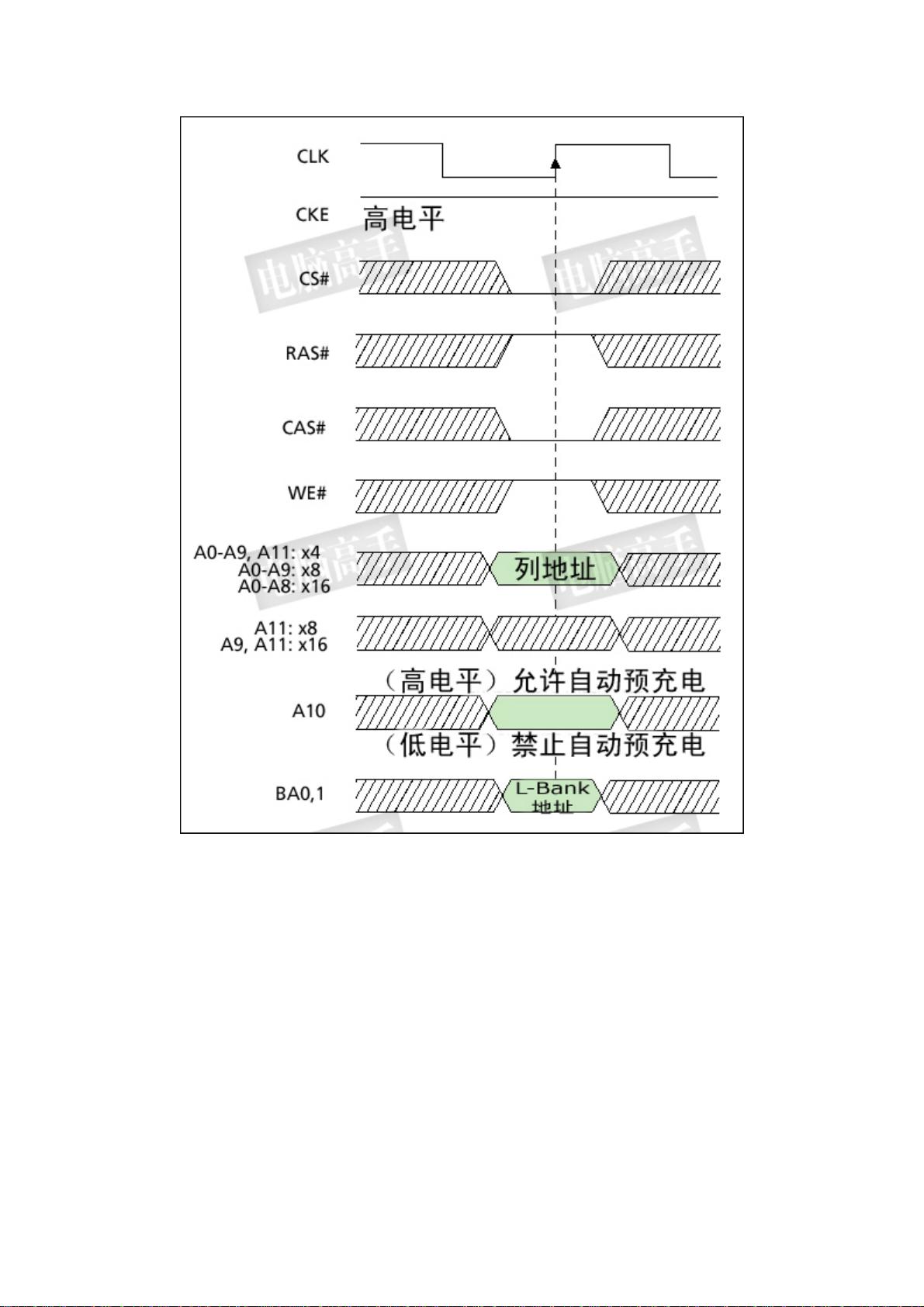

列寻址信号与读写命令是同时发出的。虽然地址线与行寻址共用,但 CAS(Column

Address Strobe,列地址选通脉冲)信号则可以区分开行与列寻址的不同,配合

A0-A9,A11(本例)来确定具体的列地址。

读写操作示意图,读取命令与列地址一块发出(当 WE#为低电平是即为写命令)

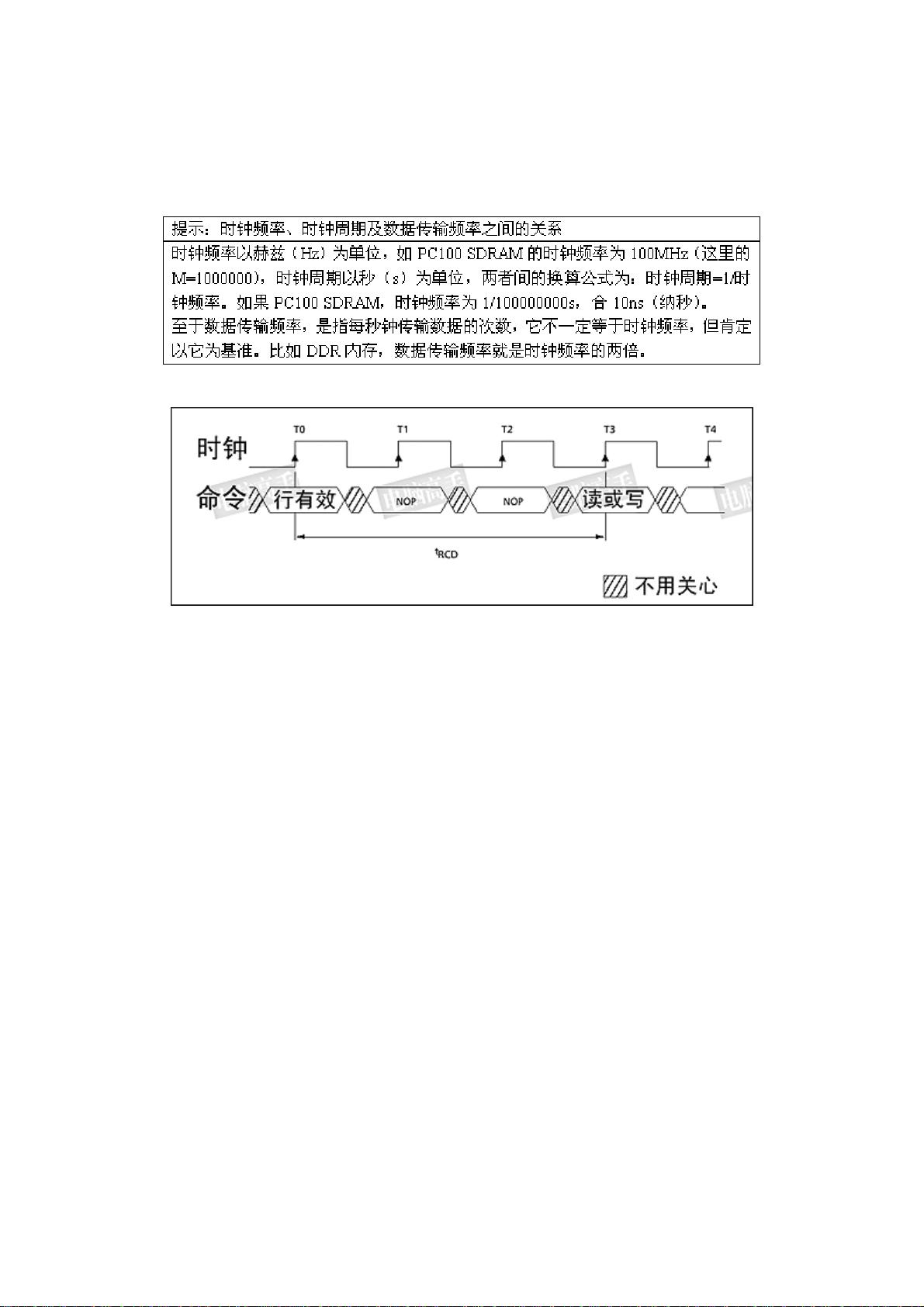

然而,在发送列读写命令时必须要与行有效命令有一个间隔,这个间隔被定义为

tRCD,即 RAS to CAS Delay(RAS 至 CAS 延迟),大家也可以理解为行选通周

期,这应该是根据芯片存储阵列电子元件响应时间(从一种状态到另一种状态变

化的过程)所制定 的延迟。tRCD 是 SDRAM 的一个重要时序参数,可以通过主板

BIOS 经过北桥芯片进行调整,但不能超过厂商的预定范围。广义的 tRCD 以时钟

周期 (tCK,Clock Time)数为单位,比如 tRCD=2,就代表延迟周期为两个时

钟周期,具体到确切的时间,则要根据时钟频率而定,对于 PC100 SDRAM,tRCD=2,

代表 20ns 的延迟,对于 PC133 则为 15ns。

tRCD=3 的时序图

SDRAM 的读/写时序与突发长度

数据输出(读)

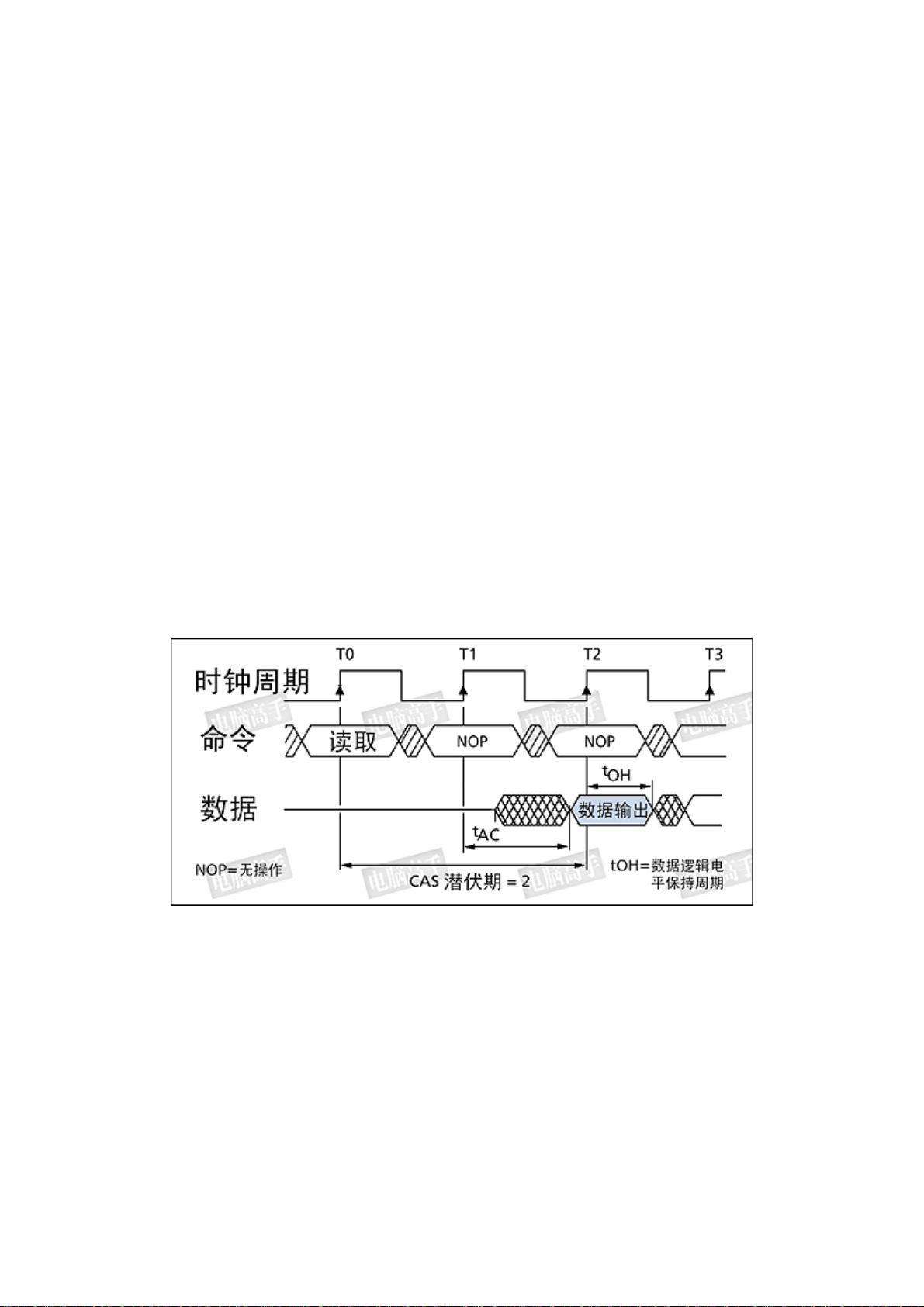

在选定列地址后,就已经确定了具体的存储单元,剩下的事情就是数据通过数据

I/O 通道 (DQ)输出到内存总线上了。但是在 CAS 发出之后,仍要经过一定的

时间才能有数据输出,从 CAS 与读取命令发出到第一笔数据输出的这段时间,被

定义为 CL(CAS Latency,CAS 潜伏期)。由于 CL 只在读取时出现,所以 CL 又

被称为读取潜伏期(RL,Read Latency)。CL 的单位与 tRCD 一样,为时钟周期

数,具体耗时由时钟频率决定。

不过,CAS 并不是在经过 CL 周期之后才送达存储单元。实际上 CAS 与 RAS 一样

是瞬间到 达的,但 CAS 的响应时间要更快一些。为什么呢?假设芯片位宽为 n

个 bit,列数为 c,那么一个行地址要选通 n×c 个存储体,而一个列地址只需选

通 n 个存 储体。但存储体中晶体管的反应时间仍会造成数据不可能与 CAS 在同

一上升沿触发,肯定要延后至少一个时钟周期。

由于芯片体积的原因,存储单元中的电容容量很小,所以信号要经过放大来保证

其有效的识别 性,这个放大/驱动工作由 S-AMP 负责,一个存储体对应一个 S-AMP

通道。但它要有一个准备时间才能保证信号的发送强度(事前还要进行电压比较

以进行 逻辑电平的判断),因此从数据 I/O 总线上有数据输出之前的一个时钟

上升沿开始,数据即已传向 S-AMP,也就是说此时数据已经被触发,经过一定的

驱动时 间最终传向数据 I/O 总线进行输出,这段时间我们称之为 tAC(Access

Time from CLK,时钟触发后的访问时间)。tAC 的单位是 ns,对于不同的频率

各有不同的明确规定,但必须要小于一个时钟周期,否则会因访问时过长而使效

率降低。 比如 PC133 的时钟周期为 7.5ns,tAC 则是 5.4ns。需要强调的是,每

个数据在读取时都有 tAC,包括在连续读取中,只是在进行第一个数据传输 的

同时就开始了第二个数据的 tAC。

CL=2 与 tAC 示意图

CL 的数值不能超出芯片的设计规范,否则会导致内存的不稳定,甚至开不了机

(超频的玩家应 该有体会),而且它也不能在数据读取前临时更改。CL 周期在

开机初始化过程中的 MRS 阶段进行设置,在 BIOS 中一般都允许用户对其调整,

然后 BIOS 控 制北桥芯片在开机时通过 A4-A6 地址线对 MR 中 CL 寄存器的信息进

行更改。

不过,从存储体的结构图上可以看出,原本逻辑状态为 1 的电容在读取操作后,

会因放电而变为 逻辑 0。所以,以前的 DRAM 为了在关闭当前行时保证数据的可

靠性,要对存储体中原有的信息进行重写,这个任务由数据所经过的刷新放大器

来完成,它根据逻 辑电平状态,将数据进行重写(逻辑 0 时就不重写),由于

这个操作与数据的输出是同步进行互不冲突,所以不会产生新的重写延迟。后来

通过技术的改良,刷新放 大器被取消,其功能由 S-AMP 取代,因为在读取时它

会保持数据的逻辑状态,起到了一个 Cache 的作用,再次读取时由它直接发送即

可,不用再进行新的寻 址输出,此时数据重写操作则可在预充电阶段完成。

数据输入(写)

数据写入的操作也是在 tRCD 之后进行,但此时没有了 CL(记住,CL 只出现在读

取操作中),行寻址与列寻址的时序图和上文一样,只是在列寻址时,WE#为有

效状态。

剩余92页未读,继续阅读

javingong

- 粉丝: 0

- 资源: 4

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 计算机人脸表情动画技术发展综述

- 关系数据库的关键字搜索技术综述:模型、架构与未来趋势

- 迭代自适应逆滤波在语音情感识别中的应用

- 概念知识树在旅游领域智能分析中的应用

- 构建is-a层次与OWL本体集成:理论与算法

- 基于语义元的相似度计算方法研究:改进与有效性验证

- 网格梯度多密度聚类算法:去噪与高效聚类

- 网格服务工作流动态调度算法PGSWA研究

- 突发事件连锁反应网络模型与应急预警分析

- BA网络上的病毒营销与网站推广仿真研究

- 离散HSMM故障预测模型:有效提升系统状态预测

- 煤矿安全评价:信息融合与可拓理论的应用

- 多维度Petri网工作流模型MD_WFN:统一建模与应用研究

- 面向过程追踪的知识安全描述方法

- 基于收益的软件过程资源调度优化策略

- 多核环境下基于数据流Java的Web服务器优化实现提升性能

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功