MAXPS—Maximum of Packed Single-Precision Floating-Point Values

INSTRUCTION SET REFERENCE, M-U

Vol. 2B 4-15

MAXPS—Maximum of Packed Single-Precision Floating-Point Values

Instruction Operand Encoding

Description

Performs a SIMD compare of the packed single-precision floating-point values in the first source operand and the

second source operand and returns the maximum value for each pair of values to the destination operand.

If the values being compared are both 0.0s (of either sign), the value in the second operand (source operand) is

returned. If a value in the second operand is an SNaN, then SNaN is forwarded unchanged to the destination (that

is, a QNaN version of the SNaN is not returned).

If only one value is a NaN (SNaN or QNaN) for this instruction, the second operand (source operand), either a NaN

or a valid floating-point value, is written to the result. If instead of this behavior, it is required that the NaN source

operand (from either the first or second operand) be returned, the action of MAXPS can be emulated using a

sequence of instructions, such as, a comparison followed by AND, ANDN and OR.

EVEX encoded versions: The first source operand (the second operand) is a ZMM/YMM/XMM register. The second

source operand can be a ZMM/YMM/XMM register, a 512/256/128-bit memory location or a 512/256/128-bit vector

broadcasted from a 32-bit memory location. The destination operand is a ZMM/YMM/XMM register conditionally

updated with writemask k1.

VEX.256 encoded version: The first source operand is a YMM register. The second source operand can be a YMM

register or a 256-bit memory location. The destination operand is a YMM register. The upper bits (MAX_VL-1:256)

of the corresponding ZMM register destination are zeroed.

VEX.128 encoded version: The first source operand is a XMM register. The second source operand can be a XMM

register or a 128-bit memory location. The destination operand is a XMM register. The upper bits (MAX_VL-1:128)

of the corresponding ZMM register destination are zeroed.

128-bit Legacy SSE version: The second source can be an XMM register or an 128-bit memory location. The desti-

nation is not distinct from the first source XMM register and the upper bits (MAX_VL-1:128) of the corresponding

ZMM register destination are unmodified.

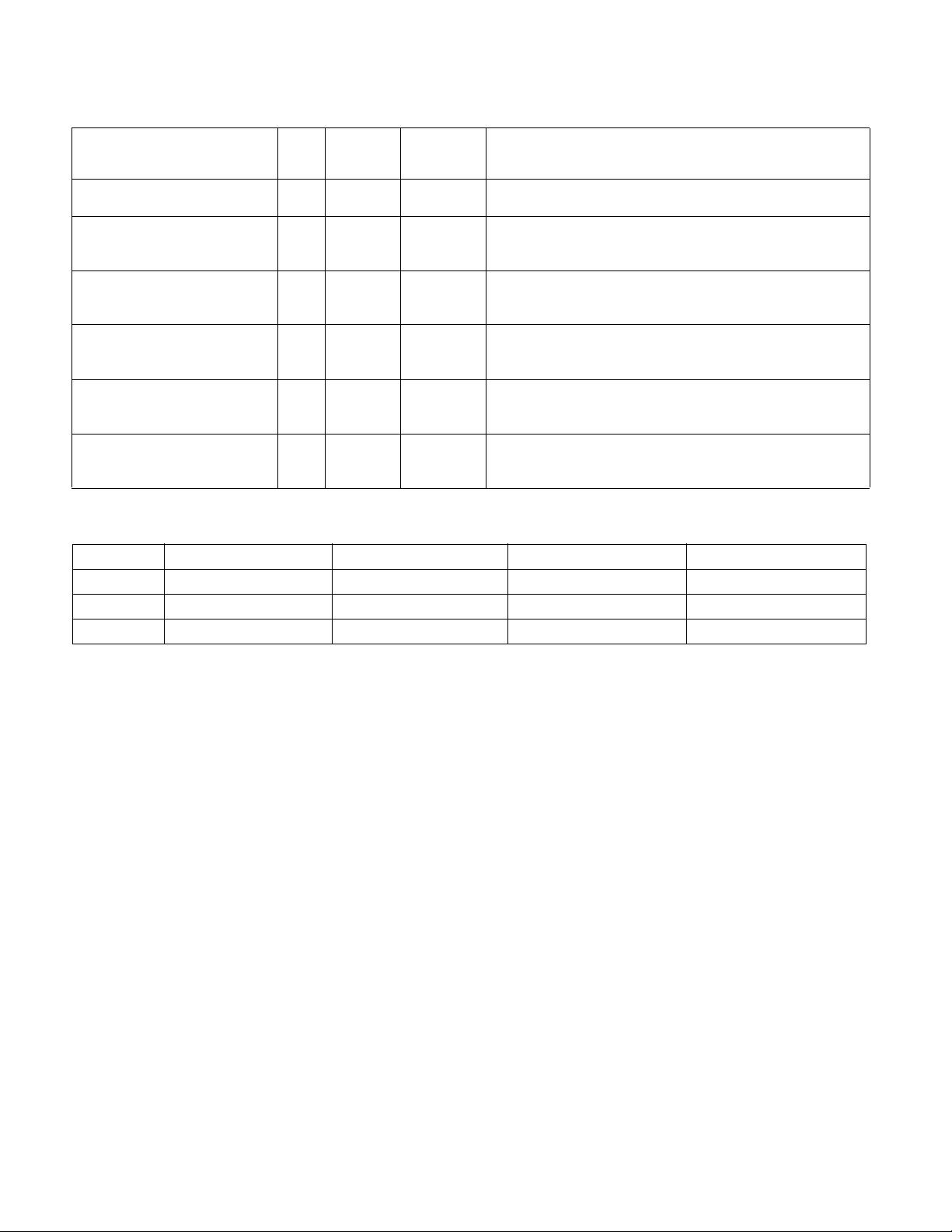

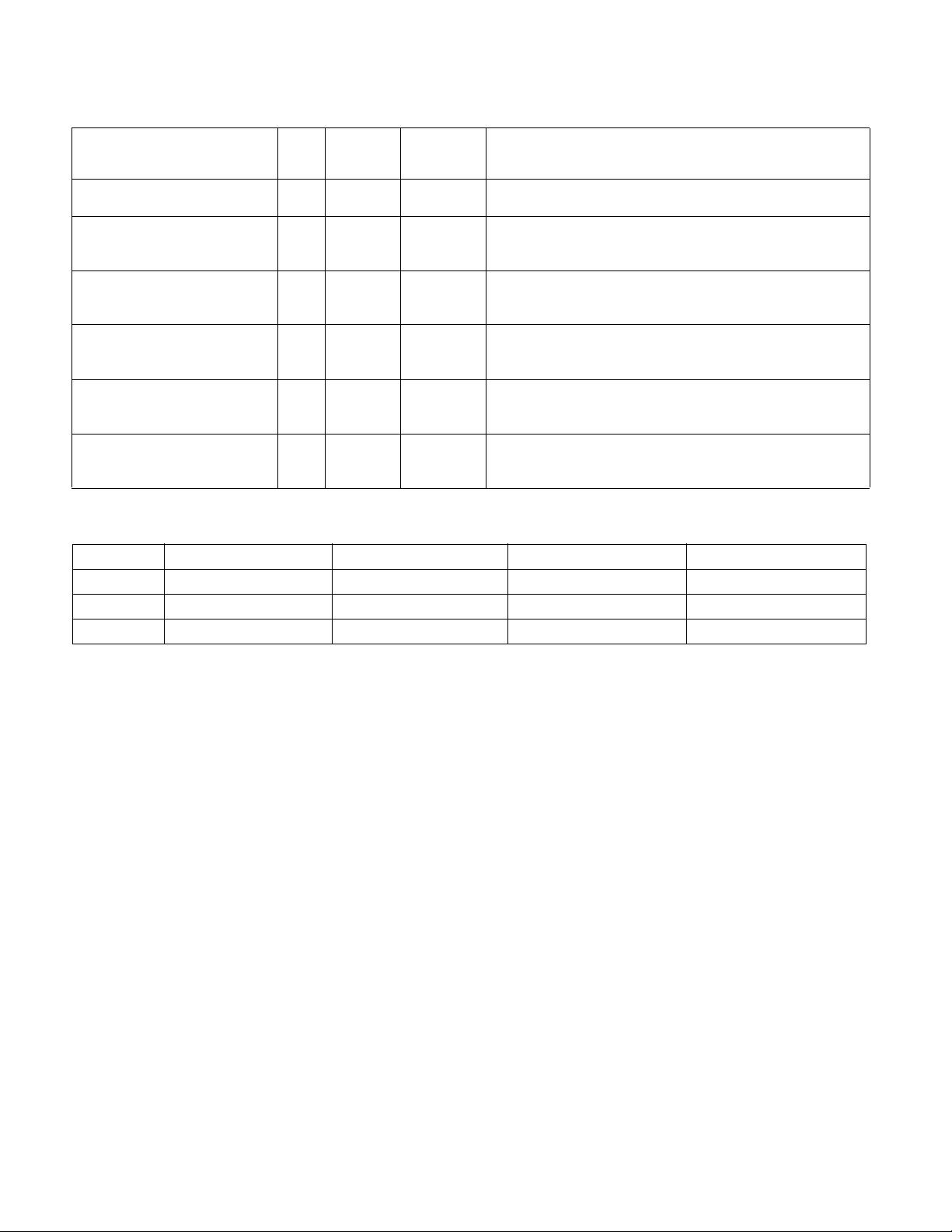

Opcode/

Instruction

Op /

En

64/32

bit Mode

Support

CPUID

Feature

Flag

Description

0F 5F /r

MAXPS xmm1, xmm2/m128

RM V/V SSE Return the maximum single-precision floating-point values

between xmm1 and xmm2/mem.

VEX.NDS.128.0F.WIG 5F /r

VMAXPS xmm1, xmm2,

xmm3/m128

RVM V/V AVX Return the maximum single-precision floating-point values

between xmm2 and xmm3/mem.

VEX.NDS.256.0F.WIG 5F /r

VMAXPS ymm1, ymm2,

ymm3/m256

RVM V/V AVX Return the maximum single-precision floating-point values

between ymm2 and ymm3/mem.

EVEX.NDS.128.0F.W0 5F /r

VMAXPS xmm1 {k1}{z}, xmm2,

xmm3/m128/m32bcst

FV V/V AVX512VL

AVX512F

Return the maximum packed single-precision floating-point

values between xmm2 and xmm3/m128/m32bcst and store

result in xmm1 subject to writemask k1.

EVEX.NDS.256.0F.W0 5F /r

VMAXPS ymm1 {k1}{z}, ymm2,

ymm3/m256/m32bcst

FV V/V AVX512VL

AVX512F

Return the maximum packed single-precision floating-point

values between ymm2 and ymm3/m256/m32bcst and store

result in ymm1 subject to writemask k1.

EVEX.NDS.512.0F.W0 5F /r

VMAXPS zmm1 {k1}{z}, zmm2,

zmm3/m512/m32bcst{sae}

FV V/V AVX512F Return the maximum packed single-precision floating-point

values between zmm2 and zmm3/m512/m32bcst and store

result in zmm1 subject to writemask k1.

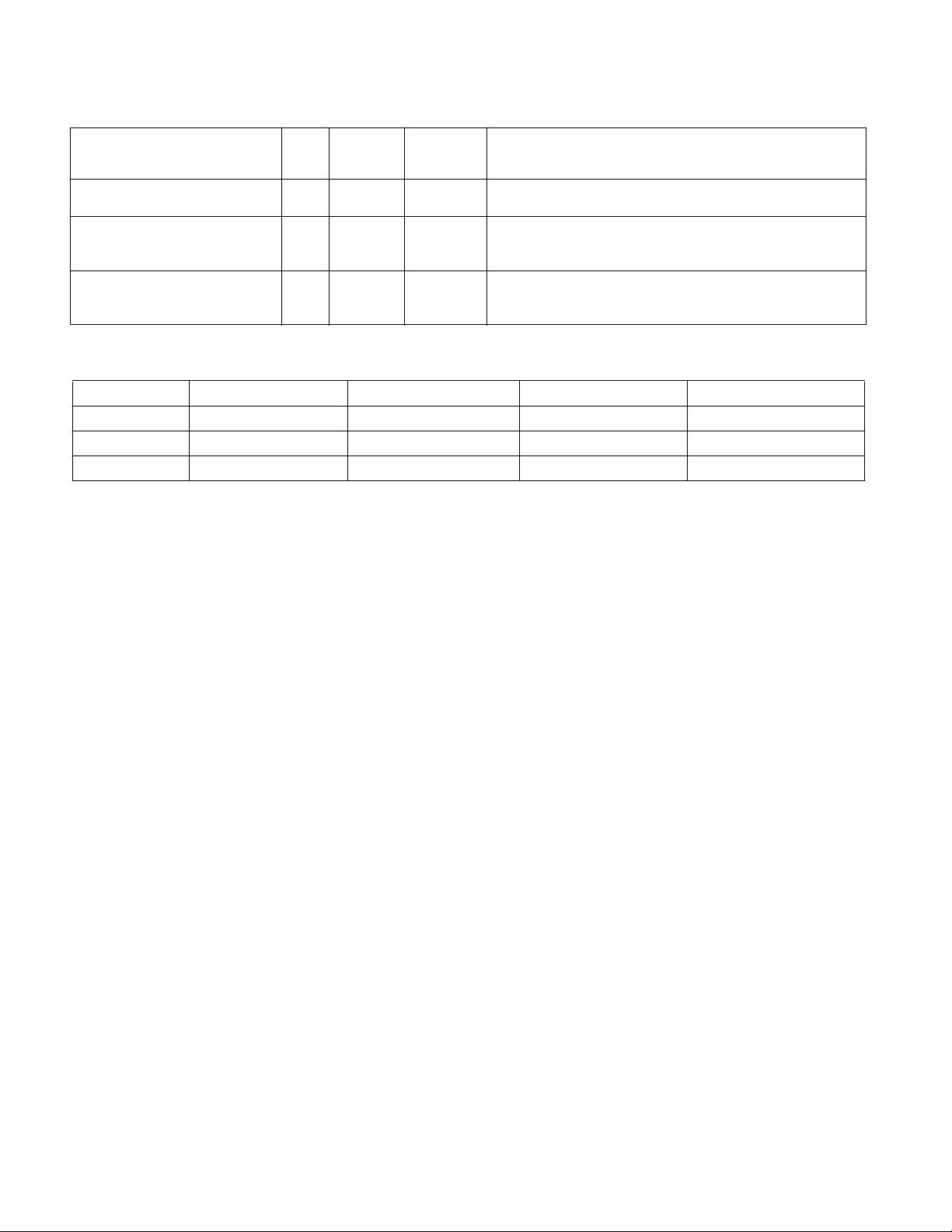

Op/En Operand 1 Operand 2 Operand 3 Operand 4

RM ModRM:reg (r, w) ModRM:r/m (r) NA NA

RVM ModRM:reg (w) VEX.vvvv ModRM:r/m (r) NA

FV ModRM:reg (w) EVEX.vvvv ModRM:r/m (r) NA