7系列FPGA Kintex-7 SelectIO特性与设计指南

需积分: 5 149 浏览量

更新于2024-06-26

收藏 3.25MB DOCX 举报

“FPGA(Kintex-7)学习笔记主要涵盖了Kintex-7 FPGA的I/O系统,包括SelectIO结构的分析,强调了不同类型的I/O banks(高性能HP和宽范围HR)以及它们各自的支持特性。内容还涉及到SelectIO资源的配置灵活性,如可编程的输出电流、边沿速率和内部参考电压。此外,文中提到了各类型I/O bank的管脚数量和用途,以及如何根据需求配置为单端或差分信号。最后,提供了关于7系列FPGA I/O Bank设计的一般指导。”

Kintex-7 FPGA是一款先进的现场可编程门阵列,其I/O系统是其核心组成部分之一。该系列的I/O banks分为高性能(HP)和宽范围(HR)两大类,以适应不同的接口需求。HP banks主要针对高速内存接口和芯片间高速连接,支持1.8V的最大电压,而HR banks则支持更广泛的I/O电平标准,最高可达3.3V。不过,并非所有I/O标准和电流驱动在两种bank中都可用,例如LVDS在HR和HP banks中均得到支持。

SelectIO是Kintex-7 FPGA中的关键特性,它提供了一种可配置的I/O解决方案,能够适应多种可变标准接口,包括可编程的输出电流、边沿速率、DCI(直流电流隔离)片上端接和内部参考电压(INTERNAL_VREF)。每个bank通常有50个SelectIO引脚,其中两个用于单端I/O,其余48个可配置为单端或差分I/O。值得注意的是,HR banks不支持DCI功能。

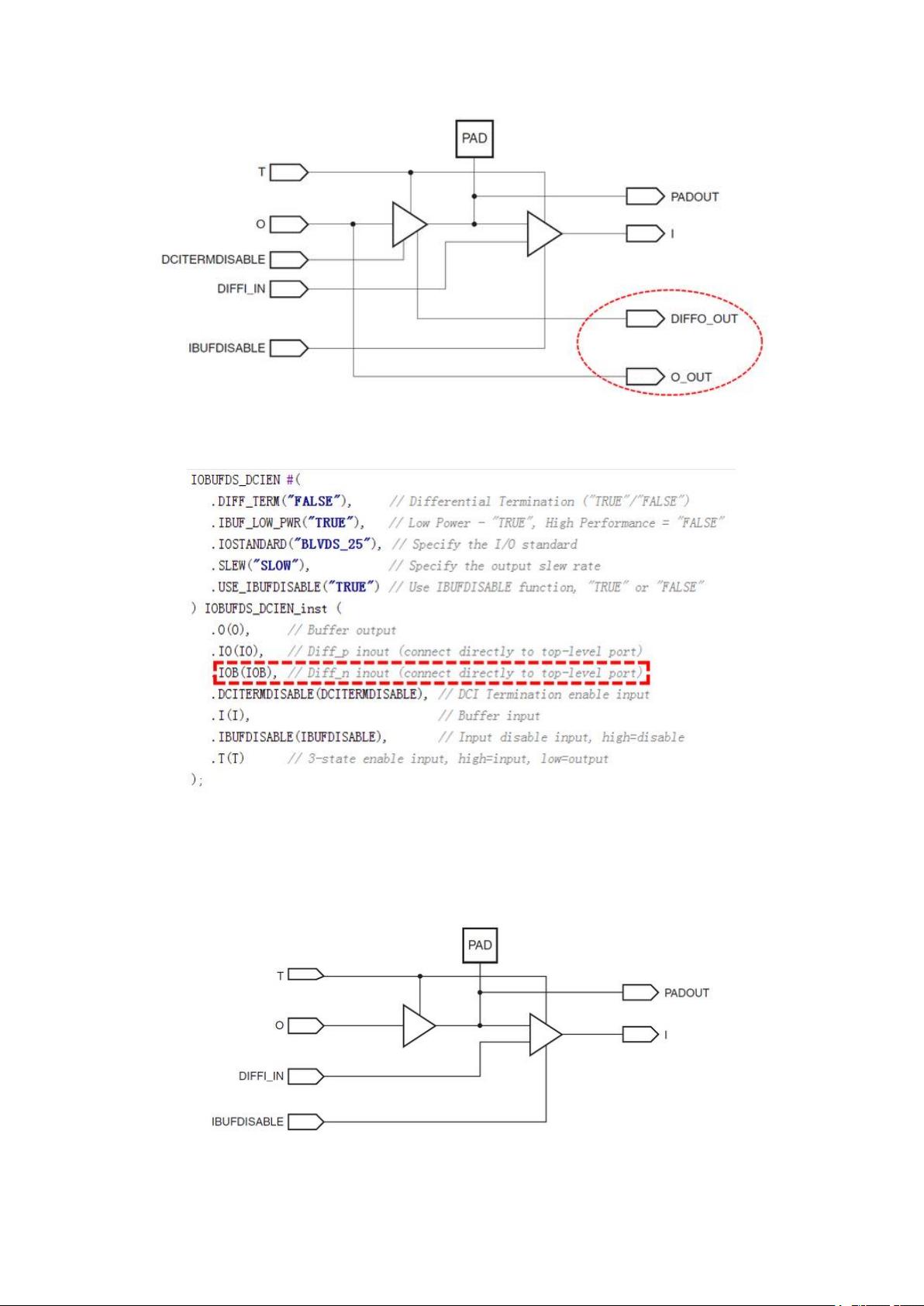

在I/O配置中,SelectIO引脚可以被设定为输入、输出或三态模式,并能支持单端和差分信号。这包括常见的单端标准如LVCMOS、LVTTL、HSTL、PCI和SSTL,以及差分标准如Mini_LVDS、RSDS、PPDS、BLVDS等。图4至图11展示了不同类型I/O bank的内部结构和配置选项,包括只能作为单端信号的HP和HR IOB,以及可配置为单端或差分信号的常规HP和HR IOB。

在设计7系列FPGA的I/O时,需要遵循特定的规则,例如,正确选择适合应用的I/O bank,理解每个bank的物理限制,以及充分利用SelectIO的可配置性来优化性能和兼容性。这需要设计师充分了解每个bank的特性,包括它们支持的电压水平、I/O标准和配置选项,以便在设计阶段就能确保系统的可靠性和效率。

Kintex-7 FPGA的SelectIO系统提供了一种强大的工具,允许设计者灵活地适应各种接口标准和性能需求。通过深入理解其结构和配置机制,可以有效地利用这些资源来创建高性能、低功耗的FPGA设计。在进行实际设计时,应结合具体的项目需求,仔细评估并选择合适的I/O配置,遵循FPGA厂商提供的设计指导,以确保设计的成功实施。

129 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

212 浏览量

324 浏览量

421 浏览量

298 浏览量

103 浏览量

Filthyfrank

- 粉丝: 1w+

- 资源: 32

最新资源

- another-round:另一轮琐事游戏

- RabbitMQ-Demo.zip

- Story-app-2:故事应用

- c-simple-libs:简单,干净,仅标头,C库

- SoftEngG1B:软件工程项目

- 水晶动物图标下载

- 可执行剑:关于剑的游戏

- monke-lang:德蒙克的威

- 虎皮鹦鹉图标下载

- Django_Personal_Portfolio:使用Django制作的投资组合网站

- hassant5577.github.io

- shaarlo:统一Shaarlis Rss

- 4boostpag

- Công Cụ Đặt Hàng Của Express-crx插件

- 米老鼠图标下载

- AdaptableApp:CITRIS 应用程序竞赛