没有合适的资源?快使用搜索试试~ 我知道了~

首页惠普HP-DV3主板维修原理图详解

惠普HP-DV3主板维修原理图详解

需积分: 13 3 下载量 39 浏览量

更新于2024-07-27

1

收藏 1.58MB PDF 举报

"惠普HP-DV3笔记本主板的维修原理图"

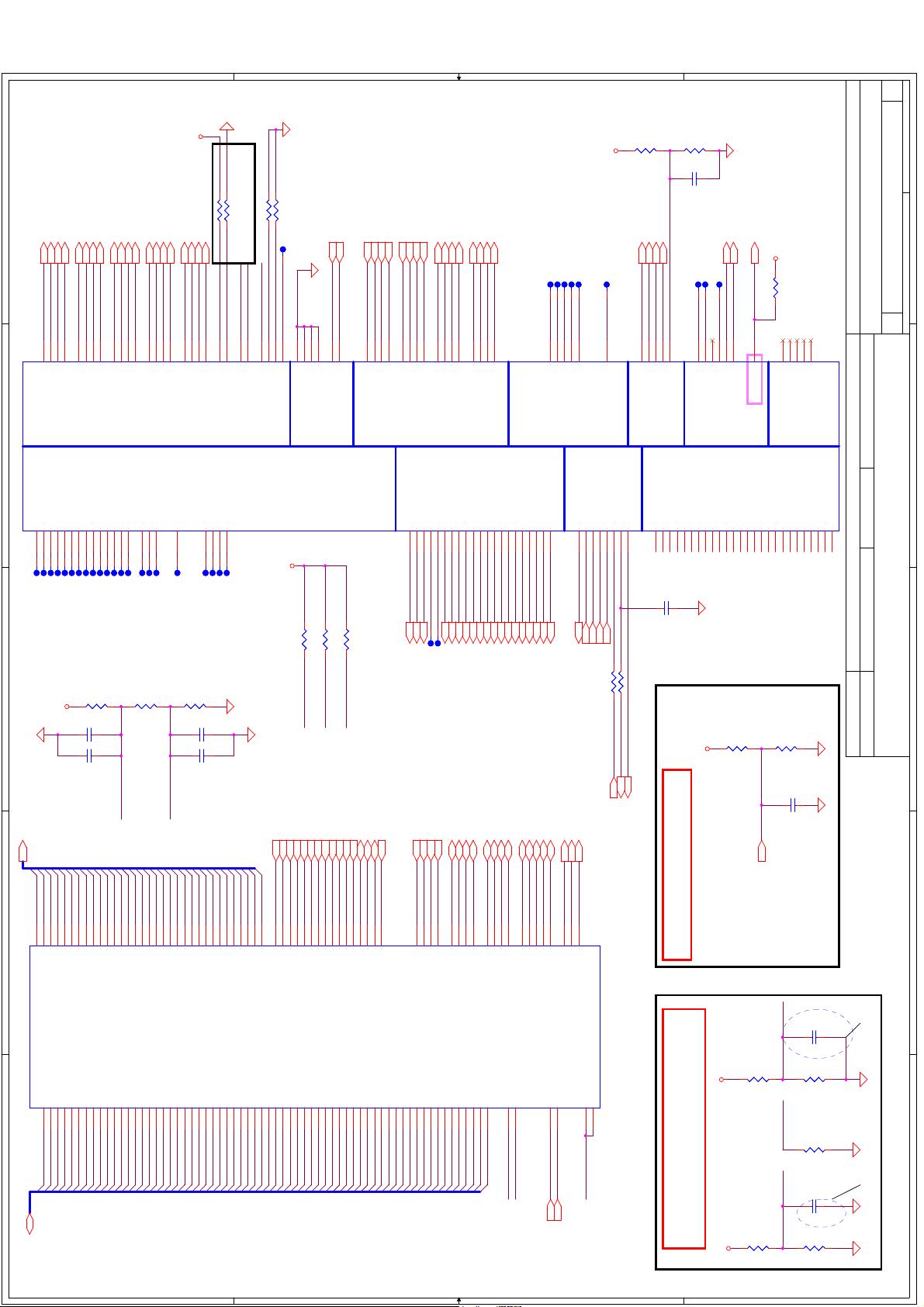

本文将深入探讨惠普HP-DV3笔记本电脑主板的维修原理图,这是一份由Compal Electronics, Inc. 制作并拥有知识产权的技术文档,包含机密及商业秘密信息。这份原理图详细描绘了主板的电路布局、组件连接和功能模块,对于维修人员而言是至关重要的参考资料。

在进行笔记本主板维修时,了解原理图至关重要。原理图是电路设计的基础,它用图形符号表示各种电子元件,并通过线条和箭头展示它们之间的连接关系。对于惠普HP-DV3的主板,原理图会展示电源管理、CPU供电、内存接口、显卡、USB端口、PCI-E接口、硬盘接口、无线网卡、音频电路以及电池充电管理等关键部分的详细信息。

首先,电源管理部分包括AC适配器输入处理、电压转换、电源开关控制以及电池状态监测。理解这些部分的工作原理有助于识别和解决电源相关的问题,如不充电、无法开机或电源故障。

其次,CPU供电部分是主板的核心,因为它直接关系到处理器的稳定运行。原理图会显示不同电压轨的设计,包括CPU核心电压、I/O电压和内存电压,以及对应的电压调节模块(VRM)。维修时需确保这些电压稳定且符合规格,以防过热或性能问题。

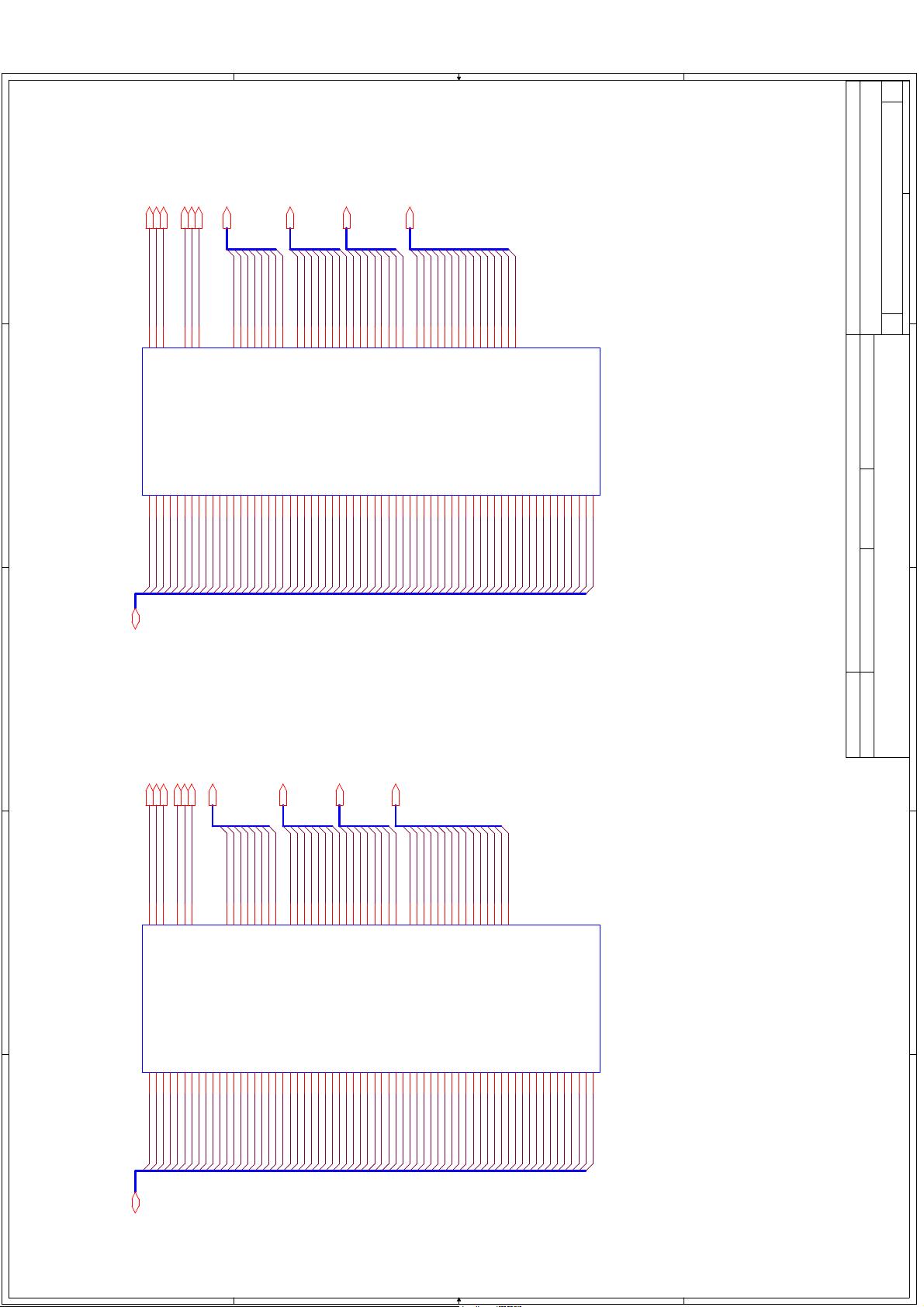

内存接口部分展示了内存条与主板的连接方式,包括数据线、地址线和控制信号线。如果笔记本出现内存兼容性问题或内存故障,查看这部分可以确定问题所在。

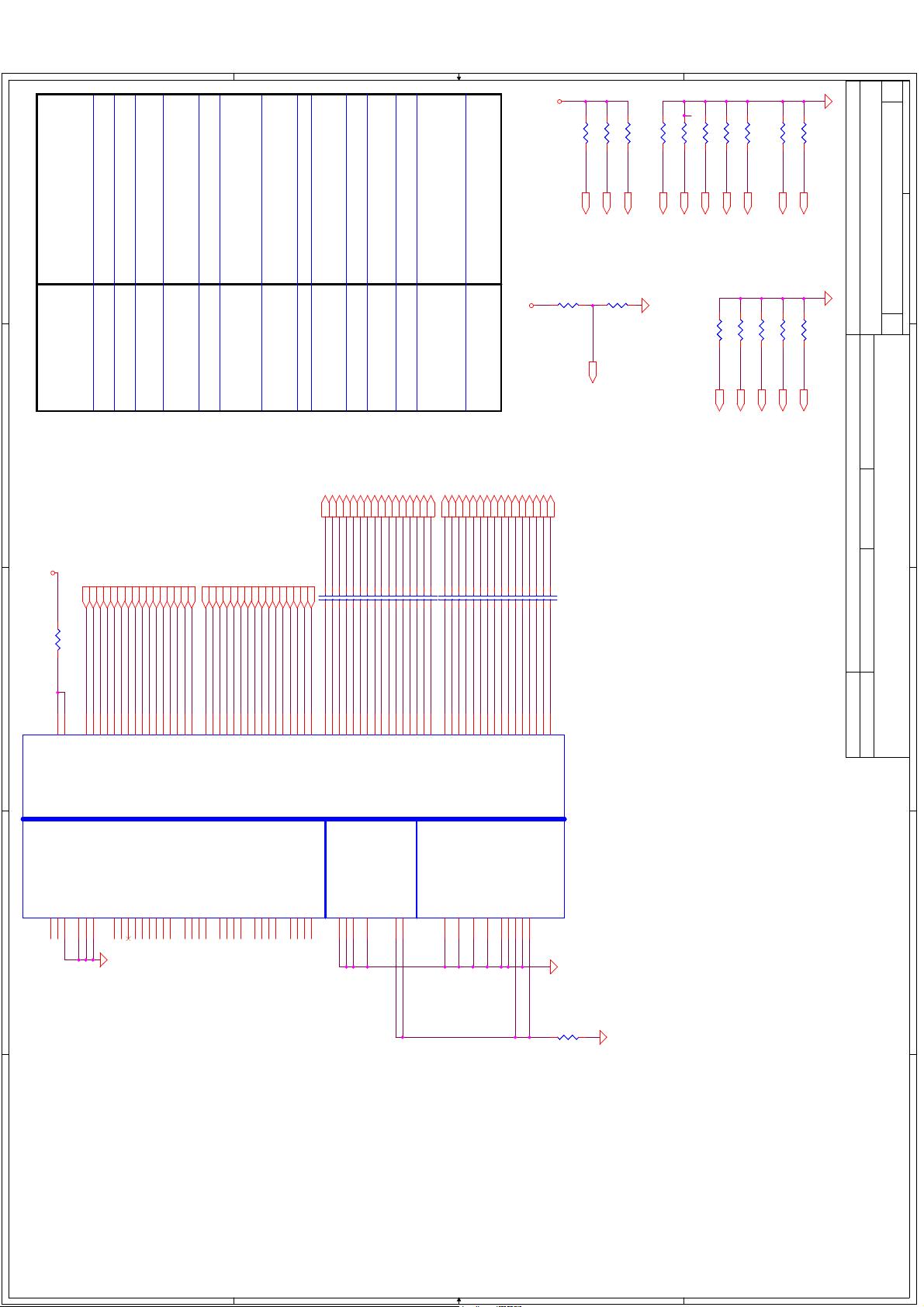

显卡部分可能包括集成显卡和独立显卡,原理图会展示GPU的供电、显存以及与显示器的接口。当视频输出出现问题时,这部分是排查的重点。

此外,USB端口、PCI-E接口和硬盘接口的电路图可以帮助识别外部设备连接问题。例如,USB端口的电源和数据传输线路,PCI-E接口的信号完整性,以及硬盘的SATA接口和电源连接。

无线网卡和音频电路部分则涉及网络通信和声音输出。如果无线网络不稳定或音质有问题,检查这些部分的电路连接和组件状态是必要的。

最后,电池充电管理部分涉及电池的充放电控制和电池健康监测。理解这一部分可以帮助诊断电池无法充电或者电池寿命缩短的问题。

在维修过程中,依据原理图进行故障定位,可以避免盲目拆解,提高修复效率。同时,这份原理图也强调了保密性,未经Compal Electronics, Inc. 的授权,不得转让或披露给第三方。因此,维修人员必须遵守相关的知识产权规定,合法合规地使用这份珍贵的资料。

惠普HP-DV3笔记本主板的维修原理图是维修人员的得力工具,它提供了全面的电路信息,有助于精确诊断和修复主板故障。通过理解和运用这份原理图,不仅可以提升维修技能,还能保护用户的隐私和设备安全。

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

PM_EXTTS#0

V_DDR_MCH_REF

H_RCOMP

CLKREQ#_7

+H_SWNG

H_D#32

H_D#24

H_D#19

H_D#59

H_D#42

H_D#36

H_D#3

H_D#40

H_RCOMP

H_D#55

H_D#4

H_D#60

H_D#30

H_D#34

H_D#27

H_D#1

H_D#23

H_D#51

H_D#48

H_D#46

H_D#44

H_D#39

H_D#22

H_D#15

H_D#14

H_D#9

H_D#56

H_D#54

H_D#8

H_RESET#

H_D#37

H_D#35

H_D#28

H_D#25

H_D#12

H_D#38

H_D#26

H_D#11

H_D#7

H_D#53

H_D#52

H_D#41

H_D#18

H_D#10

+H_VREF

H_D#57

H_D#33

H_D#29

+H_SWNG

H_D#6

H_D#45

H_D#43

H_D#20

H_D#61

H_D#17

H_D#63

H_D#58

H_D#21

H_D#16

H_D#50

H_CPUSLP#

H_D#62

H_D#5

H_D#49

H_D#31

H_D#2

H_D#47

H_D#13

H_D#0

H_A#7

H_A#12

H_A#32

H_A#24

H_A#3

H_A#18

H_A#21

H_A#16

H_A#19

H_A#31

H_A#27

H_A#5

H_A#30

H_A#9

H_A#26

H_A#14

H_A#11

H_A#22

H_A#23

H_A#34

H_A#20

H_A#8

H_A#15

H_A#6

H_A#25

H_A#17

H_A#4

H_A#13

H_A#33

H_A#29

H_A#28

H_A#10

H_A#35

CLK_MCH_BCLK#

H_LOCK#

CLK_MCH_BCLK

H_ADSTB#1

H_DEFER#

H_HITM#

H_ADS#

H_BR0#

H_DBSY#

H_HIT#

H_BPRI#

H_DRDY#

H_BNR#

H_DPWR#

H_ADSTB#0

H_TRDY#

+H_VREF

H_DINV#0

H_DINV#3

H_DINV#1

H_DINV#2

H_DSTBN#1

H_DSTBN#3

H_DSTBN#0

H_DSTBN#2

H_DSTBP#2

H_DSTBP#0

H_DSTBP#3

H_DSTBP#1

H_REQ#0

H_REQ#3

H_REQ#1

H_REQ#4

H_REQ#2

H_RS#1

H_RS#0

H_RS#2

MCH_CLKSEL0

SMRCOMP_VOL

+CL_VREF

MCH_ICH_SYNC#

CLKREQ#_7

CL_CLK0

CL_DATA0

CL_RST#

M_PWROK

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

CLK_MCH_3GPLL#

CLK_MCH_3GPLL

SM_PWROK

SM_REXT

V_DDR_MCH_REF

M_CLK_DDR3

M_CLK_DDR#0

M_CLK_DDR#1

M_CLK_DDR#2

M_CLK_DDR#3

M_CLK_DDR2

M_CLK_DDR0

M_CLK_DDR1

SMRCOMP_VOH

SMRCOMP_VOL

M_ODT1

SMRCOMP#

M_ODT3

M_ODT0

M_ODT2

SMRCOMP

DDR_CKE0_DIMMA

DDR_CKE1_DIMMA

DDR_CKE3_DIMMB

DDR_CS1_DIMMA#

DDR_CKE2_DIMMB

DDR_CS0_DIMMA#

DDR_CS3_DIMMB#

DDR_CS2_DIMMB#

MCH_CLKSEL1

MCH_CLKSEL2

CFG11

CFG9

CFG7

CFG10

CFG6

CFG14

CFG16

CFG15

CFG17

CFG8

CFG5

CFG13

CFG18

CFG19

CFG12

CFG20

H_DPRSTP#

THERMTRIP#

PM_PWROK

PM_EXTTS#1

PM_EXTTS#0

PM_BMBUSY#

DPRSLPVR

SMRCOMP_VOH

PLT_RST#

PM_EXTTS#1

TSATN#

TP_SM_DRAMRST#

V_DDR_MCH_REF15,16

H_D#[0..63]7

H_CPUSLP#7

H_RESET#6

H_A#[3..35] 6

H_ADS# 6

H_ADSTB#1 6

H_ADSTB#0 6

H_BPRI# 6

H_BNR# 6

H_DEFER# 6

H_BR0# 6

H_DBSY# 6

CLK_MCH_BCLK 17

CLK_MCH_BCLK# 17

H_DPWR# 7

H_DRDY# 6

H_HIT# 6

H_HITM# 6

H_LOCK# 6

H_TRDY# 6

H_DINV#0 7

H_DINV#1 7

H_DINV#2 7

H_DINV#3 7

H_DSTBN#0 7

H_DSTBN#1 7

H_DSTBN#2 7

H_DSTBN#3 7

H_DSTBP#0 7

H_DSTBP#1 7

H_DSTBP#2 7

H_DSTBP#3 7

H_REQ#3 6

H_REQ#2 6

H_REQ#1 6

H_REQ#4 6

H_REQ#0 6

H_RS#2 6

H_RS#1 6

H_RS#0 6

MCH_CLKSEL017

MCH_CLKSEL117

MCH_CLKSEL217

TSATN# 37

MCH_ICH_SYNC# 27

CL_CLK0 27

CL_DATA0 27

M_PWROK 27,37

CL_RST# 27

DMI_TXP0 27

DMI_RXN0 27

DMI_RXP0 27

DMI_TXN0 27

DMI_TXN1 27

DMI_TXN2 27

DMI_TXN3 27

DMI_TXP1 27

DMI_TXP2 27

DMI_TXP3 27

DMI_RXN1 27

DMI_RXN2 27

DMI_RXN3 27

DMI_RXP1 27

DMI_RXP2 27

DMI_RXP3 27

CLK_MCH_3GPLL 17

CLK_MCH_3GPLL# 17

DDR_CKE0_DIMMA 15

DDR_CKE1_DIMMA 15

DDR_CKE2_DIMMB 16

DDR_CKE3_DIMMB 16

DDR_CS0_DIMMA# 15

DDR_CS1_DIMMA# 15

DDR_CS2_DIMMB# 16

DDR_CS3_DIMMB# 16

M_CLK_DDR0 15

M_CLK_DDR1 15

M_CLK_DDR2 16

M_CLK_DDR3 16

M_CLK_DDR#0 15

M_CLK_DDR#1 15

M_CLK_DDR#2 16

M_CLK_DDR#3 16

M_ODT0 15

M_ODT1 15

M_ODT2 16

M_ODT3 16

CLKREQ#_7 17

CFG511

CFG911

CFG1111

CFG1011

CFG611

CFG711

CFG1311

CFG1211

CFG1611

CFG1811

CFG2011

CFG1911

CFG811

CFG1411

CFG1511

CFG1711

PM_BMBUSY#27

H_DPRSTP#7,26,46

PM_EXTTS#015

DPRSLPVR27,46

PM_EXTTS#116

PM_PWROK27,37

H_THERMTRIP#6,26

PLT_RST#20,25,30,31

+VCCP

+VCCP

+3VS

+1.8V

+1.8V

+VCCP

+1.8V

+VCCP

Title

Size Document Number Rev

Date: Sheet

of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-4731P Rhett discrete

0.1

Cantiga(1/6)-AGTL/DMI/DDR

Custom

9 51Monday, February 16, 2009

2008/11/04 2008/11/04

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet

of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-4731P Rhett discrete

0.1

Cantiga(1/6)-AGTL/DMI/DDR

Custom

9 51Monday, February 16, 2009

2008/11/04 2008/11/04

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet

of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-4731P Rhett discrete

0.1

Cantiga(1/6)-AGTL/DMI/DDR

Custom

9 51Monday, February 16, 2009

2008/11/04 2008/11/04

Compal Electronics, Inc.

Layout Note:

H_RCOMP / H_VREF / H_SWNG

trace width and spacing is 10/20

Layout Note: V_DDR_MCH_REF

trace width and spacing is 20/20.

Near B3 pinwithin 100 mils from NB

Layout note:

Route H_SCOMP and H_SCOMP# with trace

width, spacing and impedance (55 ohm) same as

FSB data traces

0621 add CLK and DAT for DVI

Follow Design Guide

For Cantiga: 80.6ohm

80% of 1.8V VCC_SM

20% of 1.8V VCC_SM

R44

499_0402_1%

R44

499_0402_1%

12

T15T15

T28T28

T19T19

C53

2.2U_0603_6.3V4Z

C53

2.2U_0603_6.3V4Z

1

2

T31T31

T18T18

T38T38

T7T7

C57

0.1U_0402_16V4Z

C57

0.1U_0402_16V4Z

1

2

T17T17

T25T25

T22T22

T39T39

R52

2K_0402_1%

R52

2K_0402_1%

12

T27T27

T24T24

C54

0.01U_0402_25V7K

C54

0.01U_0402_25V7K

1

2

R37 499_0402_1%R37 499_0402_1%

1 2

T21T21

T40T40

R36 0_0402_5%R36 0_0402_5%

1 2

C58

0.1U_0402_16V4Z

C58

0.1U_0402_16V4Z

1

2

R33

1K_0402_1%

R33

1K_0402_1%

12

T9T9

R45

10K_0402_1%

R45

10K_0402_1%

12

R41

100_0402_5%

R41

100_0402_5%

1 2

R40 10K_0402_5%R40 10K_0402_5%

1 2

R55

100_0402_1%

R55

100_0402_1%

12

C59

0.1U_0402_16V4Z

C59

0.1U_0402_16V4Z

1

2

R38 10K_0402_5%

R38 10K_0402_5%

1 2

T13T13

R42

0_0402_5%

R42

0_0402_5%

1 2

R35 80.6_0402_1%R35 80.6_0402_1%

1 2

T26T26

HOST

U2A

CANTIGA ES_FCBGA1329

HOST

U2A

CANTIGA ES_FCBGA1329

H_A#_10

P16

H_A#_11

R16

H_A#_12

N17

H_A#_13

M13

H_A#_14

E17

H_A#_15

P17

H_A#_16

F17

H_A#_17

G20

H_A#_18

B19

H_A#_19

J16

H_A#_20

E20

H_A#_21

H16

H_A#_22

J20

H_A#_23

L17

H_A#_24

A17

H_A#_25

B17

H_A#_26

L16

H_A#_27

C21

H_A#_28

J17

H_A#_29

H20

H_A#_3

A14

H_A#_30

B18

H_A#_31

K17

H_A#_4

C15

H_A#_5

F16

H_A#_6

H13

H_A#_7

C18

H_A#_8

M16

H_A#_9

J13

H_ADS#

H12

H_ADSTB#_0

B16

H_ADSTB#_1

G17

H_BNR#

A9

H_BPRI#

F11

H_BREQ#

G12

HPLL_CLK#

AH6

H_CPURST#

C12

HPLL_CLK

AH7

H_D#_0

F2

H_REQ#_2

F13

H_REQ#_3

B13

H_D#_1

G8

H_D#_10

M9

H_D#_20

L6

H_D#_30

N10

H_D#_40

AA8

H_D#_50

AA2

H_D#_60

AE11

H_D#_8

D4

H_D#_9

H3

H_DBSY#

B10

H_D#_11

M11

H_D#_12

J1

H_D#_13

J2

H_D#_14

N12

H_D#_15

J6

H_D#_16

P2

H_D#_17

L2

H_D#_18

R2

H_D#_19

N9

H_D#_2

F8

H_D#_21

M5

H_D#_22

J3

H_D#_23

N2

H_D#_24

R1

H_D#_25

N5

H_D#_26

N6

H_D#_27

P13

H_D#_28

N8

H_D#_29

L7

H_D#_3

E6

H_D#_31

M3

H_D#_32

Y3

H_D#_33

AD14

H_D#_34

Y6

H_D#_35

Y10

H_D#_36

Y12

H_D#_37

Y14

H_D#_38

Y7

H_D#_39

W2

H_D#_4

G2

H_D#_41

Y9

H_D#_42

AA13

H_D#_43

AA9

H_D#_44

AA11

H_D#_45

AD11

H_D#_46

AD10

H_D#_47

AD13

H_D#_48

AE12

H_D#_49

AE9

H_D#_5

H6

H_D#_51

AD8

H_D#_52

AA3

H_D#_53

AD3

H_D#_54

AD7

H_D#_55

AE14

H_D#_56

AF3

H_D#_57

AC1

H_D#_58

AE3

H_D#_59

AC3

H_D#_6

H2

H_D#_61

AE8

H_D#_62

AG2

H_D#_63

AD6

H_D#_7

F6

H_DEFER#

E9

H_DINV#_0

J8

H_DINV#_1

L3

H_DINV#_2

Y13

H_DINV#_3

Y1

H_DPWR#

J11

H_DRDY#

F9

H_DSTBN#_0

L10

H_DSTBN#_1

M7

H_DSTBN#_2

AA5

H_DSTBN#_3

AE6

H_DSTBP#_0

L9

H_DSTBP#_1

M8

H_DSTBP#_2

AA6

H_DSTBP#_3

AE5

H_AVREF

A11

H_DVREF

B11

H_TRDY#

C9

H_HIT#

H9

H_HITM#

E12

H_LOCK#

H11

H_REQ#_0

B15

H_REQ#_1

K13

H_REQ#_4

B14

H_A#_32

B20

H_A#_33

F21

H_A#_34

K21

H_A#_35

L20

H_SWING

C5

H_CPUSLP#

E11

H_RCOMP

E3

H_RS#_0

B6

H_RS#_1

F12

H_RS#_2

C8

R49

56_0402_5%

R49

56_0402_5%

1 2

T37T37

PM

MISC

NC

DDR CLK/ CONTROL/COMPENSATION

CLK

DMI

CFG

RSVD

GRAPHICS VID

MEHDA

U2B

CANTIGA ES_FCBGA1329

PM

MISC

NC

DDR CLK/ CONTROL/COMPENSATION

CLK

DMI

CFG

RSVD

GRAPHICS VID

MEHDA

U2B

CANTIGA ES_FCBGA1329

SA_CK_0

AP24

SA_CK_1

AT21

SB_CK_0

AV24

SA_CK#_0

AR24

SA_CK#_1

AR21

SB_CK#_0

AU24

SA_CKE_0

BC28

SA_CKE_1

AY28

SB_CKE_0

AY36

SB_CKE_1

BB36

SA_CS#_0

BA17

SA_CS#_1

AY16

SB_CS#_0

AV16

SB_CS#_1

AR13

SM_DRAMRST#

BC36

SA_ODT_0

BD17

SA_ODT_1

AY17

SB_ODT_0

BF15

SB_ODT_1

AY13

SM_RCOMP

BG22

SM_RCOMP#

BH21

CFG_18

P29

CFG_19

R28

CFG_2

P25

CFG_0

T25

CFG_1

R25

CFG_20

T28

CFG_3

P20

CFG_4

P24

CFG_5

C25

CFG_6

N24

CFG_7

M24

CFG_8

E21

CFG_9

C23

CFG_10

C24

CFG_11

N21

CFG_12

P21

CFG_13

T21

CFG_14

R20

CFG_15

M20

CFG_16

L21

CFG_17

H21

PM_SYNC#

R29

PM_EXT_TS#_0

N33

PM_EXT_TS#_1

P32

PWROK

AT40

RSTIN#

AT11

DPLL_REF_CLK

B38

DPLL_REF_CLK#

A38

DPLL_REF_SSCLK

E41

DPLL_REF_SSCLK#

F41

DMI_RXN_0

AE41

DMI_RXN_1

AE37

DMI_RXN_2

AE47

DMI_RXN_3

AH39

DMI_RXP_0

AE40

DMI_RXP_1

AE38

DMI_RXP_2

AE48

DMI_RXP_3

AH40

DMI_TXN_0

AE35

DMI_TXN_1

AE43

DMI_TXN_2

AE46

DMI_TXN_3

AH42

DMI_TXP_0

AD35

DMI_TXP_1

AE44

DMI_TXP_2

AF46

DMI_TXP_3

AH43

RESERVED

AL34

RESERVED

AN35

RESERVED

AK34

RESERVED

AM35

RESERVED

BG23

RESERVED

BF23

RESERVED

BH18

RESERVED

BF18

PM_DPRSTP#

B7

SB_CK_1

AU20

SB_CK#_1

AV20

RESERVED

AY21

RESERVED

AH9

RESERVED

AH10

RESERVED

AH12

RESERVED

AH13

RESERVED

M36

RESERVED

N36

RESERVED

R33

RESERVED

T33

GFX_VID_0

B33

GFX_VID_1

B32

GFX_VID_2

G33

GFX_VID_3

F33

GFX_VR_EN

C34

SM_RCOMP_VOH

BF28

SM_RCOMP_VOL

BH28

THERMTRIP#

T20

DPRSLPVR

R32

RESERVED

K12

CL_CLK

AH37

CL_DATA

AH36

CL_PWROK

AN36

CL_RST#

AJ35

CL_VREF

AH34

NC

A47

NC

BG48

NC

BF48

NC

BD48

NC

BC48

NC

BH47

NC

BG47

NC

BE47

NC

BH46

NC

BF46

NC

BG45

NC

BH44

NC

BH43

NC

BH6

NC

BH5

NC

BG4

SDVO_CTRLCLK

G36

SDVO_CTRLDATA

E36

CLKREQ#

K36

RESERVED

T24

ICH_SYNC#

H36

TSATN#

B12

PEG_CLK#

E43

PEG_CLK

F43

NC

BH3

GFX_VID_4

E33

RESERVED

B31

DDPC_CTRLCLK

N28

NC

BF3

NC

BH2

NC

BG2

NC

BE2

NC

BG1

NC

BF1

NC

BD1

NC

BC1

NC

F1

SM_VREF

AV42

SM_PWROK

AR36

SM_REXT

BF17

RESERVED

M1

HDA_BCLK

B28

HDA_RST#

B30

HDA_SDI

B29

HDA_SDO

C29

HDA_SYNC

A28

DDPC_CTRLDATA

M28

RESERVED

B2

T33T33

T29T29

T14T14

R32

3.01K_0402_1%

R32

3.01K_0402_1%

12

T10T10

R54

24.9_0402_1%

R54

24.9_0402_1%

12

C56

0.1U_0402_16V4Z

C56

0.1U_0402_16V4Z

1

2

T16T16

R39 10K_0402_5%R39 10K_0402_5%

1 2

T23T23

C51

2.2U_0603_6.3V4Z

C51

2.2U_0603_6.3V4Z

1

2

T20T20

R31

1K_0402_1%

R31

1K_0402_1%

12

T35T35

T36T36

C52

0.01U_0402_25V7K

C52

0.01U_0402_25V7K

1

2

T8T8

C55

0.1U_0402_16V4Z

@

C55

0.1U_0402_16V4Z

@

1

2

T34T34

T11T11

R43

1K_0402_1%

R43

1K_0402_1%

12

T32T32

R47

221_0603_1%

R47

221_0603_1%

12

R48

10K_0402_1%

R48

10K_0402_1%

12

T12T12

R46

1K_0402_1%

R46

1K_0402_1%

12

T30T30

R34 80.6_0402_1%

R34 80.6_0402_1%

1 2

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

DDR_A_MA0

DDR_A_MA1

DDR_A_MA4

DDR_A_MA2

DDR_A_MA3

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA12

DDR_A_MA13

DDR_A_MA11

DDR_A_MA10

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#3

DDR_A_DQS#2

DDR_A_DQS#5

DDR_A_DQS#4

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DM7

DDR_A_DM5

DDR_A_DM2

DDR_A_DM1

DDR_A_DM6

DDR_A_DM4

DDR_A_DM0

DDR_A_DM3

DDR_A_CAS#

DDR_A_RAS#

DDR_A_WE#

DDR_A_D63

DDR_A_D62

DDR_A_D61

DDR_A_D60

DDR_A_D59

DDR_A_D58

DDR_A_D57

DDR_A_D56

DDR_A_D55

DDR_A_D54

DDR_A_D51

DDR_A_D50

DDR_A_D49

DDR_A_D48

DDR_A_D53

DDR_A_D52

DDR_A_D47

DDR_A_D46

DDR_A_D43

DDR_A_D42

DDR_A_D41

DDR_A_D40

DDR_A_D45

DDR_A_D44

DDR_A_D39

DDR_A_D38

DDR_A_D35

DDR_A_D34

DDR_A_D33

DDR_A_D32

DDR_A_D37

DDR_A_D36

DDR_A_D31

DDR_A_D30

DDR_A_D27

DDR_A_D26

DDR_A_D25

DDR_A_D24

DDR_A_D15

DDR_A_D14

DDR_A_D11

DDR_A_D10

DDR_A_D9

DDR_A_D13

DDR_A_D12

DDR_A_D29

DDR_A_D28

DDR_A_D23

DDR_A_D22

DDR_A_D19

DDR_A_D18

DDR_A_D17

DDR_A_D16

DDR_A_D21

DDR_A_D20

DDR_A_D8

DDR_A_D5

DDR_A_D4

DDR_A_D3

DDR_A_D7

DDR_A_D6

DDR_A_D2

DDR_A_D1

DDR_A_D0

DDR_A_MA14

DDR_B_RAS#

DDR_B_MA14

DDR_B_MA10

DDR_B_DQS#7

DDR_B_DQS#2

DDR_B_DQS7

DDR_B_DQS2

DDR_B_DM3

DDR_B_D51

DDR_B_D39

DDR_B_D18

DDR_B_MA7

DDR_B_DQS0

DDR_B_D7

DDR_B_D54

DDR_B_D4

DDR_B_D36

DDR_B_D21

DDR_B_MA4

DDR_B_DM0

DDR_B_D62

DDR_B_D34

DDR_B_D19

DDR_B_D13

DDR_B_MA5

DDR_B_MA11

DDR_B_BS2

DDR_B_D42

DDR_B_D35

DDR_B_D31

DDR_B_D24

DDR_B_D15

DDR_B_MA3

DDR_B_DQS#6

DDR_B_DM7

DDR_B_D50

DDR_B_D38

DDR_B_D32

DDR_B_D23

DDR_B_MA6

DDR_B_D6

DDR_B_D53

DDR_B_D33

DDR_B_D3

DDR_B_D20

DDR_B_DQS#5

DDR_B_BS1

DDR_B_D61

DDR_B_D59

DDR_B_D46

DDR_B_D12

DDR_B_DQS3

DDR_B_D47

DDR_B_D30

DDR_B_D14

DDR_B_MA0

DDR_B_DQS#0

DDR_B_DM6

DDR_B_DM4

DDR_B_D55

DDR_B_D44

DDR_B_D29

DDR_B_D27

DDR_B_D22

DDR_B_MA13

DDR_B_MA1

DDR_B_D57

DDR_B_D52

DDR_B_D2

DDR_B_D17

DDR_B_DQS#1

DDR_B_DQS1

DDR_B_D9

DDR_B_D60

DDR_B_D58

DDR_B_D45

DDR_B_DQS4

DDR_B_MA9

DDR_B_DQS#4

DDR_B_DM5

DDR_B_DM2

DDR_B_D49

DDR_B_D41

DDR_B_D28

DDR_B_D11

DDR_B_WE#

DDR_B_MA12

DDR_B_D56

DDR_B_D48

DDR_B_D16

DDR_B_D1

DDR_B_MA2

DDR_B_DQS5

DDR_B_D8

DDR_B_D63

DDR_B_D37

DDR_B_D0

DDR_B_BS0

DDR_B_D5

DDR_B_MA8

DDR_B_DQS#3

DDR_B_DQS6

DDR_B_DM1

DDR_B_CAS#

DDR_B_D43

DDR_B_D40

DDR_B_D26

DDR_B_D25

DDR_B_D10

DDR_A_BS0 15

DDR_A_BS1 15

DDR_A_BS2 15

DDR_A_D[0..63]15

DDR_A_MA[0..14] 15

DDR_A_DQS#[0..7] 15

DDR_A_DQS[0..7] 15

DDR_A_DM[0..7] 15

DDR_A_CAS# 15

DDR_A_RAS# 15

DDR_A_WE# 15

DDR_B_D[0..63]16

DDR_B_BS0 16

DDR_B_BS1 16

DDR_B_BS2 16

DDR_B_CAS# 16

DDR_B_RAS# 16

DDR_B_WE# 16

DDR_B_DM[0..7] 16

DDR_B_DQS[0..7] 16

DDR_B_DQS#[0..7] 16

DDR_B_MA[0..14] 16

Title

Size Document Number Rev

Date: Sheet

of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-4731P Rhett discrete

0.1

Cantiga(2/6)-DDR2 A/B CH

Custom

10 51Monday, February 16, 2009

2008/11/04 2008/11/04

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet

of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-4731P Rhett discrete

0.1

Cantiga(2/6)-DDR2 A/B CH

Custom

10 51Monday, February 16, 2009

2008/11/04 2008/11/04

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet

of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-4731P Rhett discrete

0.1

Cantiga(2/6)-DDR2 A/B CH

Custom

10 51Monday, February 16, 2009

2008/11/04 2008/11/04

Compal Electronics, Inc.

DDR SYSTEM MEMORY A

U2D

CANTIGA ES_FCBGA1329

DDR SYSTEM MEMORY A

U2D

CANTIGA ES_FCBGA1329

SA_DQ_0

AJ38

SA_DQ_1

AJ41

SA_DQ_10

AU40

SA_DQ_11

AT38

SA_DQ_12

AN41

SA_DQ_13

AN39

SA_DQ_14

AU44

SA_DQ_15

AU42

SA_DQ_16

AV39

SA_DQ_17

AY44

SA_DQ_18

BA40

SA_DQ_19

BD43

SA_DQ_2

AN38

SA_DQ_20

AV41

SA_DQ_21

AY43

SA_DQ_22

BB41

SA_DQ_23

BC40

SA_DQ_24

AY37

SA_DQ_25

BD38

SA_DQ_26

AV37

SA_DQ_27

AT36

SA_DQ_28

AY38

SA_DQ_29

BB38

SA_DQ_3

AM38

SA_DQ_30

AV36

SA_DQ_31

AW36

SA_DQ_32

BD13

SA_DQ_33

AU11

SA_DQ_34

BC11

SA_DQ_35

BA12

SA_DQ_36

AU13

SA_DQ_37

AV13

SA_DQ_38

BD12

SA_DQ_39

BC12

SA_DQ_4

AJ36

SA_DQ_40

BB9

SA_DQ_41

BA9

SA_DQ_42

AU10

SA_DQ_43

AV9

SA_DQ_44

BA11

SA_DQ_45

BD9

SA_DQ_46

AY8

SA_DQ_47

BA6

SA_DQ_48

AV5

SA_DQ_49

AV7

SA_DQ_5

AJ40

SA_DQ_50

AT9

SA_DQ_51

AN8

SA_DQ_52

AU5

SA_DQ_53

AU6

SA_DQ_54

AT5

SA_DQ_55

AN10

SA_DQ_56

AM11

SA_DQ_57

AM5

SA_DQ_58

AJ9

SA_DQ_59

AJ8

SA_DQ_6

AM44

SA_DQ_60

AN12

SA_DQ_61

AM13

SA_DQ_62

AJ11

SA_DQ_63

AJ12

SA_DQ_7

AM42

SA_DQ_8

AN43

SA_DQ_9

AN44

SA_BS_0

BD21

SA_BS_1

BG18

SA_BS_2

AT25

SA_CAS#

BD20

SA_DM_0

AM37

SA_DM_1

AT41

SA_DM_2

AY41

SA_DM_3

AU39

SA_DM_4

BB12

SA_DM_5

AY6

SA_DM_6

AT7

SA_DQS_0

AJ44

SA_DQS_1

AT44

SA_DQS_2

BA43

SA_DQS_3

BC37

SA_DQS_4

AW12

SA_DQS_5

BC8

SA_DQS_6

AU8

SA_DQS_7

AM7

SA_DM_7

AJ5

SA_DQS#_0

AJ43

SA_DQS#_1

AT43

SA_DQS#_2

BA44

SA_DQS#_3

BD37

SA_DQS#_4

AY12

SA_DQS#_5

BD8

SA_DQS#_6

AU9

SA_DQS#_7

AM8

SA_MA_0

BA21

SA_MA_1

BC24

SA_MA_10

BC21

SA_MA_11

BG26

SA_MA_12

BH26

SA_MA_13

BH17

SA_MA_2

BG24

SA_MA_3

BH24

SA_MA_4

BG25

SA_MA_5

BA24

SA_MA_6

BD24

SA_MA_7

BG27

SA_MA_8

BF25

SA_MA_9

AW24

SA_RAS#

BB20

SA_WE#

AY20

SA_MA_14

AY25

DDR SYSTEM MEMORY B

U2E

CANTIGA ES_FCBGA1329

DDR SYSTEM MEMORY B

U2E

CANTIGA ES_FCBGA1329

SB_DQ_0

AK47

SB_DQ_1

AH46

SB_DQ_10

BA48

SB_DQ_11

AY48

SB_DQ_12

AT47

SB_DQ_13

AR47

SB_DQ_14

BA47

SB_DQ_15

BC47

SB_DQ_16

BC46

SB_DQ_17

BC44

SB_DQ_18

BG43

SB_DQ_19

BF43

SB_DQ_2

AP47

SB_DQ_20

BE45

SB_DQ_21

BC41

SB_DQ_22

BF40

SB_DQ_23

BF41

SB_DQ_24

BG38

SB_DQ_25

BF38

SB_DQ_26

BH35

SB_DQ_27

BG35

SB_DQ_28

BH40

SB_DQ_29

BG39

SB_DQ_3

AP46

SB_DQ_30

BG34

SB_DQ_31

BH34

SB_DQ_32

BH14

SB_DQ_33

BG12

SB_DQ_34

BH11

SB_DQ_35

BG8

SB_DQ_36

BH12

SB_DQ_37

BF11

SB_DQ_38

BF8

SB_DQ_39

BG7

SB_DQ_4

AJ46

SB_DQ_40

BC5

SB_DQ_41

BC6

SB_DQ_42

AY3

SB_DQ_43

AY1

SB_DQ_44

BF6

SB_DQ_45

BF5

SB_DQ_46

BA1

SB_DQ_47

BD3

SB_DQ_48

AV2

SB_DQ_49

AU3

SB_DQ_5

AJ48

SB_DQ_50

AR3

SB_DQ_51

AN2

SB_DQ_52

AY2

SB_DQ_53

AV1

SB_DQ_54

AP3

SB_DQ_55

AR1

SB_DQ_56

AL1

SB_DQ_57

AL2

SB_DQ_58

AJ1

SB_DQ_59

AH1

SB_DQ_6

AM48

SB_DQ_60

AM2

SB_DQ_61

AM3

SB_DQ_62

AH3

SB_DQ_63

AJ3

SB_DQ_7

AP48

SB_DQ_8

AU47

SB_DQ_9

AU46

SB_BS_0

BC16

SB_BS_1

BB17

SB_BS_2

BB33

SB_CAS#

BG16

SB_DM_0

AM47

SB_DM_1

AY47

SB_DM_2

BD40

SB_DM_3

BF35

SB_DM_4

BG11

SB_DM_5

BA3

SB_DM_6

AP1

SB_DM_7

AK2

SB_DQS_0

AL47

SB_DQS_1

AV48

SB_DQS_2

BG41

SB_DQS_3

BG37

SB_DQS_4

BH9

SB_DQS_5

BB2

SB_DQS_6

AU1

SB_DQS_7

AN6

SB_DQS#_0

AL46

SB_DQS#_1

AV47

SB_DQS#_2

BH41

SB_DQS#_3

BH37

SB_DQS#_4

BG9

SB_DQS#_5

BC2

SB_DQS#_6

AT2

SB_DQS#_7

AN5

SB_MA_0

AV17

SB_MA_1

BA25

SB_MA_10

BB16

SB_MA_11

AW33

SB_MA_12

AY33

SB_MA_13

BH15

SB_MA_2

BC25

SB_MA_3

AU25

SB_MA_4

AW25

SB_MA_5

BB28

SB_MA_6

AU28

SB_MA_7

AW28

SB_MA_8

AT33

SB_MA_9

BD33

SB_MA_14

AU33

SB_RAS#

AU17

SB_WE#

BF14

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

CFG5

PEG_RXN4

PEG_TXN5

PEG_RXN7

PEG_RXN6

PEG_RXN5

PEG_TXN7

PEG_RXP4

PEG_RXP7

PEG_RXP6

PEG_RXP5

PEG_RXP14

PEG_RXP12

PEG_RXP3

PEG_RXP2

PEG_RXP0

PEG_RXP13

PEG_RXP15

PEG_RXP10

PEG_RXP8

PEG_RXP1

PEG_RXP9

PEG_RXP11

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TXN12

PEG_RXN0

PEG_RXN12

PEG_RXN3

PEG_RXN2

PEG_RXN10

PEG_RXN8

PEG_RXN13

PEG_RXN15

PEG_RXN14

PEG_TXN9

PEG_RXN9

PEG_RXN11

PEG_TXN6

PEG_TXN10

PEG_TXN11

PEG_TXN8

PEG_TXP13

PEG_TXP7

PEG_TXN4

PEG_TXP5

PEG_TXP6

PEG_TXP12

PEG_TXP14

PEG_TXP15

PEG_TXP11

PEG_TXP9

PEG_TXP8

PEG_TXP10

PEG_TXP4

PEG_TXP1

PEG_TXP0

PEG_TXP2

PEG_TXN0

PEG_TXP3

PEG_TXN1

PEG_RXN1

PEG_TXN3

PEG_TXN2

CFG59

CFG69

CFG79

CFG89

CFG99

CFG109

CFG119

CFG129

CFG139

CFG149

CFG159

CFG179

CFG189

CFG169

CFG199

CFG209

PEG_M_TXN3 20

PEG_M_TXN2 20

PEG_M_TXN1 20

PEG_M_TXN0 20

PEG_M_TXP2 20

PEG_M_TXP3 20

PEG_M_TXP1 20

PEG_M_TXP0 20

PEG_RXN3 20

PEG_RXN2 20

PEG_RXN1 20

PEG_RXN0 20

PEG_RXN5 20

PEG_RXN7 20

PEG_RXN6 20

PEG_RXN4 20

PEG_RXN13 20

PEG_RXN15 20

PEG_RXN14 20

PEG_RXN12 20

PEG_RXN9 20

PEG_RXN11 20

PEG_RXN10 20

PEG_RXN8 20

PEG_RXP5 20

PEG_RXP7 20

PEG_RXP6 20

PEG_RXP4 20

PEG_RXP12 20

PEG_RXP3 20

PEG_RXP2 20

PEG_RXP0 20

PEG_RXP8 20

PEG_RXP13 20

PEG_RXP15 20

PEG_RXP14 20

PEG_RXP1 20

PEG_RXP9 20

PEG_RXP11 20

PEG_RXP10 20

PEG_M_TXN7 20

PEG_M_TXN6 20

PEG_M_TXN5 20

PEG_M_TXN4 20

PEG_M_TXN10 20

PEG_M_TXN9 20

PEG_M_TXN8 20

PEG_M_TXN14 20

PEG_M_TXN13 20

PEG_M_TXN12 20

PEG_M_TXN11 20

PEG_M_TXP6 20

PEG_M_TXP5 20

PEG_M_TXP4 20

PEG_M_TXN15 20

PEG_M_TXP10 20

PEG_M_TXP9 20

PEG_M_TXP8 20

PEG_M_TXP7 20

PEG_M_TXP13 20

PEG_M_TXP12 20

PEG_M_TXP11 20

PEG_M_TXP15 20

PEG_M_TXP14 20

+VCC_PEG

+3VS

+3VS

Title

Size Document Number Rev

Date: Sheet

of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-4731P Rhett discrete

0.1

Cantiga(3/6)-VGA/LVDS/TV

Custom

11 51Monday, February 16, 2009

2008/11/04 2008/11/04

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet

of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-4731P Rhett discrete

0.1

Cantiga(3/6)-VGA/LVDS/TV

Custom

11 51Monday, February 16, 2009

2008/11/04 2008/11/04

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet

of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

LA-4731P Rhett discrete

0.1

Cantiga(3/6)-VGA/LVDS/TV

Custom

11 51Monday, February 16, 2009

2008/11/04 2008/11/04

Compal Electronics, Inc.

PEGCOMP trace width

and spacing is 20/25 mils.

000 = FSB 1066MHz

CFG[4:3]

Reserved

CFG6

0 = The iTPM Host Interface is enable

1 = The iTPM Host Interface is disable

*

Reserved

CFG10

(Default)11 = Normal Operation

10 = All Z Mode Enabled

00 = Reserved

01 = XOR Mode Enabled

*

0 = Enable

1 = Disable

*

CFG9 (PCIE Graphics

Lane Reversal)

CFG[2:0] FSB Freq

select

Reserved

Reserved

CFG[15:14]

Strap Pin Table

Reserved

CFG[18:17]

(Lane number in Order)

Others = Reserved

011 = FSB 667MHz

010 = FSB 800MHz

*

1 = Reverse Lane

0 = Reverse Lane,15->0, 14->1

1 = Enabled

0 = Normal Operation

0 = Disabled

*

0 = DMI x 2

*

*

*

1 = PCIE/SDVO are operating simu.

0 = Only PCIE or SDVO is operational.

*

1 = Normal Operation,Lane Number in

order

1 = DMI x 4

0 =(TLS)chiper suite with no confidentiality

1 =(TLS)chiper suite with confidentiality

CFG5 (DMI select)

CFG19 (DMI Lane Reversal)

CFG16 (FSB Dynamic ODT)

CFG7

CFG20

CFG11

CFG[13:12] (XOR/ALLZ)

CFG8

(Intel Management

Engine Crypto strap)

(PCIE

Lookback

enable)

(PCIE/SDVO

concurrent)

R83

2.21K_0402_1%

@R83

2.21K_0402_1%

@

1 2

C1308 0.1U_0402_16V4ZC1308 0.1U_0402_16V4Z

1 2

LVDS

PCI-EXPRESS GRAPHICS

TV VGA

U2C

CANTIGA ES_FCBGA1329

LVDS

PCI-EXPRESS GRAPHICS

TV VGA

U2C

CANTIGA ES_FCBGA1329

PEG_COMPI

T37

PEG_COMPO

T36

PEG_RX#_0

H44

PEG_RX#_1

J46

PEG_RX#_2

L44

PEG_RX#_3

L40

PEG_RX#_4

N41

PEG_RX#_5

P48

PEG_RX#_6

N44

PEG_RX#_7

T43

PEG_RX#_8

U43

PEG_RX#_9

Y43

PEG_RX#_10

Y48

PEG_RX#_11

Y36

PEG_RX#_12

AA43

PEG_RX#_13

AD37

PEG_RX#_14

AC47

PEG_RX#_15

AD39

PEG_RX_0

H43

PEG_RX_1

J44

PEG_RX_2

L43

PEG_RX_3

L41

PEG_RX_4

N40

PEG_RX_5

P47

PEG_RX_6

N43

PEG_RX_7

T42

PEG_RX_8

U42

PEG_RX_9

Y42

PEG_RX_10

W47

PEG_RX_11

Y37

PEG_RX_12

AA42

PEG_RX_13

AD36

PEG_RX_14

AC48

PEG_RX_15

AD40

PEG_TX#_0

J41

PEG_TX#_10

Y40

PEG_TX#_3

M40

PEG_TX#_4

M42

PEG_TX#_5

R48

PEG_TX#_6

N38

PEG_TX#_7

T40

PEG_TX#_8

U37

PEG_TX#_9

U40

PEG_TX#_1

M46

PEG_TX#_11

AA46

PEG_TX#_12

AA37

PEG_TX#_13

AA40

PEG_TX#_14

AD43

PEG_TX#_15

AC46

PEG_TX#_2

M47

PEG_TX_0

J42

PEG_TX_1

L46

PEG_TX_2

M48

PEG_TX_3

M39

PEG_TX_4

M43

PEG_TX_5

R47

PEG_TX_6

N37

PEG_TX_7

T39

PEG_TX_8

U36

PEG_TX_9

U39

PEG_TX_10

Y39

PEG_TX_11

Y46

PEG_TX_12

AA36

PEG_TX_13

AA39

PEG_TX_14

AD42

PEG_TX_15

AD46

L_CTRL_CLK

M32

L_CTRL_DATA

M33

L_DDC_CLK

K33

L_DDC_DATA

J33

L_VDD_EN

M29

LVDS_IBG

C44

LVDS_VBG

B43

LVDS_VREFH

E37

LVDS_VREFL

E38

LVDSA_CLK#

C41

LVDSA_CLK

C40

LVDSA_DATA#_0

H47

LVDSA_DATA#_1

E46

LVDSA_DATA#_2

G40

LVDSA_DATA_1

D45

LVDSA_DATA_2

F40

LVDSB_CLK#

B37

LVDSB_CLK

A37

LVDSB_DATA#_0

A41

LVDSB_DATA#_1

H38

LVDSB_DATA#_2

G37

LVDSB_DATA_1

G38

LVDSB_DATA_2

F37

L_BKLT_EN

G32

TVA_DAC

F25

TVB_DAC

H25

TVC_DAC

K25

TV_RTN

H24

CRT_BLUE

E28

CRT_DDC_CLK

H32

CRT_DDC_DATA

J32

CRT_GREEN

G28

CRT_HSYNC

J29

CRT_TVO_IREF

E29

CRT_RED

J28

CRT_IRTN

G29

CRT_VSYNC

L29

LVDSA_DATA_0

H48

LVDSB_DATA_0

B42

L_BKLT_CTRL

L32

TV_DCONSEL_0

C31

TV_DCONSEL_1

E32

LVDSA_DATA#_3

A40

LVDSA_DATA_3

B40

LVDSB_DATA#_3

J37

LVDSB_DATA_3

K37

C1319 0.1U_0402_16V4ZC1319 0.1U_0402_16V4Z

1 2

C1316 0.1U_0402_16V4ZC1316 0.1U_0402_16V4Z

1 2

C1298 0.1U_0402_16V4ZC1298 0.1U_0402_16V4Z

1 2

R82

2.21K_0402_1%

@R82

2.21K_0402_1%

@

1 2

C1315 0.1U_0402_16V4ZC1315 0.1U_0402_16V4Z

1 2

C1293 0.1U_0402_16V4ZC1293 0.1U_0402_16V4Z

1 2

R57

49.9_0402_1%

R57

49.9_0402_1%

1 2

C1290 0.1U_0402_16V4ZC1290 0.1U_0402_16V4Z

1 2

C1307 0.1U_0402_16V4ZC1307 0.1U_0402_16V4Z

1 2

R85

2.21K_0402_1%

@R85

2.21K_0402_1%

@

1 2

C1305 0.1U_0402_16V4ZC1305 0.1U_0402_16V4Z

1 2

C1297 0.1U_0402_16V4ZC1297 0.1U_0402_16V4Z

1 2

R81

2.21K_0402_1%

@ R81

2.21K_0402_1%

@

1 2

C1313 0.1U_0402_16V4ZC1313 0.1U_0402_16V4Z

1 2

C1292 0.1U_0402_16V4ZC1292 0.1U_0402_16V4Z

1 2

R78

2.21K_0402_1%

@R78

2.21K_0402_1%

@

1 2

C1311 0.1U_0402_16V4ZC1311 0.1U_0402_16V4Z

1 2

R79

2.21K_0402_1%

@R79

2.21K_0402_1%

@

1 2

C1306 0.1U_0402_16V4ZC1306 0.1U_0402_16V4Z

1 2

C1320 0.1U_0402_16V4ZC1320 0.1U_0402_16V4Z

1 2

C1300 0.1U_0402_16V4ZC1300 0.1U_0402_16V4Z

1 2

C1304 0.1U_0402_16V4ZC1304 0.1U_0402_16V4Z

1 2

C1294 0.1U_0402_16V4ZC1294 0.1U_0402_16V4Z

1 2

C1303 0.1U_0402_16V4ZC1303 0.1U_0402_16V4Z

1 2

R86

2.21K_0402_1%

@R86

2.21K_0402_1%

@

1 2

C1301 0.1U_0402_16V4ZC1301 0.1U_0402_16V4Z

1 2

C1291 0.1U_0402_16V4ZC1291 0.1U_0402_16V4Z

1 2

C1317 0.1U_0402_16V4ZC1317 0.1U_0402_16V4Z

1 2

C1312 0.1U_0402_16V4ZC1312 0.1U_0402_16V4Z

1 2

C1314 0.1U_0402_16V4ZC1314 0.1U_0402_16V4Z

1 2

R74

2.21K_0402_1%

@

R74

2.21K_0402_1%

@

12

C1310 0.1U_0402_16V4ZC1310 0.1U_0402_16V4Z

1 2

R73

4.02K_0402_1%

@ R73

4.02K_0402_1%

@

1 2

R80

2.21K_0402_1%

@R80

2.21K_0402_1%

@

1 2

C1318 0.1U_0402_16V4ZC1318 0.1U_0402_16V4Z

1 2

C1302 0.1U_0402_16V4ZC1302 0.1U_0402_16V4Z

1 2

R76

2.21K_0402_1%

@R76

2.21K_0402_1%

@

1 2

R148

0_0402_5%

@

R148

0_0402_5%

@

1 2

R75

4.02K_0402_1%

@R75

4.02K_0402_1%

@

1 2

C1296 0.1U_0402_16V4ZC1296 0.1U_0402_16V4Z

1 2

R77

2.21K_0402_1%

@R77

2.21K_0402_1%

@

1 2

R87

2.21K_0402_1%

@R87

2.21K_0402_1%

@

1 2

C1299 0.1U_0402_16V4ZC1299 0.1U_0402_16V4Z

1 2

C1289 0.1U_0402_16V4ZC1289 0.1U_0402_16V4Z

1 2

R84

2.21K_0402_1%

@R84

2.21K_0402_1%

@

1 2

R72

4.02K_0402_1%

@R72

4.02K_0402_1%

@

1 2

R71

4.02K_0402_1%

@

R71

4.02K_0402_1%

@

12

C1309 0.1U_0402_16V4ZC1309 0.1U_0402_16V4Z

1 2

C1295 0.1U_0402_16V4ZC1295 0.1U_0402_16V4Z

1 2

剩余50页未读,继续阅读

2011-07-21 上传

2022-08-29 上传

2023-12-28 上传

点击了解资源详情

2023-12-28 上传

2013-08-12 上传

cjpconglangggg

- 粉丝: 3

- 资源: 16

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 探索数据转换实验平台在设备装置中的应用

- 使用git-log-to-tikz.py将Git日志转换为TIKZ图形

- 小栗子源码2.9.3版本发布

- 使用Tinder-Hack-Client实现Tinder API交互

- Android Studio新模板:个性化Material Design导航抽屉

- React API分页模块:数据获取与页面管理

- C语言实现顺序表的动态分配方法

- 光催化分解水产氢固溶体催化剂制备技术揭秘

- VS2013环境下tinyxml库的32位与64位编译指南

- 网易云歌词情感分析系统实现与架构

- React应用展示GitHub用户详细信息及项目分析

- LayUI2.1.6帮助文档API功能详解

- 全栈开发实现的chatgpt应用可打包小程序/H5/App

- C++实现顺序表的动态内存分配技术

- Java制作水果格斗游戏:策略与随机性的结合

- 基于若依框架的后台管理系统开发实例解析

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功