Xilinx AXI Interconnect v2.1:产品指南与设计支持

Xilinx Axi Interconnect是一款针对FPGA(现场可编程门阵列)设计的专业IP核,旨在提供高性能和灵活的高级扩展接口(Accelerator eXtensible Interface, AXI)连接解决方案。AXI Interconnect是LogiCORE IP产品系列的一部分,它在Vivado Design Suite这个强大的设计环境中被广泛应用,帮助设计师构建高效且可扩展的系统架构。

该产品在Vivado Design Suite 2022年5月的版本中进行了更新,注重创造一个包容性的工作环境,通过去除可能具有排他性或反映历史偏见的语言,确保所有用户都能感到舒适和接纳。尽管如此,早期产品的文档中可能仍存在非包容性语言,但Xilinx正积极进行内部整改以遵循不断发展的行业标准。

产品指南涵盖了多个关键方面:

1. **IP Facts**:

- 本产品专注于AXI基础设施核心功能,提供高效的数据传输和通信通道,适用于各种应用需求。

- 功能概述强调了其灵活性和性能优化,可以支持不同的设计场景。

2. **Chapter 1: Overview**:

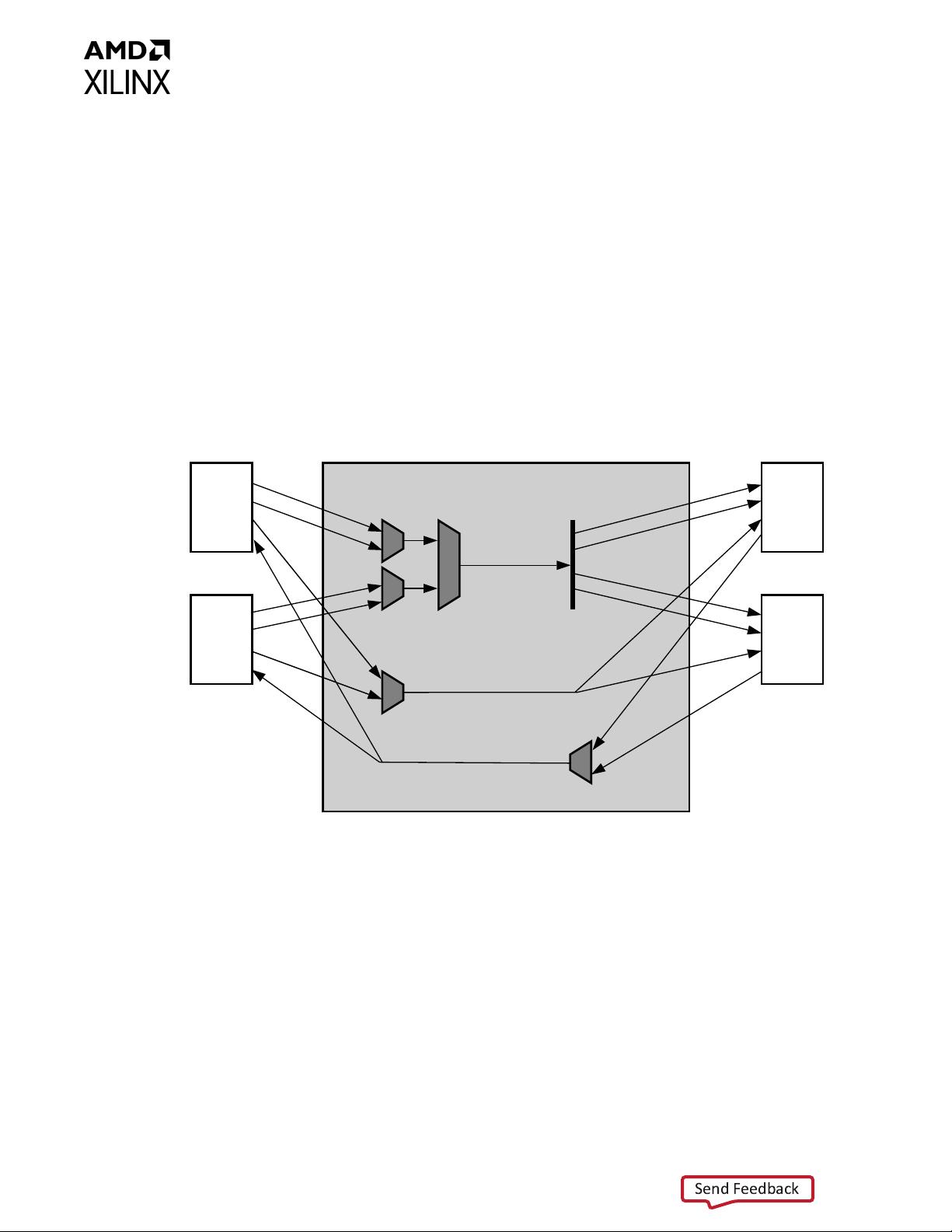

- 本章介绍了AXI Interconnect的核心特点,包括但不限于支持多种总线宽度和地址宽度,适用于数据、控制、仲裁等不同类型的通信。

- 应用场景广泛,包括但不限于处理加速器之间的通信、存储器接口以及复杂的系统级互联。

3. **Chapter 2: Product Specification**:

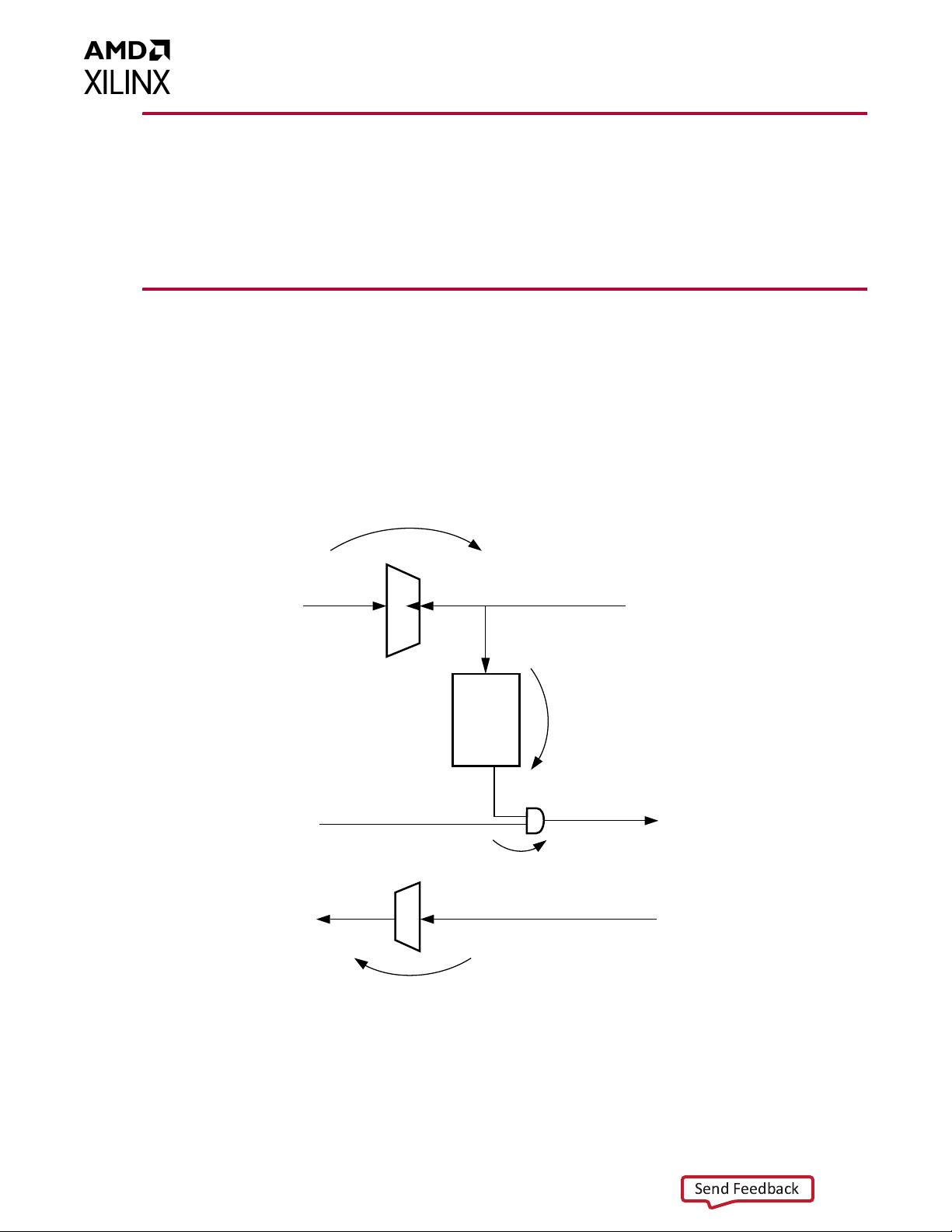

- 详细规定了产品的工作模型,确保与其他AXI兼容组件无缝协作。

- 标准部分阐述了AXI协议兼容性和规范,保证了与Xilinx和其他供应商产品的互操作性。

- 性能参数包括最小延迟和最大吞吐量,以及资源利用情况,这对于设计师评估其在具体设计中的适用性和效率至关重要。

- Port Descriptions部分提供了详细的接口描述,以便用户了解如何配置和连接各个端口。

4. **Chapter 3: Designing with the Core**:

- 本章节深入探讨了如何在设计中实现AXI Interconnect的功能,包括设计参数的设定和调整,确保用户能够根据项目需求定制合适的配置。

- 它还涵盖了如何处理可能遇到的限制,例如性能瓶颈或者资源冲突,并提供了最佳实践和指导。

在使用AXI Interconnect时,设计师需要注意的是,虽然旧版本文档可能存在非包容性语言,但随着时间的推移,Xilinx会持续改进其产品,以适应不断变化的技术趋势和社会标准。因此,在选择和使用该IP核时,务必参考最新文档和指南,以获取最准确的信息和最新的最佳实践。

523 浏览量

1653 浏览量

275 浏览量

287 浏览量

277 浏览量

212 浏览量

2024-11-03 上传

2024-11-03 上传

2024-11-04 上传

scottwqn

- 粉丝: 0

- 资源: 4

最新资源

- Touch-Friendliness for Discord-crx插件

- fine_conf_entity_10

- imagenet-vgg-verydeep-19.zip

- 特种部队

- Forecating-Weather-App-:显示即将到来的3天天气详细信息基于国家/地区州搜索

- yiweijunyun_matlab_

- nagios-plugins-rabbitmq:一组使用管理界面的RabbitMQ的nagios检查

- For-Step-Class

- Wheebox Tests : Enable Screen Sharing-crx插件

- Morrowind-Modular-Mod-Guide:适用于Morrowind的模块化,香草友好的安装指南

- .NET基于SMTP发送邮件

- Note-application-with-node.js

- kav2010_9.0.0.736ES.rar

- adinabasaraba99:我的GitHub个人资料的配置文件

- defcon24-infra-monitoring-workshop:Defcon24研讨会内容:忍者级基础设施监视

- gulp-swagger-typescript-angular