VHDL大规模逻辑设计指南

需积分: 1 171 浏览量

更新于2024-07-27

收藏 3.45MB PDF 举报

"该文档是关于大规模逻辑设计的指导,主要使用VHDL语言进行讲解。文档分为多个章节,详细阐述了VHDL编码的方法、规范以及在设计中需要注意的问题。内容涵盖了从基本的语法元素如信号和变量的命名,到更高级的概念如FSM(有限状态机)、函数和过程、程序包的编写实例,还包括了代码编写中的常见问题和最佳实践。文档还强调了代码风格和综合考虑,旨在提高设计的效率和可读性。"

在大规模逻辑设计中,VHDL是一种常用的硬件描述语言,它允许设计者以结构化的方式描述数字系统的功能和行为。以下是一些关键的知识点:

1. **命名规范**:设计中选择有意义的信号和变量名至关重要。名字应反映其功能,如信号的来源或变量的有效状态。这有助于提高代码的可读性和可维护性。

2. **编码风格**:有明确的编码规范能提升代码质量。例如,使用TAB键间隔可以使代码更整洁,而良好的注释(comments)能帮助理解代码意图。

3. **基本元素**:VHDL中的基本元素包括信号(signals)和变量(variables),它们分别代表硬件连接和存储数据。理解何时使用信号和变量是VHDL学习的基础。

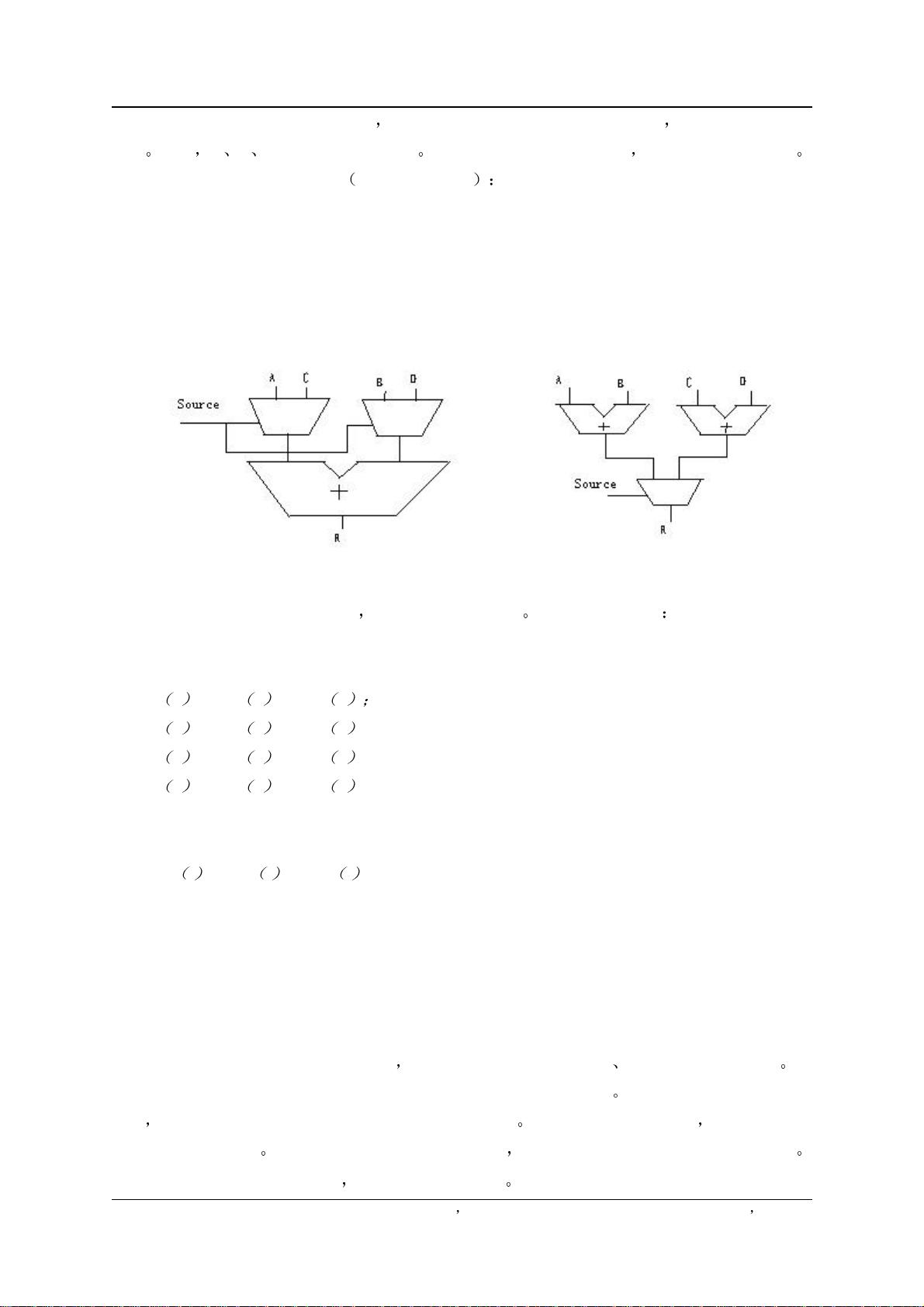

4. **逻辑类型**:理解并行与顺序逻辑的区别(Combinatorial Vs Sequential Logic)对于设计正确的行为至关重要。组合逻辑在任何时钟周期内都立即响应输入,而顺序逻辑则依赖于时钟边沿。

5. **赋值语句**:VHDL中的赋值操作包括“=”和“:=”。了解它们的差异,例如“=”用于非阻塞赋值,适用于组合逻辑,而“:=”用于阻塞赋值,适用于时序逻辑。

6. **控制结构**:IF语句和CASE语句是控制流程的关键,用于根据条件执行不同路径。理解如何有效地使用它们对于实现复杂逻辑至关重要。

7. **函数和过程**:function和procedure是VHDL中封装计算逻辑的手段。函数返回一个值,而过程不返回值但可以改变其内部的变量。

8. **FSM(有限状态机)**:FSM是描述数字系统行为的一种常见方法。理解如何用VHDL描述状态转移和事件响应是设计复杂系统的关键。

9. **资源共享**:在设计中,合理利用资源可以提高效率。理解如何避免不必要的 latch 使用和考虑综合的执行时间是优化设计的重要步骤。

10. **参数化元件**:通过参数化元件,可以创建可重用的设计模块,增加代码的灵活性和可扩展性。

11. **程序包(package)**:程序包用来集合常量、类型定义、函数和过程,提供代码复用,提高组织性。

每个章节都提供了深入的细节和实例,帮助读者逐步掌握VHDL编程的艺术,从而能够进行高效的大规模逻辑设计。此外,文档还强调了版权和保密性,表明其内容的重要性。通过遵循这些指导原则,设计师可以创建出更高效、可读且易于维护的VHDL代码。

2009-10-13 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

hbjnj

- 粉丝: 0

- 资源: 3

最新资源

- 磁性吸附笔筒设计创新,行业文档精选

- Java Swing实现的俄罗斯方块游戏代码分享

- 骨折生长的二维与三维模型比较分析

- 水彩花卉与羽毛无缝背景矢量素材

- 设计一种高效的袋料分离装置

- 探索4.20图包.zip的奥秘

- RabbitMQ 3.7.x延时消息交换插件安装与操作指南

- 解决NLTK下载停用词失败的问题

- 多系统平台的并行处理技术研究

- Jekyll项目实战:网页设计作业的入门练习

- discord.js v13按钮分页包实现教程与应用

- SpringBoot与Uniapp结合开发短视频APP实战教程

- Tensorflow学习笔记深度解析:人工智能实践指南

- 无服务器部署管理器:防止错误部署AWS帐户

- 医疗图标矢量素材合集:扁平风格16图标(PNG/EPS/PSD)

- 人工智能基础课程汇报PPT模板下载