5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

CFG5

PEG_RXN4

PEG_TXN5

PEG_RXN7

PEG_RXN6

PEG_RXN5

PEG_TXN7

PEG_RXP4

PEG_RXP7

PEG_RXP6

PEG_RXP5

PEG_RXP14

PEG_RXP12

PEG_RXP3

PEG_RXP2

PEG_RXP0

PEG_RXP13

PEG_RXP15

PEG_RXP10

PEG_RXP8

PEG_RXP1

PEG_RXP9

PEG_RXP11

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TXN12

PEG_RXN0

PEG_RXN12

PEG_RXN3

PEG_RXN2

PEG_RXN10

PEG_RXN8

PEG_RXN13

PEG_RXN15

PEG_RXN14

PEG_TXN9

PEG_RXN9

PEG_RXN11

PEG_TXN6

PEG_TXN10

PEG_TXN11

PEG_TXN8

PEG_TXP13

PEG_TXP7

PEG_TXN4

PEG_TXP5

PEG_TXP6

PEG_TXP12

PEG_TXP14

PEG_TXP15

PEG_TXP11

PEG_TXP9

PEG_TXP8

PEG_TXP10

PEG_TXP4

PEG_TXP1

PEG_TXP0

PEG_TXP2

PEG_TXN0

PEG_TXP3

PEG_TXN1

PEG_RXN1

PEG_TXN3

PEG_TXN2

CFG59

CFG69

CFG79

CFG89

CFG99

CFG109

CFG119

CFG129

CFG139

CFG149

CFG159

CFG179

CFG189

CFG169

CFG199

CFG209

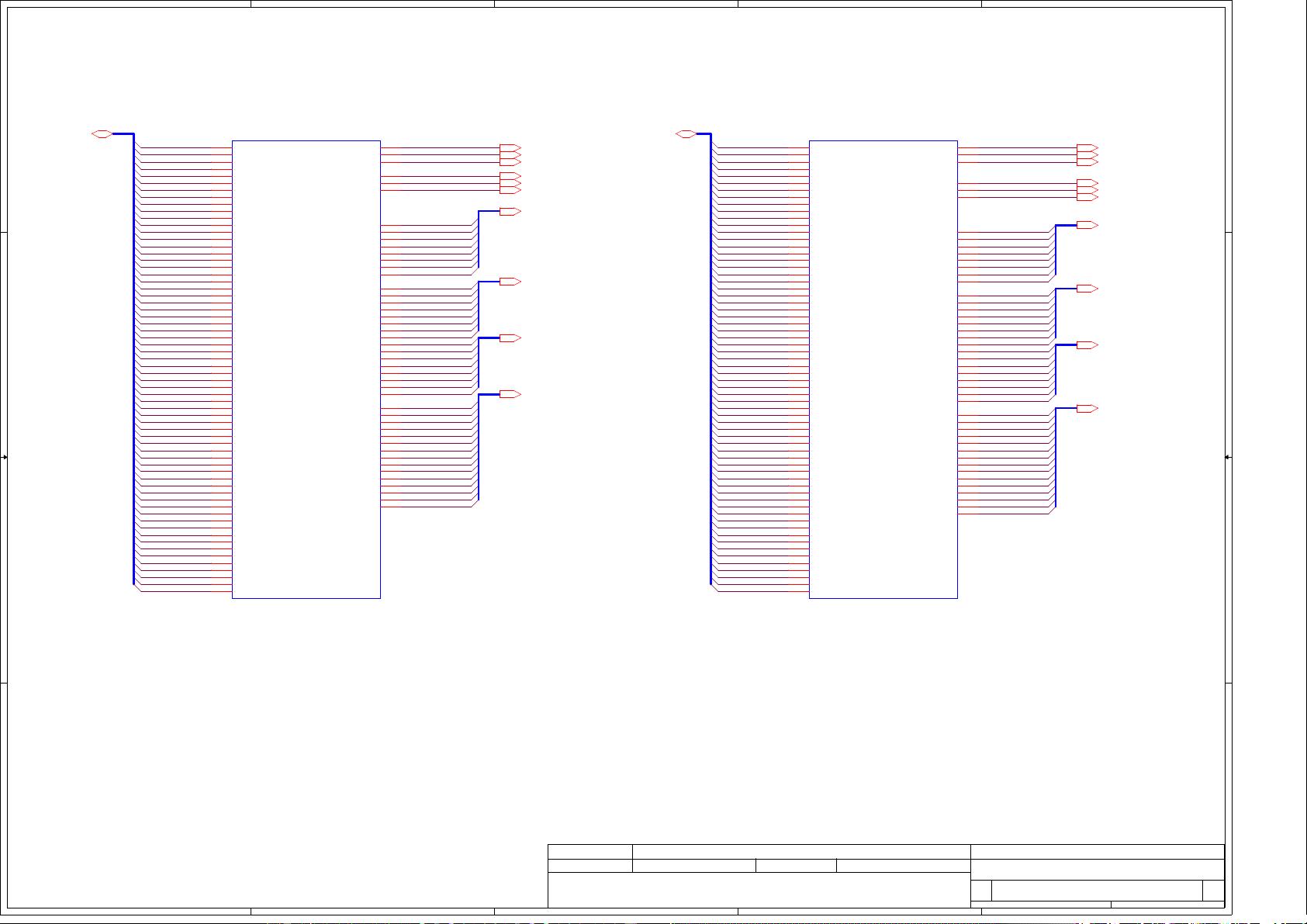

PEG_M_TXN3 20

PEG_M_TXN2 20

PEG_M_TXN1 20

PEG_M_TXN0 20

PEG_M_TXP2 20

PEG_M_TXP3 20

PEG_M_TXP1 20

PEG_M_TXP0 20

PEG_RXN3 20

PEG_RXN2 20

PEG_RXN1 20

PEG_RXN0 20

PEG_RXN5 20

PEG_RXN7 20

PEG_RXN6 20

PEG_RXN4 20

PEG_RXN13 20

PEG_RXN15 20

PEG_RXN14 20

PEG_RXN12 20

PEG_RXN9 20

PEG_RXN11 20

PEG_RXN10 20

PEG_RXN8 20

PEG_RXP5 20

PEG_RXP7 20

PEG_RXP6 20

PEG_RXP4 20

PEG_RXP12 20

PEG_RXP3 20

PEG_RXP2 20

PEG_RXP0 20

PEG_RXP8 20

PEG_RXP13 20

PEG_RXP15 20

PEG_RXP14 20

PEG_RXP1 20

PEG_RXP9 20

PEG_RXP11 20

PEG_RXP10 20

PEG_M_TXN7 20

PEG_M_TXN6 20

PEG_M_TXN5 20

PEG_M_TXN4 20

PEG_M_TXN10 20

PEG_M_TXN9 20

PEG_M_TXN8 20

PEG_M_TXN14 20

PEG_M_TXN13 20

PEG_M_TXN12 20

PEG_M_TXN11 20

PEG_M_TXP6 20

PEG_M_TXP5 20

PEG_M_TXP4 20

PEG_M_TXN15 20

PEG_M_TXP10 20

PEG_M_TXP9 20

PEG_M_TXP8 20

PEG_M_TXP7 20

PEG_M_TXP13 20

PEG_M_TXP12 20

PEG_M_TXP11 20

PEG_M_TXP15 20

PEG_M_TXP14 20

+VCC_PEG

+3VS

+3VS

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

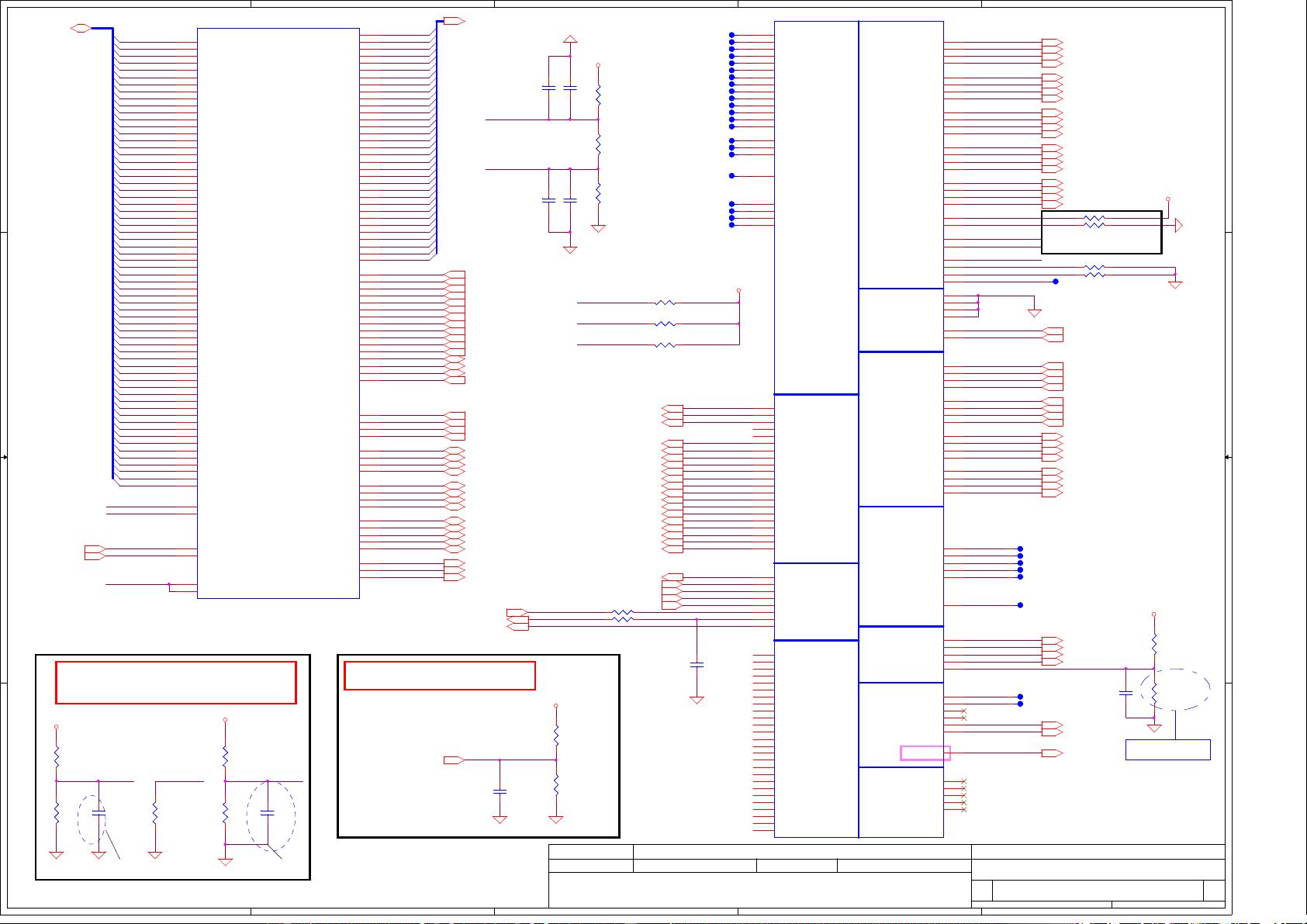

Montevina Consumer Discrete

0.1

Cantiga(3/6)-VGA/LVDS/TV

Custom

11 51Monday, October 08, 2007

2007/09/26 2007/09/26

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

Montevina Consumer Discrete

0.1

Cantiga(3/6)-VGA/LVDS/TV

Custom

11 51Monday, October 08, 2007

2007/09/26 2007/09/26

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

Montevina Consumer Discrete

0.1

Cantiga(3/6)-VGA/LVDS/TV

Custom

11 51Monday, October 08, 2007

2007/09/26 2007/09/26

Compal Electronics, Inc.

PEGCOMP trace width

and spacing is 20/25 mils.

000 = FSB 1066MHz

CFG[4:3]

Reserved

CFG6

0 = The iTPM Host Interface is enable

1 = The iTPM Host Interface is disable

*

Reserved

CFG10

(Default)11 = Normal Operation

10 = All Z Mode Enabled

00 = Reserved

01 = XOR Mode Enabled

*

0 = Enable

1 = Disable

*

CFG9 (PCIE Graphics

Lane Reversal)

CFG[2:0] FSB Freq

select

Reserved

Reserved

CFG[15:14]

Strap Pin Table

Reserved

CFG[18:17]

(Lane number in Order)

Others = Reserved

011 = FSB 667MHz

010 = FSB 800MHz

*

1 = Reverse Lane

0 = Reverse Lane,15->0, 14->1

1 = Enabled

0 = Normal Operation

0 = Disabled

*

0 = DMI x 2

*

*

*

1 = PCIE/SDVO are operating simu.

0 = Only PCIE or SDVO is operational.

*

1 = Normal Operation,Lane Number in

order

1 = DMI x 4

0 =(TLS)chiper suite with no confidentiality

1 =(TLS)chiper suite with confidentiality

CFG5 (DMI select)

CFG19 (DMI Lane Reversal)

CFG16 (FSB Dynamic ODT)

CFG7

CFG20

CFG11

CFG[13:12] (XOR/ALLZ)

CFG8

(Intel Management

Engine Crypto strap)

(PCIE

Lookback

enable)

(PCIE/SDVO

concurrent)

R71

4.02K_0402_1%

R71

4.02K_0402_1%

12

C1315 0.1U_0402_16V4ZC1315 0.1U_0402_16V4Z

1 2

R81

2.21K_0402_1%

R81

2.21K_0402_1%

1 2

C1303 0.1U_0402_16V4ZC1303 0.1U_0402_16V4Z

1 2

R77

2.21K_0402_1%

R77

2.21K_0402_1%

1 2

R73

4.02K_0402_1%

@ R73

4.02K_0402_1%

@

1 2

C1295 0.1U_0402_16V4ZC1295 0.1U_0402_16V4Z

1 2

C1293 0.1U_0402_16V4ZC1293 0.1U_0402_16V4Z

1 2

C1313 0.1U_0402_16V4ZC1313 0.1U_0402_16V4Z

1 2

C1304 0.1U_0402_16V4ZC1304 0.1U_0402_16V4Z

1 2

R74

2.21K_0402_1%

@

R74

2.21K_0402_1%

@

12

C1296 0.1U_0402_16V4ZC1296 0.1U_0402_16V4Z

1 2

R72

4.02K_0402_1%

R72

4.02K_0402_1%

1 2

R82

2.21K_0402_1%

@R82

2.21K_0402_1%

@

1 2

C1292 0.1U_0402_16V4ZC1292 0.1U_0402_16V4Z

1 2

C1294 0.1U_0402_16V4ZC1294 0.1U_0402_16V4Z

1 2

C1310 0.1U_0402_16V4ZC1310 0.1U_0402_16V4Z

1 2

R75

4.02K_0402_1%

@R75

4.02K_0402_1%

@

1 2

C1309 0.1U_0402_16V4ZC1309 0.1U_0402_16V4Z

1 2

C1298 0.1U_0402_16V4ZC1298 0.1U_0402_16V4Z

1 2

C1300 0.1U_0402_16V4ZC1300 0.1U_0402_16V4Z

1 2

C1297 0.1U_0402_16V4ZC1297 0.1U_0402_16V4Z

1 2

C1314 0.1U_0402_16V4ZC1314 0.1U_0402_16V4Z

1 2

R84

2.21K_0402_1%

@R84

2.21K_0402_1%

@

1 2

C1316 0.1U_0402_16V4ZC1316 0.1U_0402_16V4Z

1 2

C1305 0.1U_0402_16V4ZC1305 0.1U_0402_16V4Z

1 2

C1320 0.1U_0402_16V4ZC1320 0.1U_0402_16V4Z

1 2

C1312 0.1U_0402_16V4ZC1312 0.1U_0402_16V4Z

1 2

R76

2.21K_0402_1%

@R76

2.21K_0402_1%

@

1 2

C1319 0.1U_0402_16V4ZC1319 0.1U_0402_16V4Z

1 2

C1289 0.1U_0402_16V4ZC1289 0.1U_0402_16V4Z

1 2

R85

2.21K_0402_1%

@R85

2.21K_0402_1%

@

1 2

C1306 0.1U_0402_16V4ZC1306 0.1U_0402_16V4Z

1 2

C1317 0.1U_0402_16V4ZC1317 0.1U_0402_16V4Z

1 2

C1302 0.1U_0402_16V4ZC1302 0.1U_0402_16V4Z

1 2

C1299 0.1U_0402_16V4ZC1299 0.1U_0402_16V4Z

1 2

R83

2.21K_0402_1%

@R83

2.21K_0402_1%

@

1 2

C1307 0.1U_0402_16V4ZC1307 0.1U_0402_16V4Z

1 2

R79

2.21K_0402_1%

@R79

2.21K_0402_1%

@

1 2

C1318 0.1U_0402_16V4ZC1318 0.1U_0402_16V4Z

1 2

C1291 0.1U_0402_16V4ZC1291 0.1U_0402_16V4Z

1 2

R87

2.21K_0402_1%

@R87

2.21K_0402_1%

@

1 2

C1308 0.1U_0402_16V4ZC1308 0.1U_0402_16V4Z

1 2

R57

49.9_0402_1%

R57

49.9_0402_1%

1 2

R78

2.21K_0402_1%

R78

2.21K_0402_1%

1 2

C1301 0.1U_0402_16V4ZC1301 0.1U_0402_16V4Z

1 2

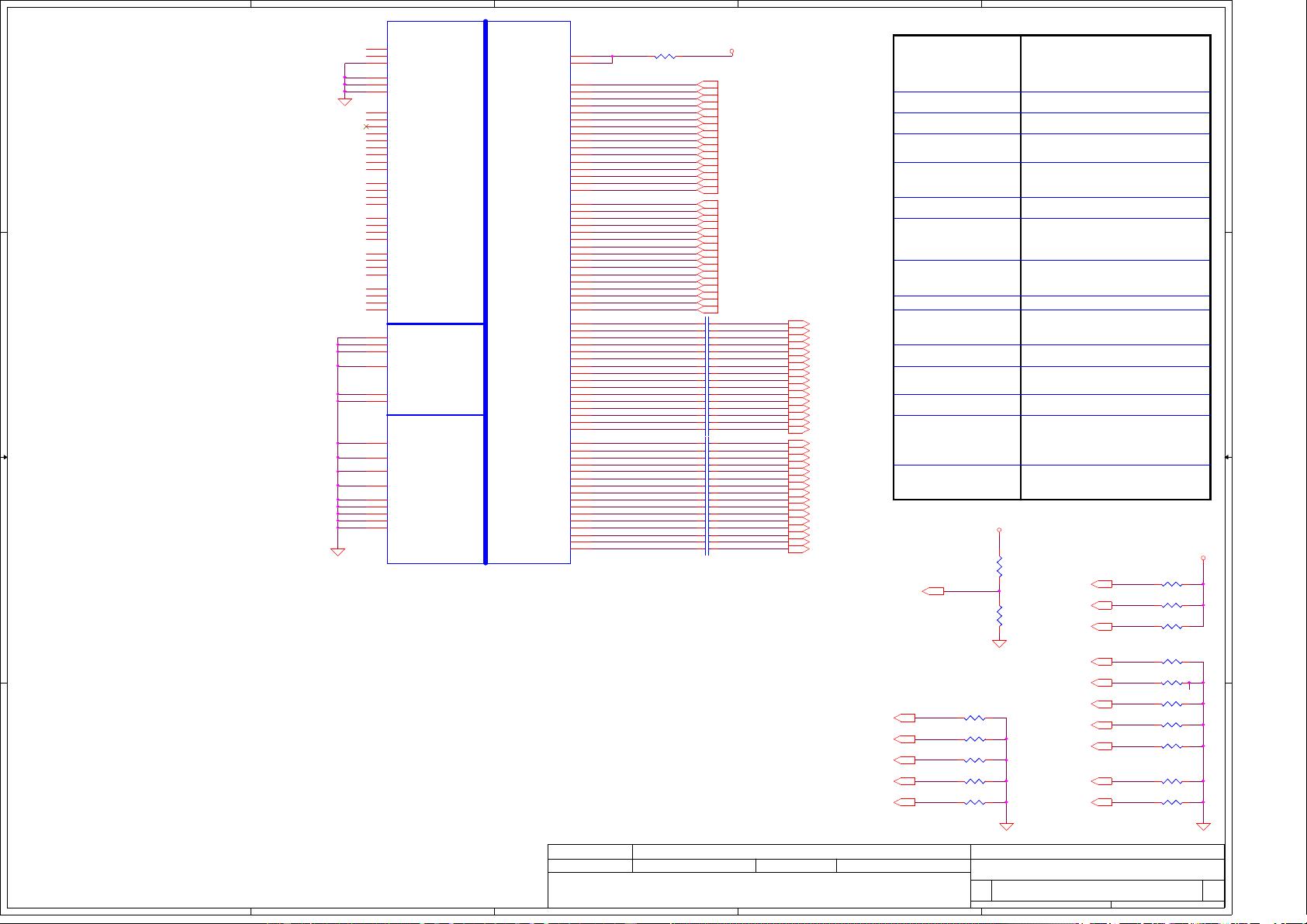

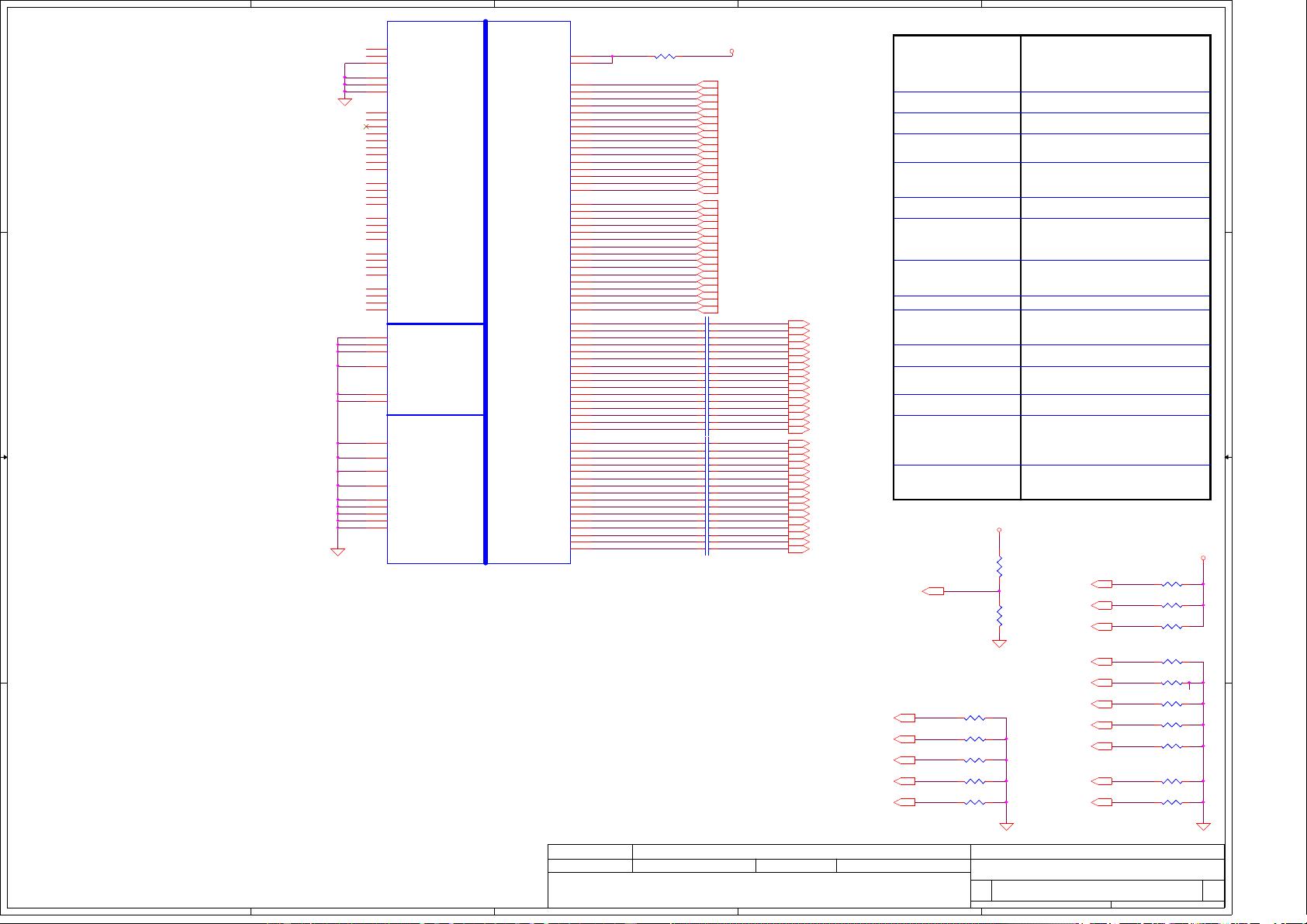

LVDS

PCI-EXPRESS GRAPHICS

TV VGA

U2C

CANTIGA ES_FCBGA1329

LVDS

PCI-EXPRESS GRAPHICS

TV VGA

U2C

CANTIGA ES_FCBGA1329

PEG_COMPI

T37

PEG_COMPO

T36

PEG_RX#_0

H44

PEG_RX#_1

J46

PEG_RX#_2

L44

PEG_RX#_3

L40

PEG_RX#_4

N41

PEG_RX#_5

P48

PEG_RX#_6

N44

PEG_RX#_7

T43

PEG_RX#_8

U43

PEG_RX#_9

Y43

PEG_RX#_10

Y48

PEG_RX#_11

Y36

PEG_RX#_12

AA43

PEG_RX#_13

AD37

PEG_RX#_14

AC47

PEG_RX#_15

AD39

PEG_RX_0

H43

PEG_RX_1

J44

PEG_RX_2

L43

PEG_RX_3

L41

PEG_RX_4

N40

PEG_RX_5

P47

PEG_RX_6

N43

PEG_RX_7

T42

PEG_RX_8

U42

PEG_RX_9

Y42

PEG_RX_10

W47

PEG_RX_11

Y37

PEG_RX_12

AA42

PEG_RX_13

AD36

PEG_RX_14

AC48

PEG_RX_15

AD40

PEG_TX#_0

J41

PEG_TX#_10

Y40

PEG_TX#_3

M40

PEG_TX#_4

M42

PEG_TX#_5

R48

PEG_TX#_6

N38

PEG_TX#_7

T40

PEG_TX#_8

U37

PEG_TX#_9

U40

PEG_TX#_1

M46

PEG_TX#_11

AA46

PEG_TX#_12

AA37

PEG_TX#_13

AA40

PEG_TX#_14

AD43

PEG_TX#_15

AC46

PEG_TX#_2

M47

PEG_TX_0

J42

PEG_TX_1

L46

PEG_TX_2

M48

PEG_TX_3

M39

PEG_TX_4

M43

PEG_TX_5

R47

PEG_TX_6

N37

PEG_TX_7

T39

PEG_TX_8

U36

PEG_TX_9

U39

PEG_TX_10

Y39

PEG_TX_11

Y46

PEG_TX_12

AA36

PEG_TX_13

AA39

PEG_TX_14

AD42

PEG_TX_15

AD46

L_CTRL_CLK

M32

L_CTRL_DATA

M33

L_DDC_CLK

K33

L_DDC_DATA

J33

L_VDD_EN

M29

LVDS_IBG

C44

LVDS_VBG

B43

LVDS_VREFH

E37

LVDS_VREFL

E38

LVDSA_CLK#

C41

LVDSA_CLK

C40

LVDSA_DATA#_0

H47

LVDSA_DATA#_1

E46

LVDSA_DATA#_2

G40

LVDSA_DATA_1

D45

LVDSA_DATA_2

F40

LVDSB_CLK#

B37

LVDSB_CLK

A37

LVDSB_DATA#_0

A41

LVDSB_DATA#_1

H38

LVDSB_DATA#_2

G37

LVDSB_DATA_1

G38

LVDSB_DATA_2

F37

L_BKLT_EN

G32

TVA_DAC

F25

TVB_DAC

H25

TVC_DAC

K25

TV_RTN

H24

CRT_BLUE

E28

CRT_DDC_CLK

H32

CRT_DDC_DATA

J32

CRT_GREEN

G28

CRT_HSYNC

J29

CRT_TVO_IREF

E29

CRT_RED

J28

CRT_IRTN

G29

CRT_VSYNC

L29

LVDSA_DATA_0

H48

LVDSB_DATA_0

B42

L_BKLT_CTRL

L32

TV_DCONSEL_0

C31

TV_DCONSEL_1

E32

LVDSA_DATA#_3

A40

LVDSA_DATA_3

B40

LVDSB_DATA#_3

J37

LVDSB_DATA_3

K37

R80

2.21K_0402_1%

@R80

2.21K_0402_1%

@

1 2

C1311 0.1U_0402_16V4ZC1311 0.1U_0402_16V4Z

1 2

C1290 0.1U_0402_16V4ZC1290 0.1U_0402_16V4Z

1 2

R86

2.21K_0402_1%

@R86

2.21K_0402_1%

@

1 2