《计算机组成与设计·硬件/软件接·RISC-V版》第4章处理器内容总结

需积分: 0 185 浏览量

更新于2024-01-02

收藏 4.25MB PDF 举报

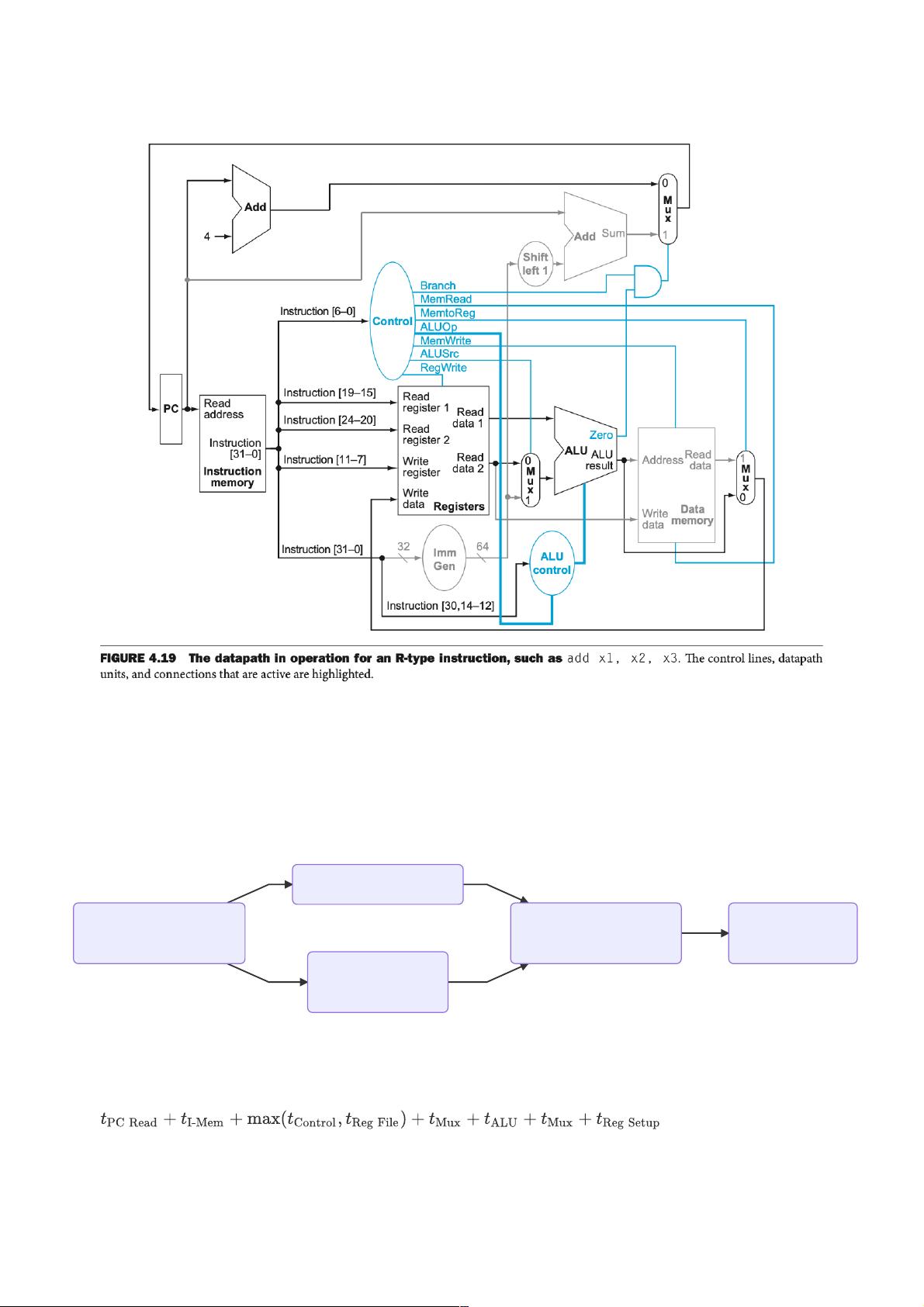

本章内容对应《计算机组成与设计·硬件/软件接·RISC-V版》的第 4 章处理器的内容。在本章中,将实现 RISC-V 的一个核心子集,包括存储器访问指令 ld 和 sd、算术逻辑指令 add、sub、and 和 or,以及条件分支指令 beq。执行这些指令的大部分工作是相同的:首先,PC发送到指令所在的存储单元,从中取出指令。然后,处理器读取一个或两个寄存器(对于ld指令,读取一个寄存器;对于其他指令,读取两个寄存器)。接下来,根据不同的指令类型,处理器进行不同的操作:对于访存指令,使用ALU计算地址并访问存储器;对于算术逻辑指令,使用ALU进行运算;对于条件分支指令,使用ALU进行比较。最后,对于存储器访问指令sd,将数据存入存储器中。

本章主要内容包括处理器1的概述、单周期数据通路、流水线等。处理器1的概述部分对于章节内容进行了简要介绍,为后续内容的学习提供了基础。在单周期数据通路部分,详细介绍了控制信号、不同类型指令的数据通路等,帮助读者理解不同指令类型在处理器中的执行过程。而流水线部分则进一步探讨了流水线的概念、流水线冒险以及解决流水线冒险的方法,通过具体的数据通路分析和实例说明,帮助读者深入理解流水线的工作原理及其中可能出现的问题和解决方案。

在流水线数据通路部分,本章详细介绍了流水线的数据通路结构,并对数据冒险、控制冒险等问题进行了深入的讨论。针对数据冒险问题,本章提出了前递和停顿两种解决方案,并对其进行了详细的分析和比较。针对控制冒险问题,本章介绍了缩短分支延迟和动态分支预测两种解决方法,并对其进行了具体的实例说明,帮助读者理解并掌握解决控制冒险问题的策略。

此外,本章还介绍了处理器中可能出现的例外情况,以及指令并行与多发射的相关内容,为读者进一步探索处理器运行机制提供了拓展的空间。通过本章的学习,读者不仅能够掌握处理器的基本运行原理和数据通路结构,还能够深入理解处理器中可能出现的问题及解决方法,为今后的学习和工作打下坚实的基础。

综上所述,本章内容对于理解处理器的工作原理和学习处理器的基本知识具有重要意义。通过本章的学习,读者能够深入了解处理器的数据通路结构、流水线运行机制以及可能出现的问题和解决方法,为后续学习和工作提供了重要的参考和指导。同时,本章还为读者提供了进一步学习处理器相关知识的拓展方向,为读者的综合能力提升和专业素养培养提供了重要的支持。

2022-08-03 上传

2022-08-03 上传

101 浏览量

2020-07-13 上传

2011-02-04 上传

点击了解资源详情

点击了解资源详情

2023-02-22 上传

虚伪的小白

- 粉丝: 26

- 资源: 321

最新资源

- Angular实现MarcHayek简历展示应用教程

- Crossbow Spot最新更新 - 获取Chrome扩展新闻

- 量子管道网络优化与Python实现

- Debian系统中APT缓存维护工具的使用方法与实践

- Python模块AccessControl的Windows64位安装文件介绍

- 掌握最新*** Fisher资讯,使用Google Chrome扩展

- Ember应用程序开发流程与环境配置指南

- EZPCOpenSDK_v5.1.2_build***版本更新详情

- Postcode-Finder:利用JavaScript和Google Geocode API实现

- AWS商业交易监控器:航线行为分析与营销策略制定

- AccessControl-4.0b6压缩包详细使用教程

- Python编程实践与技巧汇总

- 使用Sikuli和Python打造颜色求解器项目

- .Net基础视频教程:掌握GDI绘图技术

- 深入理解数据结构与JavaScript实践项目

- 双子座在线裁判系统:提高编程竞赛效率