AXI总线协议详解:高性能SoC设计的关键

需积分: 1 49 浏览量

更新于2024-07-02

收藏 1.74MB DOC 举报

AXI总线协议相关解读深入剖析

AXI(Advanced eXtensible Interface)是ARM公司推出的一种高级片内总线协议,作为AMBA 3.0协议的重要组成部分,它专为高性能、高带宽和低延迟设计。AXI的特点主要体现在以下几个方面:

1. 单向通道体系结构:AXI采用单向通道设计,降低了信号传输的复杂性,减少了时钟域之间的桥接所需门的数量,从而减小延迟。这种设计有助于简化系统集成,并降低功耗。

2. 独立地址和数据通道:地址和数据传输被分离处理,每个通道可以独立优化,提供更大的灵活性。这意味着可以根据需求调整时序,提高数据传输速度,同时确保低延迟。

3. 支持多数据交换与猝发操作:通过并行执行数据交换,AXI极大提升了数据吞吐量,使得系统能够在较短时间内完成任务,满足高性能需求。

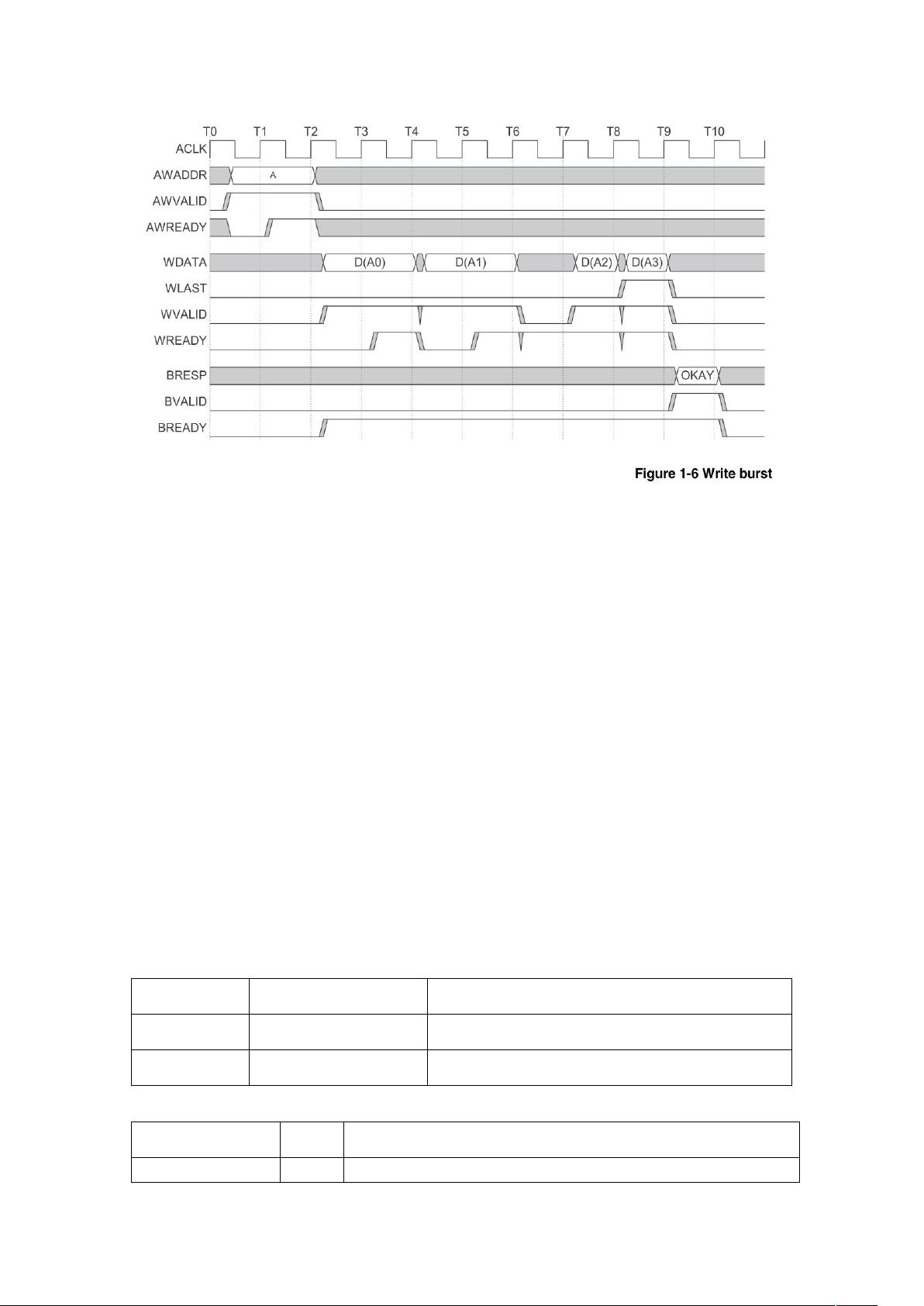

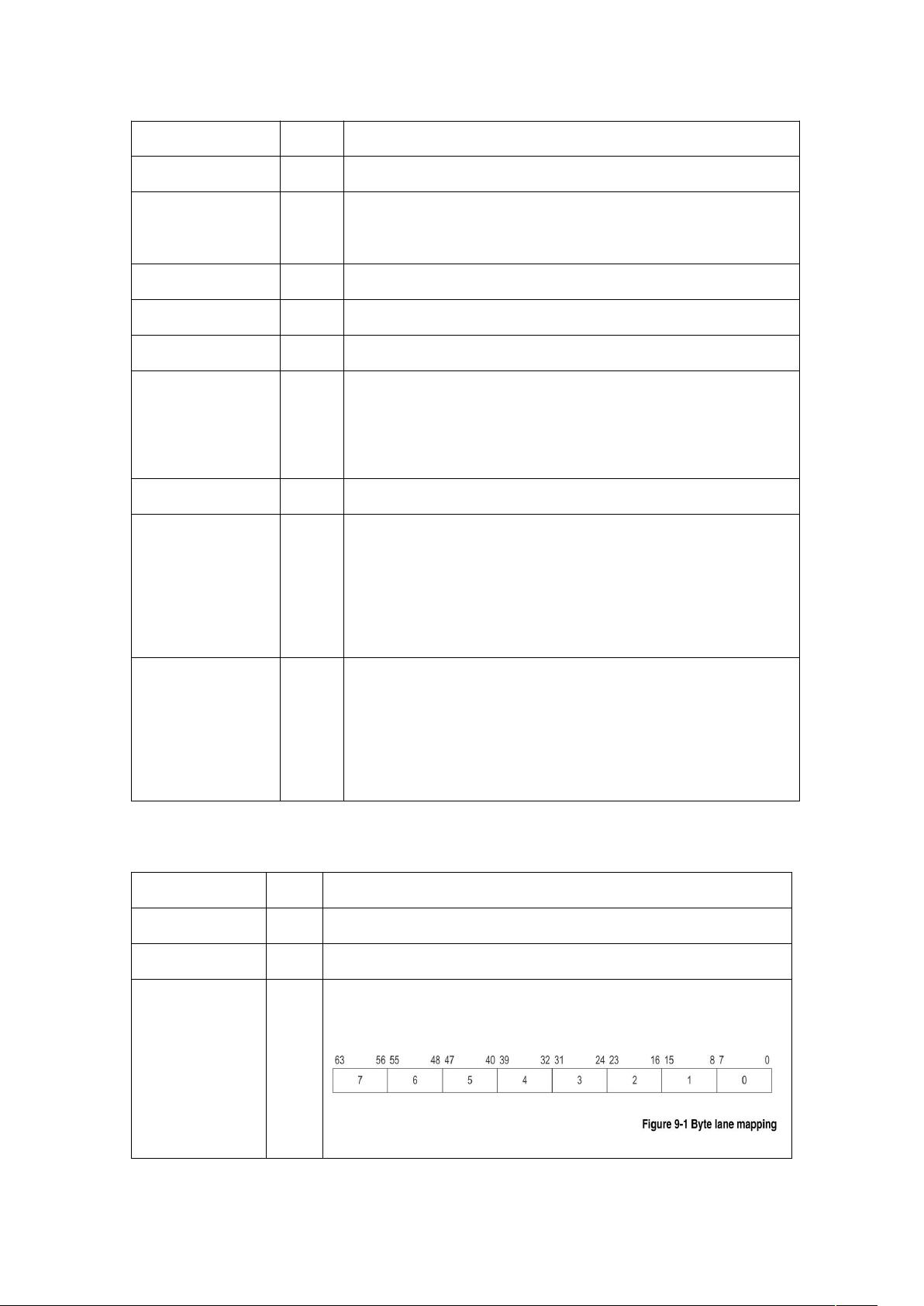

4. 事务结构:AXI总线包括五个独立通道:readaddresschannel、writeaddresschannel、readdatachannel、writedatachannel和writeresponsechannel。每个通道都有明确的功能,如地址信息传输和数据交换。例如,读事务结构图和写事务结构图展示了数据如何通过这些通道进行传递,以及地址和控制信息的传递方式。

5. 握手机制:每个通道都包含信息信号和VALD(validity)和READY信号,用于同步数据的有效性和接收状态。读数据通道负责从设备到主机的读数据和读响应,而写数据通道则负责数据写入和确认。

6. 完成状态指示:无论是读还是写事务,都有专门的LAST信号来标记事务的结束,这对于错误检测和处理至关重要。

通过AXI1.0协议的详细章节学习,开发人员可以更好地理解和应用这一高性能总线标准,从而优化片上系统(SoC)设计,提升系统性能和能效。掌握AXI协议对于构建现代高性能嵌入式系统和处理器架构至关重要。

722 浏览量

234 浏览量

202 浏览量

2329 浏览量

278 浏览量

2024-02-19 上传

点击了解资源详情

2266 浏览量

162 浏览量

青花127

- 粉丝: 28

- 资源: 9