Verilog HDL入门教程:基础语法与建模解析

需积分: 36 107 浏览量

更新于2024-07-16

4

收藏 271KB PDF 举报

"Verilog+HDL入门教程.pdf"

这是一份关于Verilog HDL的入门教程,适合初学者学习和了解这一重要的硬件描述语言。Verilog HDL是一种用于电子系统设计的标准化语言,广泛应用于集成电路(IC)设计,尤其是FPGA(现场可编程门阵列)和ASIC(应用专用集成电路)的设计。

教程首先介绍了Verilog HDL的基本概念,包括其历史、设计方法学以及它在数字电路设计中的作用。Verilog HDL起源于20世纪80年代,是一种强大的硬件描述工具,能够用来描述从低级别门电路到高级别系统级别的设计。

接着,教程详细讲解了Verilog HDL的基本语法。这包括标识符的定义、关键词的使用、书写规范建议以及注释的添加。在数据类型部分,教程涵盖了线网类型和寄存器类型,这些都是构建Verilog模型的基础。此外,还讨论了数字值集合、常量以及各种运算符,如算术运算符、逻辑运算符、关系运算符和按位逻辑运算符。

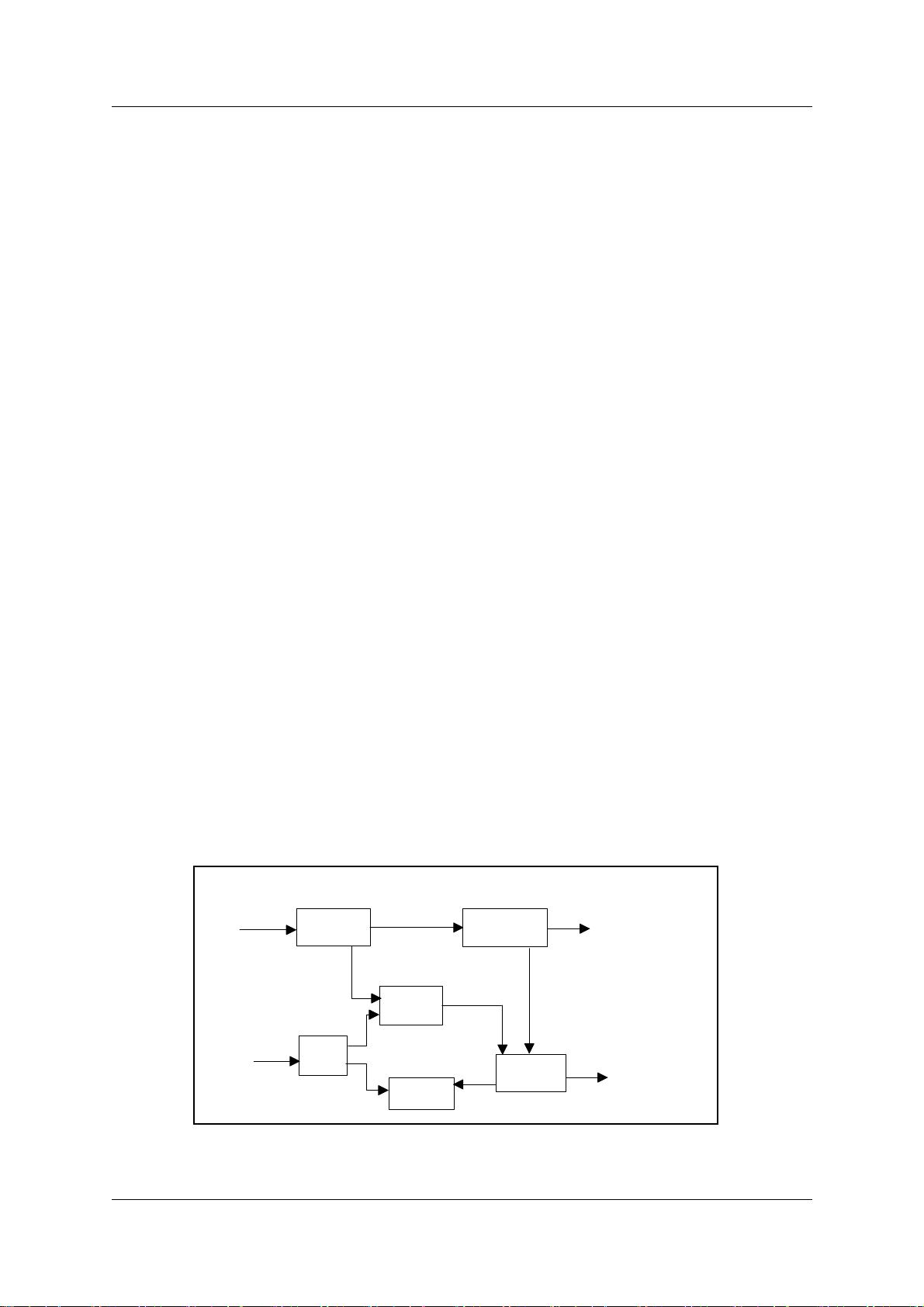

在建模方面,教程阐述了Verilog HDL的三种主要建模方式:结构化描述、数据流描述和行为描述。结构化描述允许设计者用硬件组件(如门和触发器)来表示设计;数据流描述则关注信号的流动和操作;行为描述则更接近于软件编程,用于描述系统的动态行为。教程还包含了条件语句(如case语句)、条件运算符和过程赋值语句等控制结构,这些是实现复杂逻辑的关键。

在建模的更高级部分,教程涉及到了行为建模和数据流建模的具体实例,以及过程赋值语句和顺序语句块的使用,这些帮助理解如何用Verilog HDL描述复杂的系统行为。最后,教程还提到了一些其他相关主题,例如时延处理,并给出了习题以供实践,以及一个附录,列出了Verilog HDL的所有保留关键字。

这份教程为初学者提供了一个全面的Verilog HDL学习框架,通过学习,读者将能够理解和编写基本的Verilog HDL代码,为进行实际的硬件设计打下坚实的基础。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2008-09-02 上传

2014-06-12 上传

2020-09-02 上传

118 浏览量

2015-09-15 上传

元辰辰辰辰辰辰

- 粉丝: 54

- 资源: 76

最新资源

- FSM 设计指导-FPGA编程的重要方面

- FPGASOPC开发简明教程

- 高质量C、C++编程指南

- 新版设计模式手册[C#]

- 计算机控制技术试题1

- RHCE官方教材RH033/英文版

- 51单片机 传感器DS18B20

- Uml Managing Software Requirements

- XFire开发Web服务的简易之道

- arcgis二次开发学习资料PDF教程

- 电子技术课程设计(没有封面)

- Microsoft Windows Internals (原版PDF)

- Android 动画分析

- 51单片机学习--单片机的40个实验

- C、C++、Fortran混合编程研究

- 利用VC++实现局域网实时视频传输