1.BUFG

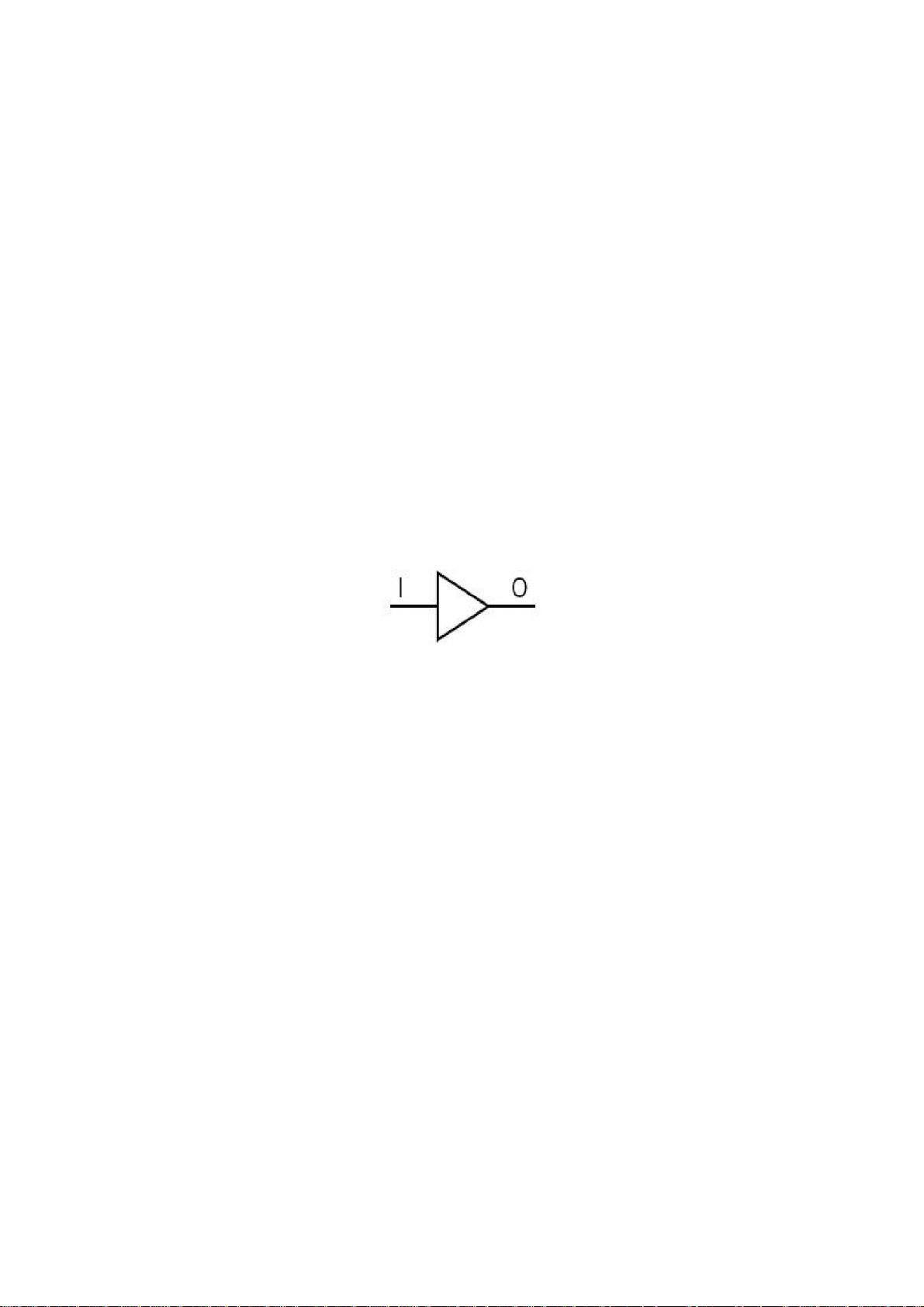

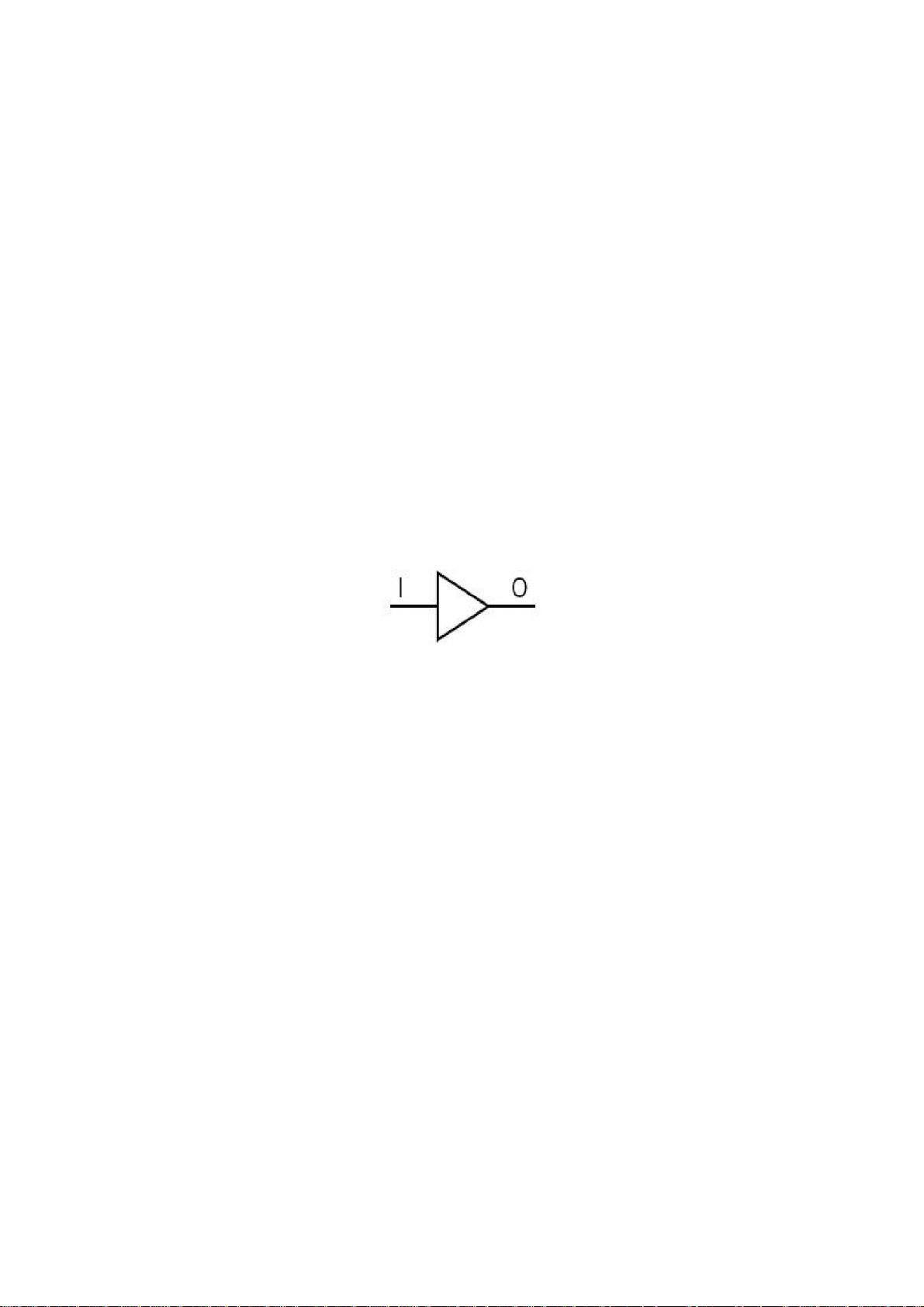

BUFG 是具有高扇出的全局时钟缓冲器,一般由综合器自动推断并使用,其

和同类原语的 RTL 结构如图 3-28 所示。全局时钟是具有高扇出驱动能力的

缓冲器,可以将信号连到时钟抖动可以忽略不计的全局时钟网络,BUFG 组

件还可应用于典型的高扇出信号和网络,如复位信号和时钟使能信号。如果

要对全局时钟实现 PLL 或 DCM 等时钟管理,则需要手动例化该缓冲器。其

例化的代码模板如下所示:

// BUFG: 全局时钟缓存(Global Clock Buffer),只能以内部信号驱动

// Xilinx HDL 库向导版本,ISE 9.1

BUFG BUFG_inst (

.O(O), //时钟缓存输出信号

.I(I) // /时钟缓存输入信号

);

// 结束 BUFG_ins 模块的例化过程

在综合结果分析中,其和同类原语的 RTL 结构如图 3-32 所示。

图 3-32 全局时钟原语的 RTL 级结构示意图

2. BUFMUX

BUFMUX 是全局时钟复用器,选择两个输入时钟 I0 或 I1 中的一个作为全局

时钟,其和同类原语 BUFMUX1 的 RTL 级结构如图 M 所示。当选择信号 S

为低时,选择 I0;否则输出 I1,其真值表如表 M 所示。BUFMUX 原语和

BUFMUX1 原语的功能一样,只是选择逻辑不同,对于 BUFMUX1,当选择

信号 S 为低时,选择 I1;否则输出 I0。

BUFMUX 原语的例化代码模板如下所示:

// BUFGMUX: 全局时钟的 2 到 1 复用器(Global Clock Buffer 2-to-1 MUX)

// 适用芯片:Virtex-II/II-Pro/4/5, Spartan-3/3E/3A

// Xilinx HDL 库向导版本,ISE 9.1

BUFGMUX BUFGMUX_inst (

.O(O), //时钟复用器的输出信号

.I0(I0), // 0 时钟输入信号

.I1(I1), //1 时钟输入信号

.S(S) // 时钟选择信号

);

// 结束 BUFGMUX_inst 模块的例化过程