i.MX 6Solo/6DualLite Applications Processors for Consumer Products, Rev. 2.1

20 Freescale Semiconductor

Modules List

3.1 Special Signal Considerations

Table 3 lists special signal considerations for the i.MX 6Solo/6DualLite processors. The signal names are

listed in alphabetical order.

The package contact assignments can be found in Section 6, “Package Information and Contact

Assignments.” Signal descriptions are provided in the i.MX 6Solo/6DualLite Reference Manual

(IMX6SDLRM).

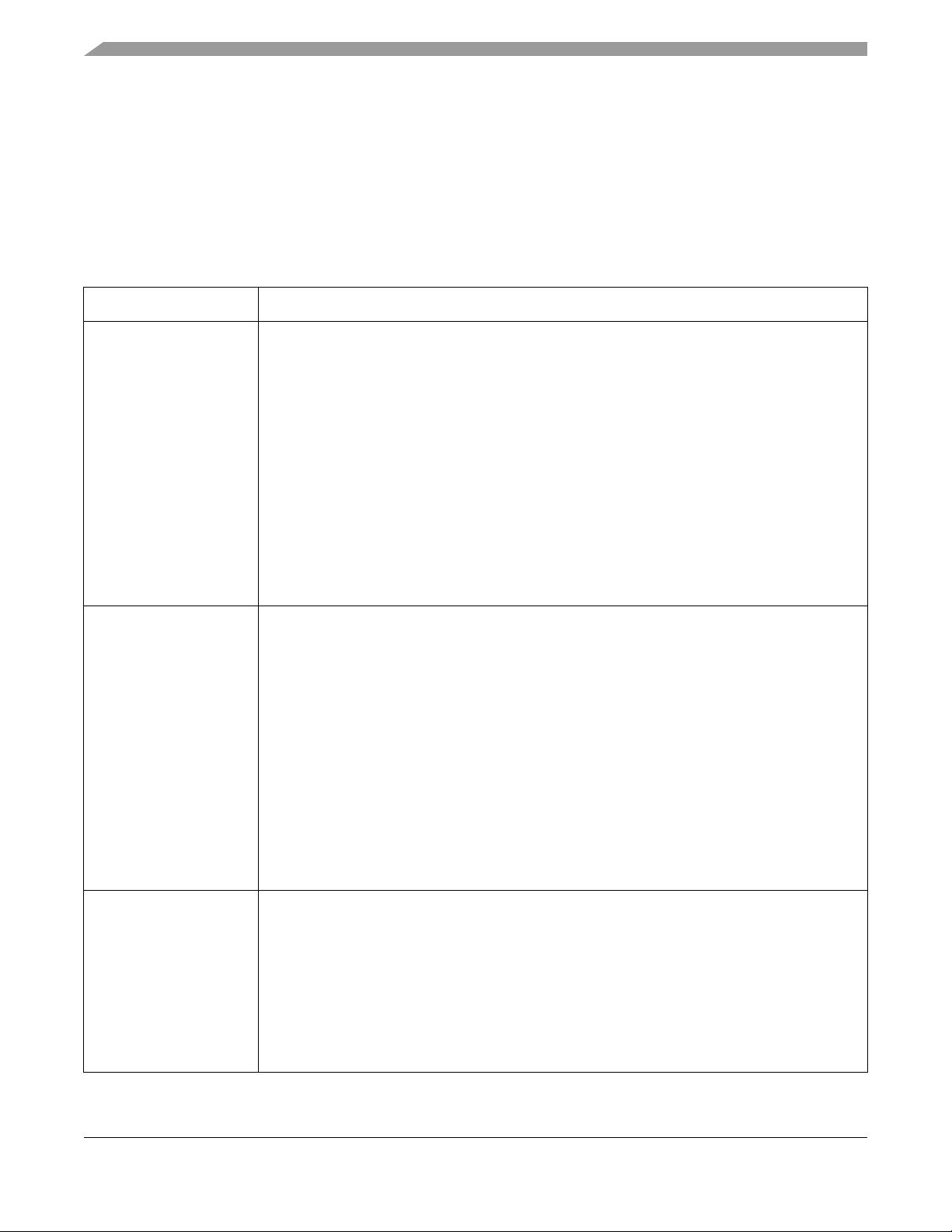

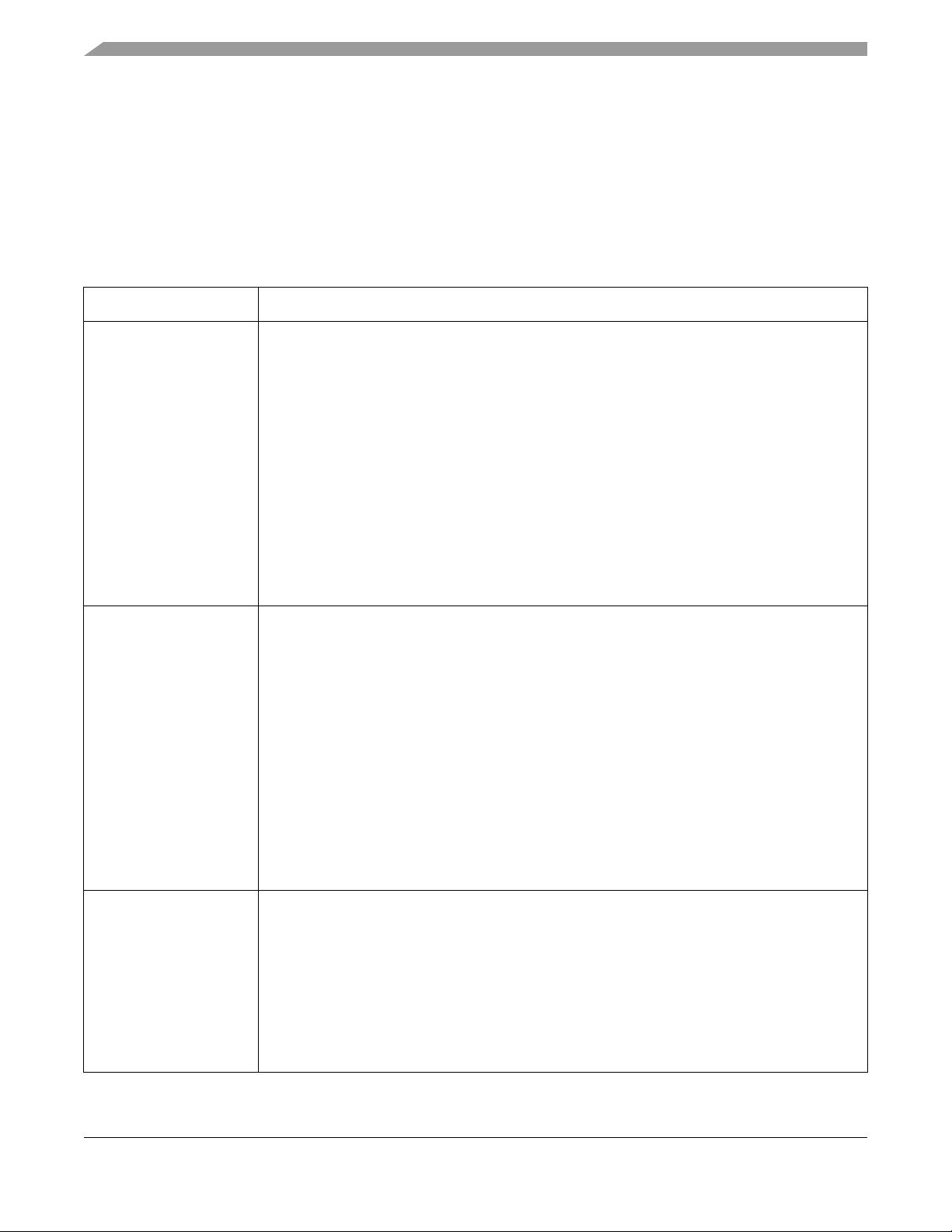

Table 3. Special Signal Considerations

Signal Name Remarks

CLK1_P/CLK1_N

CLK2_P/CLK2_N

Two general purpose differential high speed clock Input/outputs are provided.

Any or both of them could be used:

• To feed external reference clock to the PLLs and further to the modules inside SoC, for example

as alternate reference clock for PCIe, Video/Audio interfaces, etc.

• To output internal SoC clock to be used outside the SoC as either reference clock or as a

functional clock for peripherals, for example it could be used as an output of the PCIe master

clock (root complex use)

See the i.MX 6Solo/6DualLite reference manual for details on the respective clock trees.

The clock inputs/outputs are LVDS differential pairs compatible with TIA/EIA-644 standard, the

maximum frequency range supported is 0...600 MHz.

Alternatively one may use single ended signal to drive CLKx_P input. In this case corresponding

CLKx_N input should be tied to the constant voltage level equal 1/2 of the input signal swing.

Termination should be provided in case of high frequency signals.

See LVDS pad electrical specification for further details.

After initialization, the CLKx inputs/outputs could be disabled (if not used). If unused any or both of

the CLKx_N/P pairs may be left floating.

XTALOSC_RTC_XTALI/

RTC_XTALO

If the user wishes to configure XTALOSC_RTC_XTALI and RTC_XTALO as an RTC oscillator, a

32.768 kHz crystal, (100 k ESR, 10 pF load) should be connected between

XTALOSC_RTC_XTALI and RTC_XTALO. Keep in mind the capacitors implemented on either side

of the crystal are about twice the crystal load capacitor. To hit the exact oscillation frequency, the

board capacitors need to be reduced to account for board and chip parasitics. The integrated

oscillation amplifier is self biasing, but relatively weak. Care must be taken to limit parasitic leakage

from XTALOSC_RTC_XTALI and RTC_XTALO to either power or ground (>100 M). This will

debias the amplifier and cause a reduction of startup margin. Typically XTALOSC_RTC_XTALI and

RTC_XTALO should bias to approximately 0.5 V.

If it is desired to feed an external low frequency clock into XTALOSC_RTC_XTALI the RTC_XTALO

pin should be left floating or driven with a complimentary signal. The logic level of this forcing clock

should not exceed VDD_SNVS_CAP level and the frequency should be <100 kHz under typical

conditions.

In case when high accuracy real time clock are not required system may use internal low frequency

ring oscillator. It is recommended to connect XTALOSC_RTC_XTALI to GND and keep

RTC_XTALO floating.

XTALI/XTALO A 24.0 MHz crystal should be connected between XTALI and XTALO. level and the frequency

should be <32 MHz under typical conditions.

The crystal must be rated for a maximum drive level of 250 W. An ESR (equivalent series

resistance) of typical 80 is recommended. Freescale BSP (board support package) software

requires 24 MHz on XTALI/XTALO.

The crystal can be eliminated if an external 24 MHz oscillator is available in the system. In this

case, XTALI must be directly driven by the external oscillator and XTALO is floated. The XTALI

signal level must swing from ~0.8 x NVCC_PLL_OUT to ~0.2 V.

If this clock is used as a reference for USB and PCIe, then there are strict frequency tolerance and

jitter requirements. See OSC24M chapter and relevant interface specifications chapters for details.

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

信息提交成功

信息提交成功