基于VHDL和FPGA的模块化数字秒表设计

版权申诉

149 浏览量

更新于2024-06-25

收藏 346KB DOC 举报

本研究文档详细探讨了基于EDA(电子设计自动化)技术的数字秒表的设计过程。该设计采用VHDL(Verilog Hardware Description Language,VHDL硬件描述语言)作为硬件描述语言,并利用大规模可编程逻辑器件FPGA(Field-Programmable Gate Array)作为核心硬件平台。设计目标是创建一个功能强大、实时性强且具有高度可靠性的计时器。

设计流程分为五个主要部分:

1. **方案设计**:

- 绪论部分介绍了设计背景和目的,对数字秒表的需求进行了概述。

- 方案论证与选择环节,作者可能讨论了多种方案的比较,最终选择了基于EDA的方案,因其灵活性和效率。

- 数字秒表的性能指标,如精确度、速度和多路计时能力,是设计的关键考量因素。

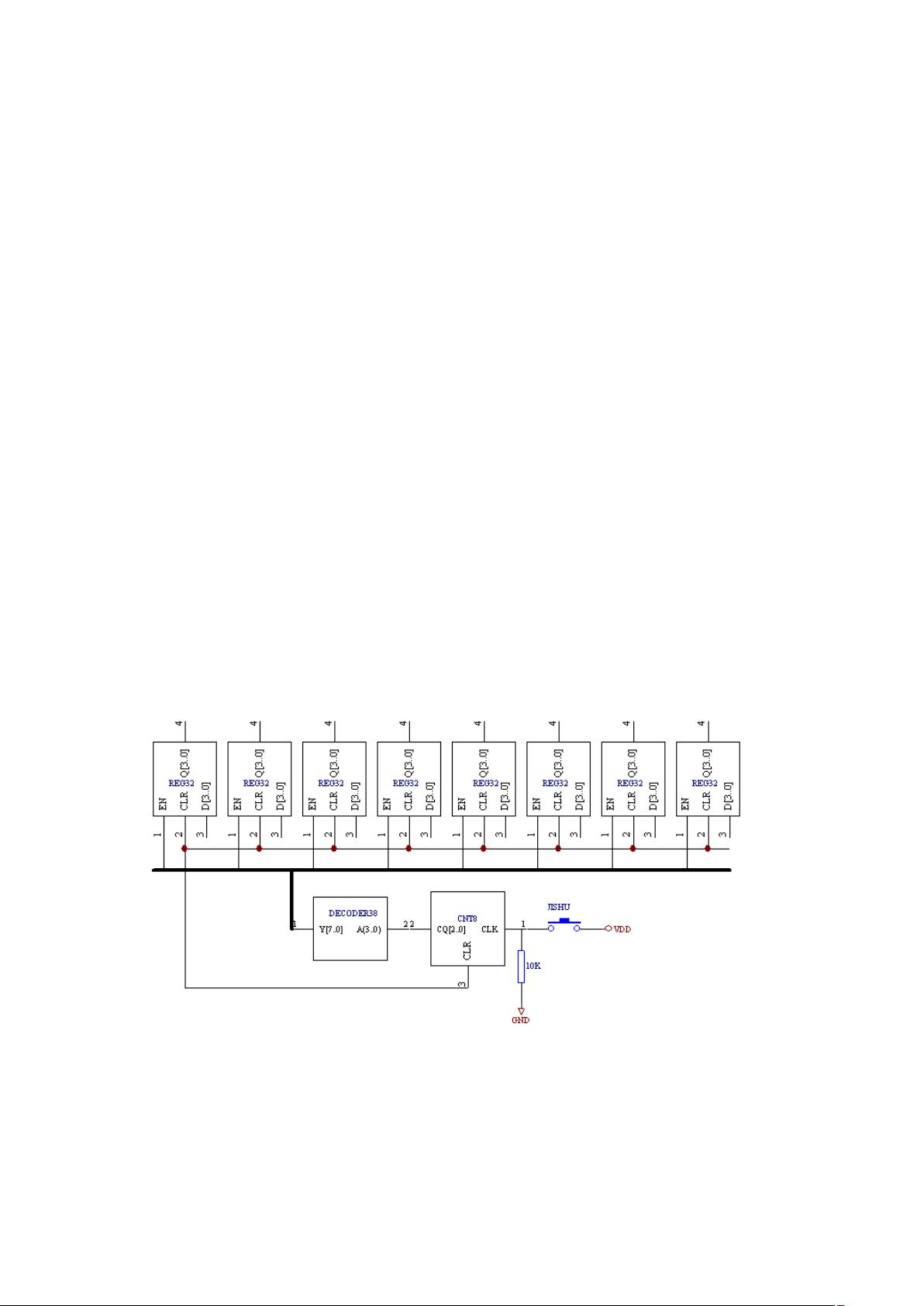

- 具体设计方案详细阐述了各个模块的功能,如计数模块负责时间计数,记忆模块用于存储历史数据,选择输出模块控制不同输出显示,而译码模块则负责信号转换。

2. **电路设计**:

- 计数模块是核心部分,实现基础的计时功能。

- 记忆模块确保数据的持久保留,可能包括定时器复位、暂停等功能。

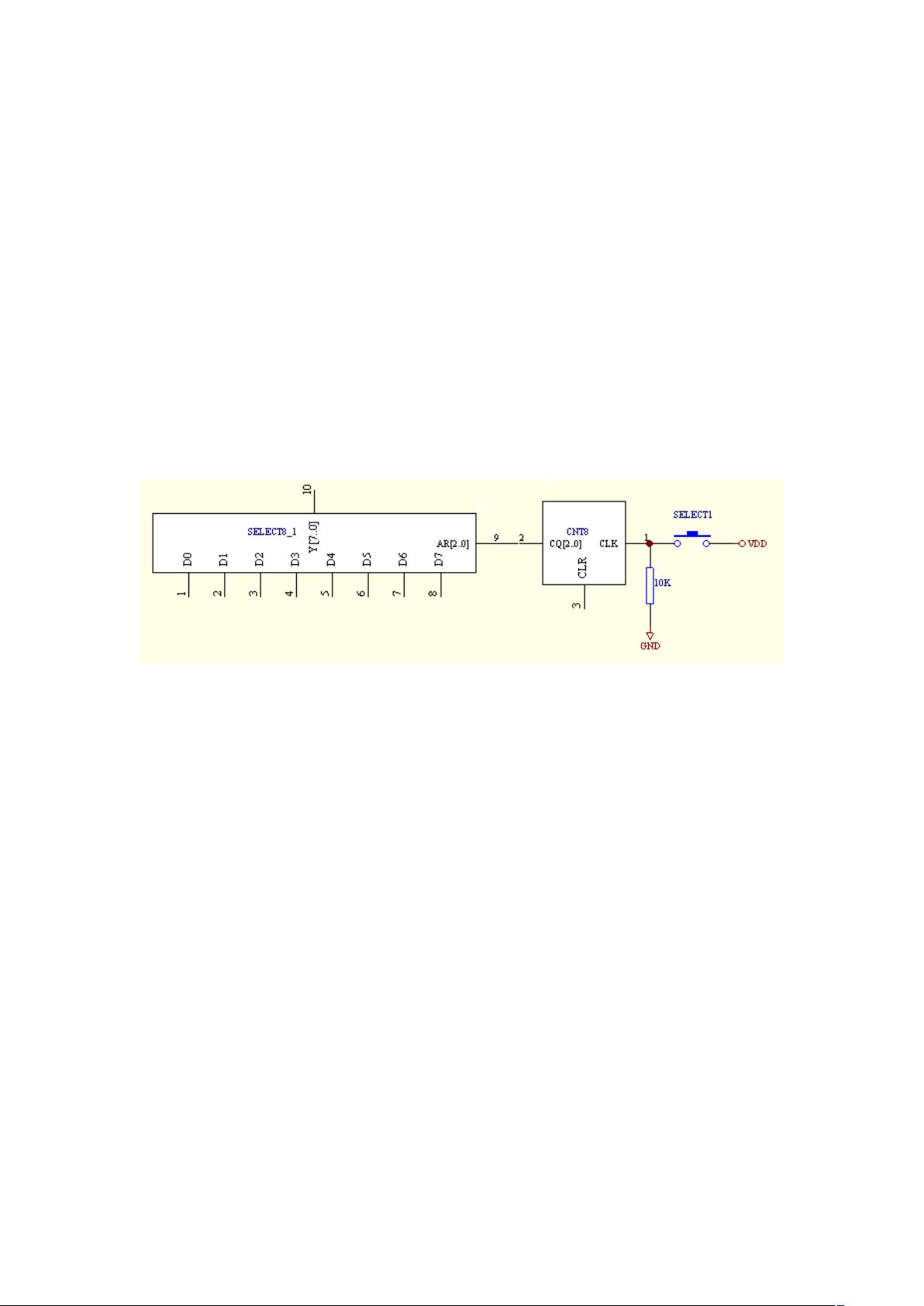

- 选择输出模块负责不同显示模式的选择,比如分钟、秒数或分秒组合。

- 译码模块将内部逻辑信号转化为用户可读的数字或字符。

- 整体电路设计展示了各个模块如何集成在一起,形成完整的秒表系统。

3. **软件设计**:

- 接口定义了系统与其他设备的通信方式,确保数据交换的准确性和兼容性。

- 主程序负责控制整个系统的运行流程。

- 各个模块的子程序,如计数、记忆和选择输出,都是模块化设计的体现,分别实现了各自功能。

- 使用QUARTUS II软件进行系统设计描述、划分、综合和验证,确保每个模块功能的正确性。

4. **仿真与实验**:

- QUARTUS II软件被用来进行软件仿真,测试各个模块和整个系统在理想条件下的行为。

- EDA实验箱提供了硬件环境,进行实际硬件级别的验证,确保设计的可实现性和性能。

5. **结论与优势**:

- 文献总结了设计过程中的关键步骤和技术,强调了使用FPGA和VHDL的优势,如实时编程、低功耗、多功能以及高精度和快速计时。

- 关键词如“数字秒表”、“EDA”、“FPGA”、“VHDL”和“QUARTUS II”突出了设计的核心技术。

通过这个设计,作者成功地将系统分解成模块,提高了设计的灵活性和复用性,同时通过严格的仿真和实验验证了系统的性能和可靠性,从而为实际应用提供了一个高效且可靠的数字秒表解决方案。

743 浏览量

195 浏览量

610 浏览量

188 浏览量

256 浏览量

172 浏览量

184 浏览量

127 浏览量

2023-06-20 上传

老帽爬新坡

- 粉丝: 98

- 资源: 2万+