DDR2/3高速PCB信号完整性设计:4层板挑战与优化策略

需积分: 32 179 浏览量

更新于2024-07-28

收藏 1002KB PDF 举报

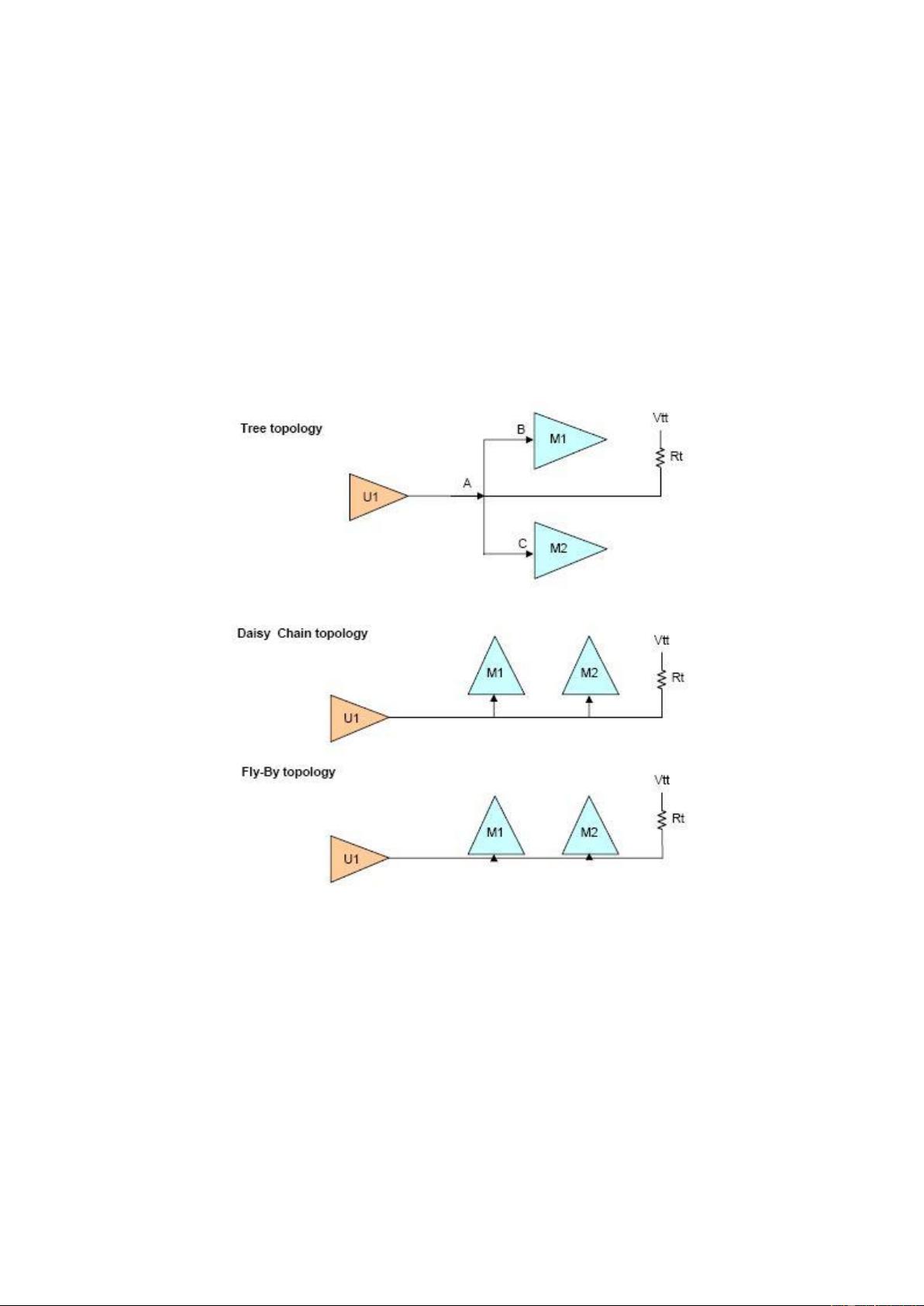

本文将深入探讨DDR2-800和DDR3高速内存技术在PCB(Printed Circuit Board,印刷电路板)信号完整性设计中的关键要素,特别是在设计4层或6层PCB时面临的挑战。随着DDR2的速度提升至800Mbps甚至更高,以及DDR3达到1600Mbps,信号传输的时序匹配、波形完整性、阻抗控制、等长规则、串扰抑制、电源管理以及信号时序控制变得尤为重要。

在设计过程中,PCB叠层(stackup)的选择直接影响信号传输的质量。在4层板中,信号线通常分布在顶层(TOP)、底层(BOTTOM)以及GND和VDD层,而6层板提供了更多的灵活性。叠层设计需确保电源平面(Power Plane)与地平面(Ground Plane)之间的距离优化,以提高电源完整性(PI)。

阻抗一致性是关键,单端信号需匹配50欧姆,而差分信号则需100欧姆终端匹配电阻。在DDR3设计中,ADDR/CMD/CNTRL信号线的终端匹配电阻范围在40到60欧姆,允许更灵活的调整,并可能根据SI仿真的结果调整到30到70欧姆。此外,所有匹配电阻需上拉到VTT,并保持恒定的阻值。

等长规则(Equal-Length Routing)在DDR2和DDR3中都至关重要,以减小延迟偏差并保持信号同步。在4层板中,设计者需巧妙利用空间,确保每个信号路径长度接近,同时处理好电源和地线的布局,以减少信号间的相互影响,如串扰。

电源完整性涉及电源线的布局,确保电压稳定和快速上升时间,这对高速数据传输至关重要。对于DDR3,电源平面和地平面的间距缩小有助于提高电源完整性,但同时也需考虑电源噪声的影响。

最后,现代EDA工具如Cadence ALLEGRO SI-230和Ansoft's HFSS在信号完整性设计中扮演着核心角色,它们能进行精确的计算和仿真,帮助工程师优化PCB设计以满足DDR2和DDR3的严苛技术要求。

DDR2-800和DDR3的PCB信号完整性设计是一门精细的艺术,需要综合考虑多种因素,包括但不限于PCB层数、叠层配置、阻抗控制、等长规则以及电源管理,以确保高速数据传输的稳定性和可靠性。随着技术的不断发展,设计者需不断学习和适应新的工具和技术,以应对不断提升的内存标准。

2023-07-07 上传

2024-11-05 上传

2024-10-26 上传

2024-11-05 上传

2024-10-26 上传

2024-10-26 上传

heyan504538

- 粉丝: 0

- 资源: 7

最新资源

- Raspberry Pi OpenCL驱动程序安装与QEMU仿真指南

- Apache RocketMQ Go客户端:全面支持与消息处理功能

- WStage平台:无线传感器网络阶段数据交互技术

- 基于Java SpringBoot和微信小程序的ssm智能仓储系统开发

- CorrectMe项目:自动更正与建议API的开发与应用

- IdeaBiz请求处理程序JAVA:自动化API调用与令牌管理

- 墨西哥面包店研讨会:介绍关键业绩指标(KPI)与评估标准

- 2014年Android音乐播放器源码学习分享

- CleverRecyclerView扩展库:滑动效果与特性增强

- 利用Python和SURF特征识别斑点猫图像

- Wurpr开源PHP MySQL包装器:安全易用且高效

- Scratch少儿编程:Kanon妹系闹钟音效素材包

- 食品分享社交应用的开发教程与功能介绍

- Cookies by lfj.io: 浏览数据智能管理与同步工具

- 掌握SSH框架与SpringMVC Hibernate集成教程

- C语言实现FFT算法及互相关性能优化指南